计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

项目一:实现一个简单的1到9的计数器。

项目分析:假设FPGA的晶振为50HZ,相当于1秒有50M次时钟周期,故计数一次的时间为1/50000000=20ns,若想计时1秒,故计数器要一直累加到50000000-1次,即可以达到想要的效果。

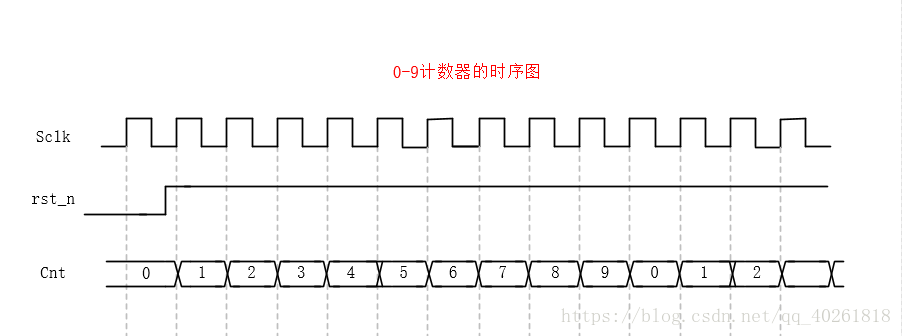

根据简单的时序图可以知道,若设计1到9的简单计数器,每当累加到9的时候要清0一次。故程序编写如下:

module jishuqi(

input wire sclk ,

input wire rst_n,

output reg[3:0] cnt

);

always@(posedge sclk)

begin

if(rst_n==1'b0)

cnt <= 1'b0 ;

else if(cnt == 9)

cnt <= 1'b0 ;

else

cnt <= cnt + 1'b1 ;

end

endmodule如想编写其他范围的计数器,只要在else if(cnt == n)更改n的值就可以编写使用!

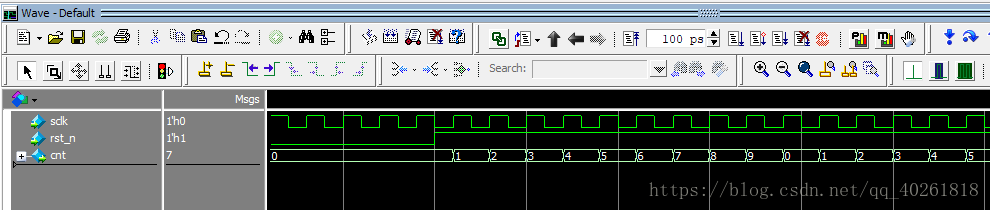

下面是modelsim仿真结果,方便大家能更好的理解:

项目二:用FPGA Verilog HDL 实现流水灯功能。

首先先讲解一下区分LED灯共阳极和共阴极:

共阴极公共端接阴极,高电平有效(灯亮),共阴极数码管内部发光二极管的阴极(负极)都联在一起,此数码管阴极(负极)在外部只有一个引脚。

共阳极公共端接阳极,低电平有效(灯亮), 共阳极数码管内部发光二极管的阳极(正极)都联在一起,此数码管阳极(正极)在外部只有一个引脚。

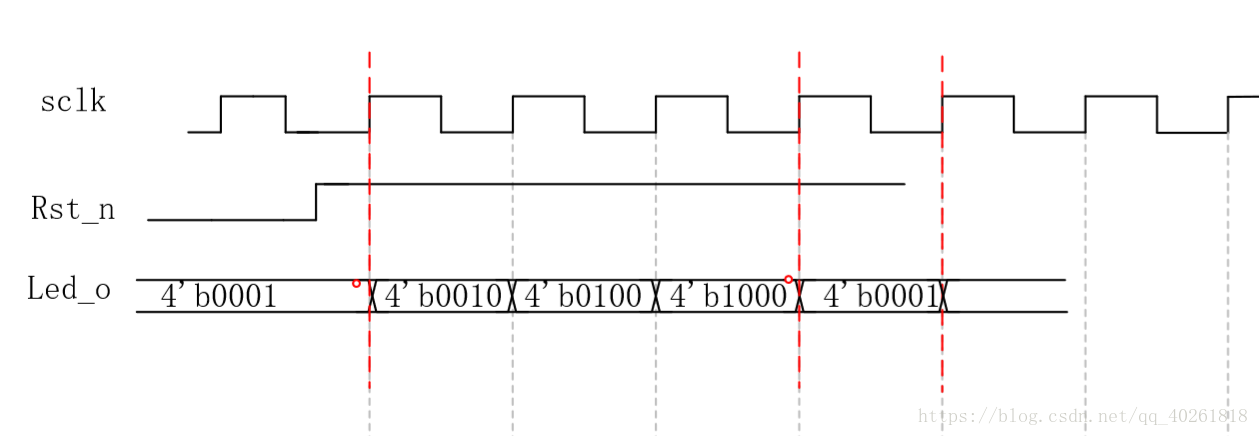

项目分析:首先定义4位宽的LED灯,查看FPGA电路原理图,确认LED是共阴极还是共阳极。本次设计是以共阴极,首先初始状态先让一个灯亮,故4个LED的逻辑为0001,我们想达到一个流水灯的功能故让最后一个灯向前每次位移1位,效果就是0010,0100,1000。当灯为1000时再位移一次就会变成10000,因为位宽是4位,所以会默认低4位0000(全灭)。所以当灯为1000时我们令它变成0001状态,到这一步很多人就会觉得流水灯应该可以呈现出来了,但是真正完成这一步是不够的,完成这一部最后的现象是4个LED灯全亮(可以自己尝试一下)。我们的人眼的频率大约是24HZ左右,因为是用的50HZ的FPGA板,相当于每次灯亮一次所用的时间只有20ns,故会产生余晖效应,看到的现象是全亮的现象。所以前面设计的项目一,计数器便发挥到了作用。我们可以令计数器计时到50000000-1次,相当于1秒,1秒位移1位。

根据分析的时序图可以知道,当LED为4‘b1000时,我们让它等于4‘b0001’’,故代码如下:

module water_led (

input wire sclk ,

input wire rst_n ,

output reg [3:0] led_o

);

reg [25:0] cnt ; //26位宽

//计时器模块

always@(posedge sclk or negedge rst_n)

begin

if(rst_n==1'b0)

cnt <= 1'b0 ;

else if(cnt == 50000000-1)

cnt <= 1'b0 ;

else

cnt <= cnt + 1'b1 ;

end

//流水灯模块

always@(posedge sclk or negedge rst_n)begin

if(rst_n == 1'b0 )

led_o <= 4'b0001 ;

else if (led == 4'b1000 && cnt == 50000000-1)

led_o <= 4'b0001 ;

else if (cnt == 50000000-1)

led_o <= led_o << 1'b1 ;

end

endmodule 下面有一个简单的编程方式,用位拼接的方式可以改写一下流水灯模块。

//流水灯模块

always@(posedge sclk or negedge rst_n)begin

if(rst_n == 1'b0 )

led_o <= 4'b0001 ;

else if (cnt == 50000000-1)

led_o<={ led_o[2:0],led_o[3] } ;

end

用位拼接进行循环位移。

循环右移:LED<={LED[0],LED[3:1]};

循环左移:LED<={LED[2:0],LED[3]};

举例:1000 0100 0010 0001 每次将前三位赋值到低位,将第四位赋值到高位。可以自行理解一下,动手画一下。

该项目只是为了让新手方便理解以及我的学弟学妹们方便学习,欢迎大家交流,未经允许,请勿盗用,谢谢!