New STM32 Learning 25- Introduction to USART Register

STM32–USART register introduction (F1)

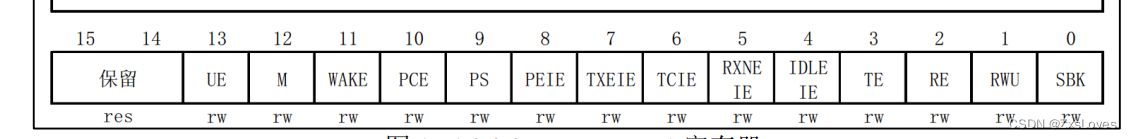

control register 1 (CR1)

bit 13: Enable USART UE

0: USART divider and outputs disabled

1: USART module enabled

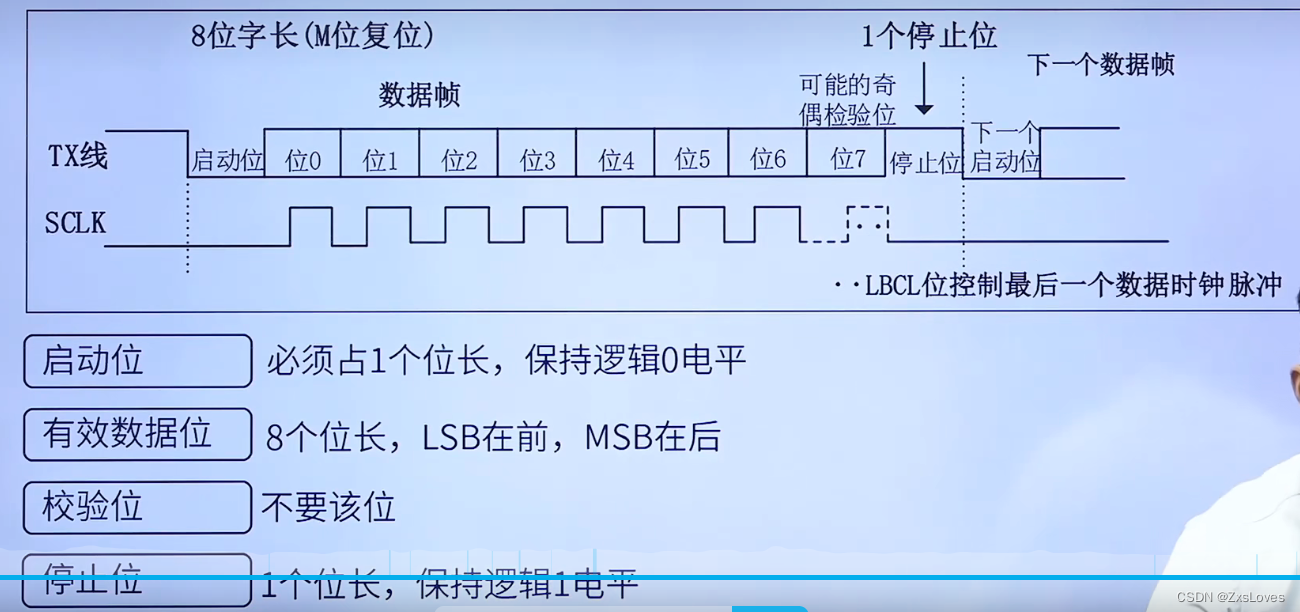

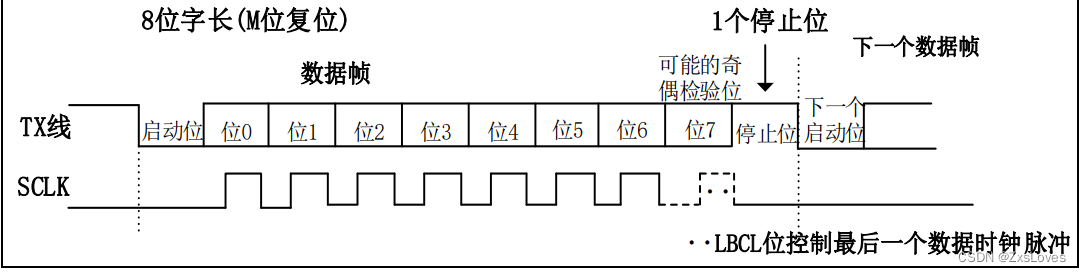

Bit 12: Configure 8 data bits M.

This bit defines the length of the data word, which is set and cleared by software.

0: One start bit, 8 data bits, n stop bits

1: One start bit, 9 data bits, n stop bits.

Generally speaking, 8 bits are used for effective data bits.

Bit 10: Disable check control PCE

0: Disable verification control

1: Enable verification control

Bit 5: RXNEIE enables receive buffer not empty interrupt

0: Disable interrupt generation

1: When ORE or RXNE of USART_SR is 1, USART interrupt is generated

Bit 3: TE enables transmission

0: Disables transmission

1: Enables transmission

Bit 2: Enable reception

0: Disable reception

1: Enable reception and start searching for the start bit on the RX pin

UE is the serial port enable bit. By setting this bit to 1, the serial port is enabled.

M is the word length. When this bit is 0, set the serial port to 8 words plus n stop bits. The number of stop bits (n) is determined according to the [13:12] bit setting of USART_CR2. The default is 0.

PCE

is the verification enable bit, which is set to 0 to disable verification, otherwise it is enabled.

PS is the parity bit selection, set to 0 for even parity,

otherwise odd parity. TXIE is the transmit buffer empty interrupt enable bit. Set this bit to 1. When the TXE bit in USART_SR is

1, a serial port interrupt will be generated.

TCIE is the transmission completion interrupt enable bit. Set this bit to 1. When the TC bit in USART_SR is 1, a serial port interrupt will be generated. RXNEIE is the receive buffer non-empty interrupt enable. Set this bit to 1. When the

ORE or RXNE bit in USART_SR is 1, a serial port interrupt will be generated. TE is the transmission enable bit. When set to 1,

the transmission function of the serial port will be enabled. RE is the receive enable bit, and its usage is the same as TE. ,

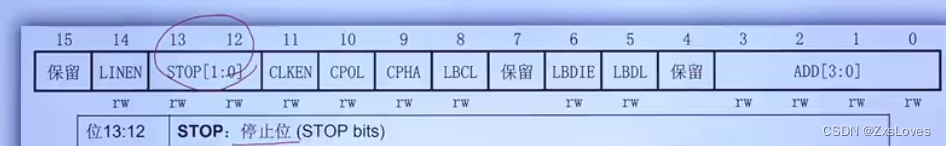

For another control register 2 CR2,

we only use bit 13. 12

bits 13:12

is the STOP stop bit.

Use these two bits to set the number of stop bits.

00: 1 stop bit

01: 0.5 stop bits

10: 2 stops Bit

11: 1.5 stop bits.

The configuration that needs to be completed for this register is: Configure 1 stop bit.

Note: UART4 and UART5 cannot use 0.5 stop bits and 1.5 stop bits.

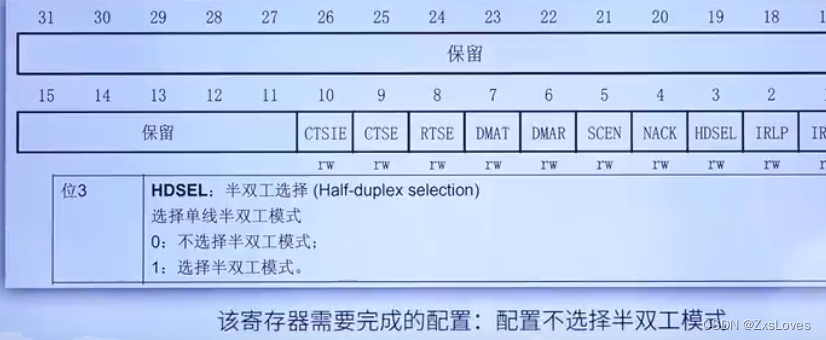

Control register CR3

we only use its bit 3.

We select half-duplex for the HDSEL configuration. Select

0: Do not select half-duplex mode.

1: Select half-duplex mode.

There are 9 bits here.

We follow the arrangement of CR1 above. If CR1 indicates 8 Then we just use [7;0]

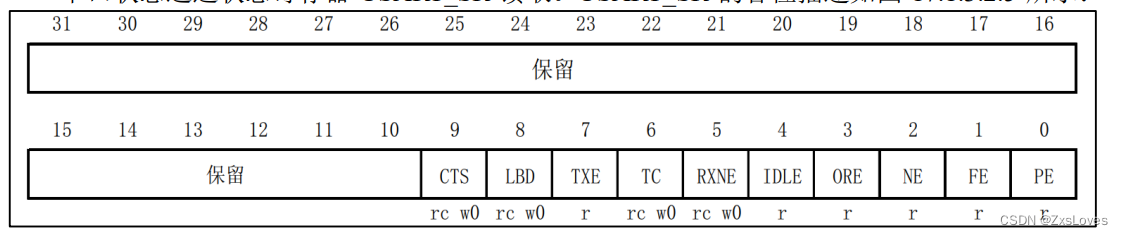

Status register SR

bit 5: RXNE (read data register is not empty)

When this bit is set to 1, it indicates that data has been received and can be read out. What we have to do at this time is to read USART_DR as soon as possible. By reading USART_DR, we can clear this bit, or we can write 0 to this bit to clear it directly.

In layman's terms, when this bit is 1, it means that the read data register is not empty, that is, there is something on the DR. We can read it out quickly. 0: The data has not been

received.

1: The data has been received and can be read out.

Bit 6: TC (transmission completed)

When this bit is set, it indicates that the data in USART_DR has been sent. If the interrupt for this bit is set, an interrupt will be generated. There are also two ways to clear this bit:

1) Read USART_SR and write USART_DR.

2) Write 0 directly to this bit

0: The sending is not completed yet

1: The sending is completed

According to the TC bit, we can know whether data can be sent.

According to the RXNE bit, we can know whether data has been received.