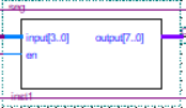

3)seg部分

library ieee;

use ieee.std_logic_1164.all;

entity seg is

port(input:in std_logic_vector(3 downto 0);

en:in std_logic;

output:out std_logic_vector(7 downto 0));

end seg;

architecture ru of seg is

begin

process(input,en)

begin

if en='1' then

if input="0000" then

output<="11111100";

elsif input="0001" then

output<="01100000";

elsif input="0010" then

output<="11011010";

elsif input="0011" then

output<="11110010";

elsif input="0100" then

output<="01100110";

elsif input="0101" then

output<="10110110";

elsif input="0110" then

output<="10111110";

elsif input="0111" then

output<="11100000";

elsif input="1000" then

output<="11111110";

elsif input="1001" then

output<="11110110";

elsif input="1010" then

output<="11101110";

elsif input="1011" then

output<="00111110";

elsif input="1100" then

output<="10011100";

elsif input="1101" then

output<="01111010";

elsif input="1110" then

output<="10011110";

elsif input="1111" then

output<="10001110";

end if;

else output<="00000010";

end if;

end process;

end ru;

接口设计:

input:输入数据

en:使能输入

output:输出数据

功能实现:

在显示模块中,通过输入数据,产生相应的段选信号。

结论:正确,信号结果正确。