2019年3月6日

活动:总线实验

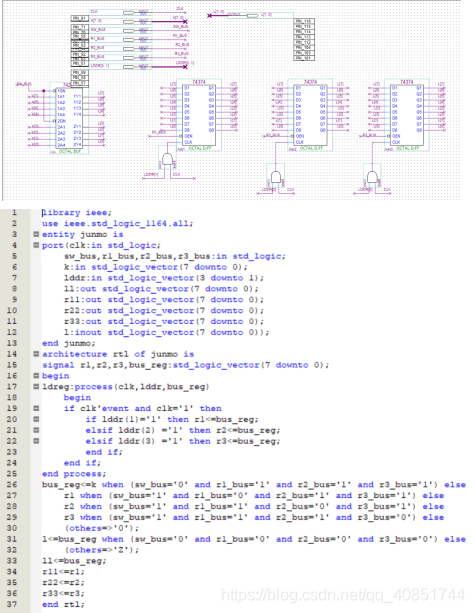

解释:3月5日时我同时写了VHDL和dbf文件两种格式,发现通过vhdl可以很轻松的实现总线要求的所有操作,同时可以很轻松的完成实验要求的r1和r2寄存器的交换操作,但是。在通过dbf格式实现总线实验的时候出了一些状况,不知道为什么我和我的组员的现象不一致,他没有le~result这个输出而我有,而且我的总线怎么也没有输出,不知道为什么。推测是因为对三态门那个芯片不是很熟悉的原因,还需要后续跟进进行改进。于3月6日全部完成,包括vhdl和图,也实现了r1和r2元素的交换,现在正在思考如何能在电路板上进行实现。于3月7日实现了所有的alu运算器的实验,即两个vhdl文件,也得到了正确的结果,同时学会了如何设置针脚以及如何将文件下载到板子上并在板子上运行文件。

题目:4.1.6思考题

解题方法:

1)只是用一条传输线,在传输线上按顺序传送信息的所有二进制位的脉冲信号,每次一位。

2)74374相当于一个八位寄存器,可以在控制信号的控制下输出(低电平有效)和输入(高电平有效)数据,并实现存储;74244相当于一个八位三态门,可以在控制信号(低电平有效)的控制下选择的通过数据

3)bidir端口可以实现双向输入,即既可以在仿真波形中看到l总线上的结果,也可以通过端口向总线输入数据

4)粗线比细线在画图上粗的多,粗线可以连接传输多位数据,细线只能传输一位数据。总线的命名方式为x[n…m],支线的命名方式为x[n]…x[m]

5)r3的输出没有接入总线l中,所以没法接触r3实现数据暂存。也就没有办法实现r1寄存器和r2寄存器的数据交换

6)通过inout设置端口来实现双向输入输出

7)可以将when语句修改成if else语句来实现,如:else bus_Reg<=”ZZZZZZZZ”

8)可以通过if和elsif语句实现多路分支,分别对应不同的情况执行不同的语句来实现多路选择的效果

9)在声明中间变量的时候在变量类型后面通过“=”进行赋值即可

题目:思考如何构造总线电路

解题方法:

通过粗线作为总线连接多个寄存器,并将总线引出接到bidir端口来观察总线值以及输入数据。

题目:分析图4-1-5与exp_bus.vhd设计的总线电路缓冲结构不同之处?并进一步分析lpm_bustri

解题方法:

图4-1-5没有将寄存器r3接入总线中,仅仅可以输出但不可以将r3的值返回总线,vhd可以。

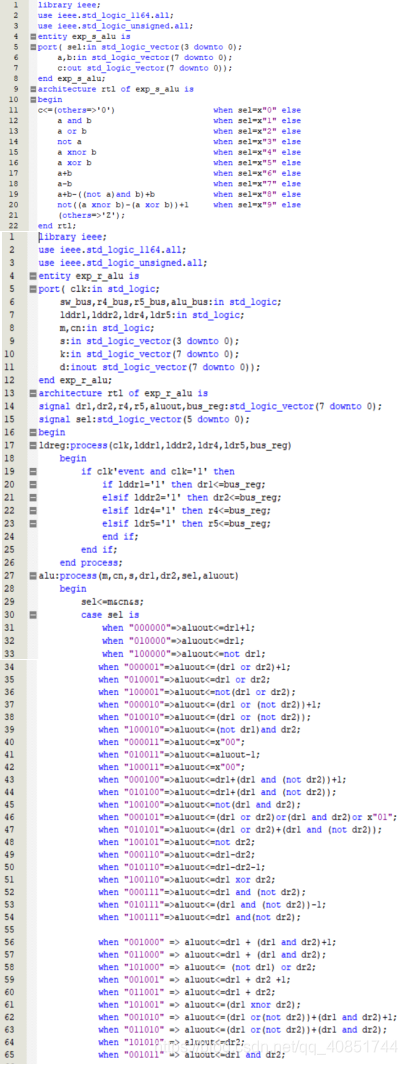

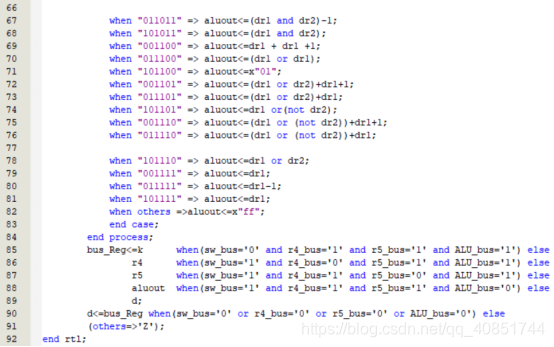

题目:4.2.6思考题

解题方法:

1)通过m,cn,s控制信号控制来输出到总线,如想要展示DR1的值,需要将m,cn,s设置为101111既可以在总线上输出

2)DR1和DR2存储的是最初的原始数据,如果将中间结果继续存到DR1或DR2中,那么在后续想要调用最初的原始数据将会无法调用。

3)通过符号位的0和1来表示正数和负数

4)+表示逻辑加法运算,加表示算数加法运算

5)用于连接数据,如a=“01”,b=“10”,那么c=a&b的结果就是“0110”

6)为了使用+、-等运算符来简化代码

7)通过x”0”来表示,如x“0”即表示十六进制里面的0

题目:试述实验8位运算器如何实现复合运算?

解题方法:

通过DR1和DR2暂存器来存储中间结果,使用多个时钟周期来实现复杂的复合运算。

结论:即便是在简单的实验,也不应该掉以轻心,避免在细节的方面出错;即便是再复杂的实验,也不应该畏惧,只要把问题列明白,再一个一个解决,就会发现其实很简单。

计算机系统实验:总线实验

猜你喜欢

转载自blog.csdn.net/qq_40851744/article/details/104820588

今日推荐

周排行