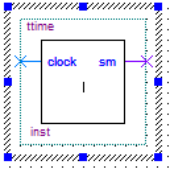

9)ttime部分

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity ttime is

port(clock:in std_logic;

sm:out std_logic

);

end ttime;

architecture st of ttime is

signal s:std_logic:='0';

constant clk:time:=2 ns;

begin

process(clock,s)

begin

if (falling_edge(clock)) then--rising_edge(clock)

--wait for clk/2;

if (s='0') then

s<='1';

elsif (s='1') then

s<='0';

end if;

end if;

end process;

sm<=s;

end st;

接口设计:

Clock:时钟信号

sm:指令输出

功能实现:

通过外部给定的clock信号,生成整个cpu的sm使能信号,并传递给各个部件。

仿真验证:

与cpu在同一文件中,与cpu同仿真。