目录

ARM Cortex M3 处理器

ARM Cortex-M3处理器基于ARM7

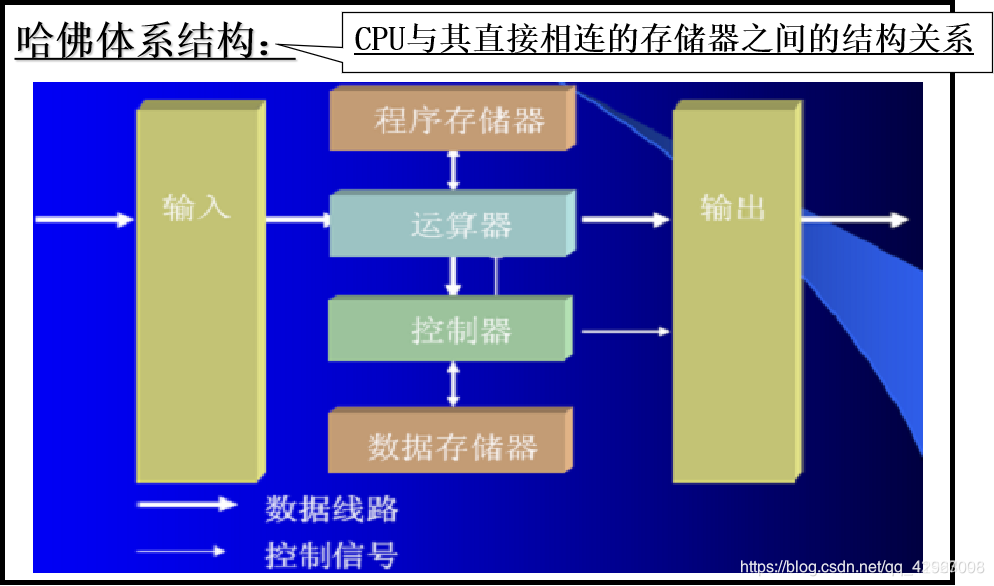

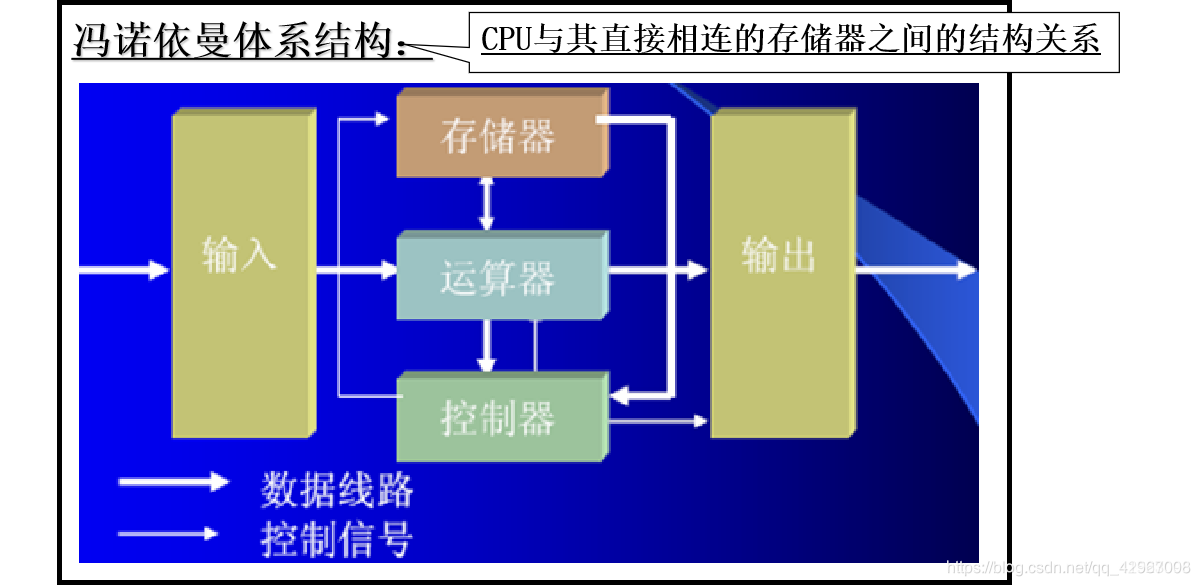

基于哈佛体系结构的32位ARMv7处理器

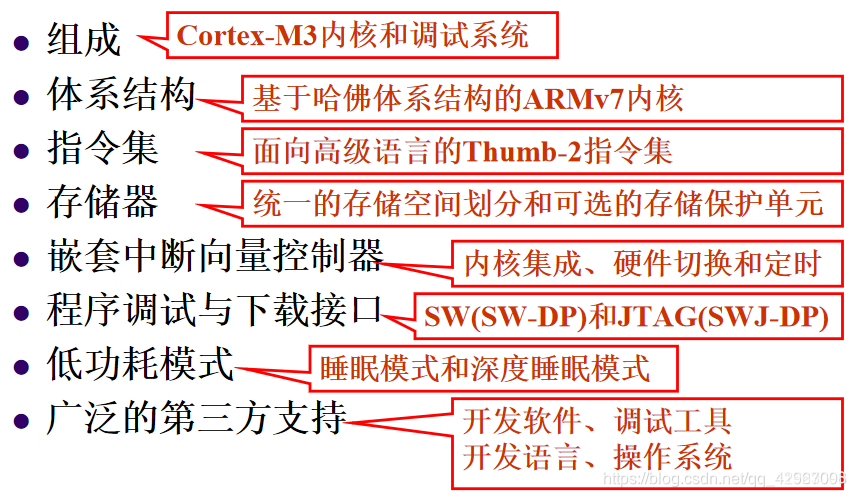

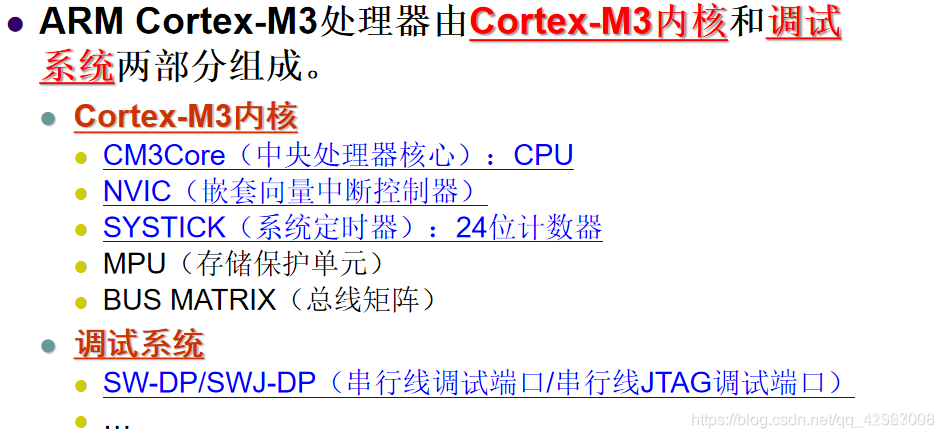

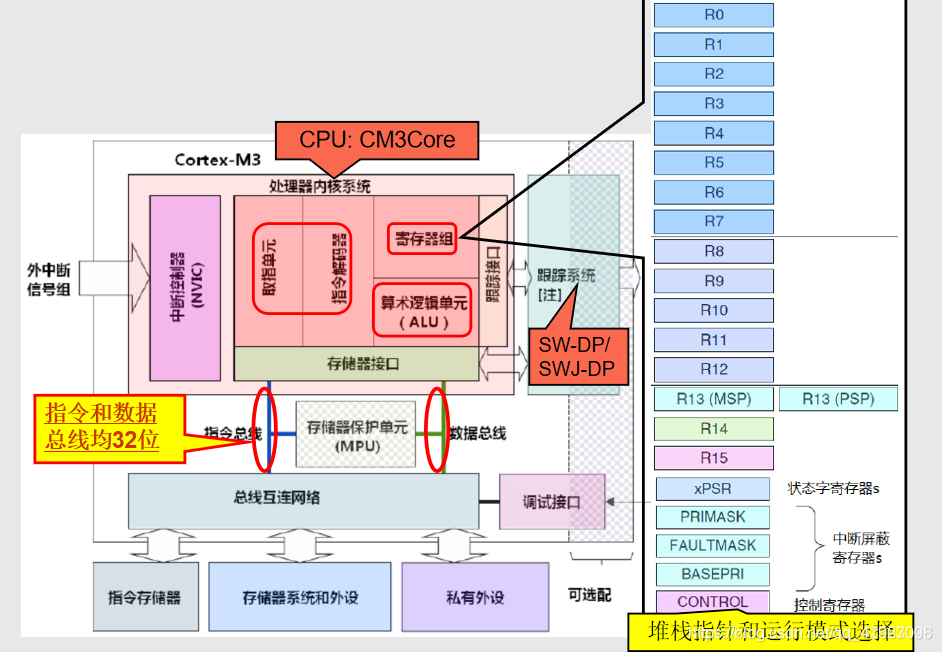

ARM Cortex-M3处理器组成

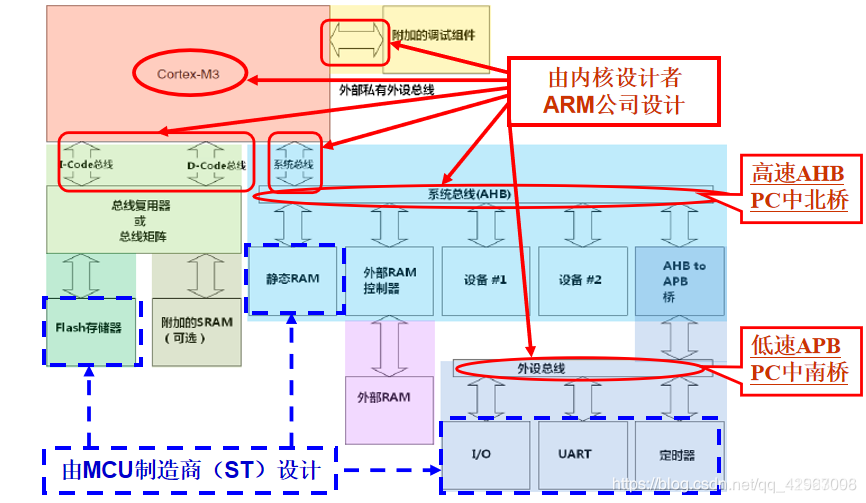

ARM Cortex-M3处理器结构

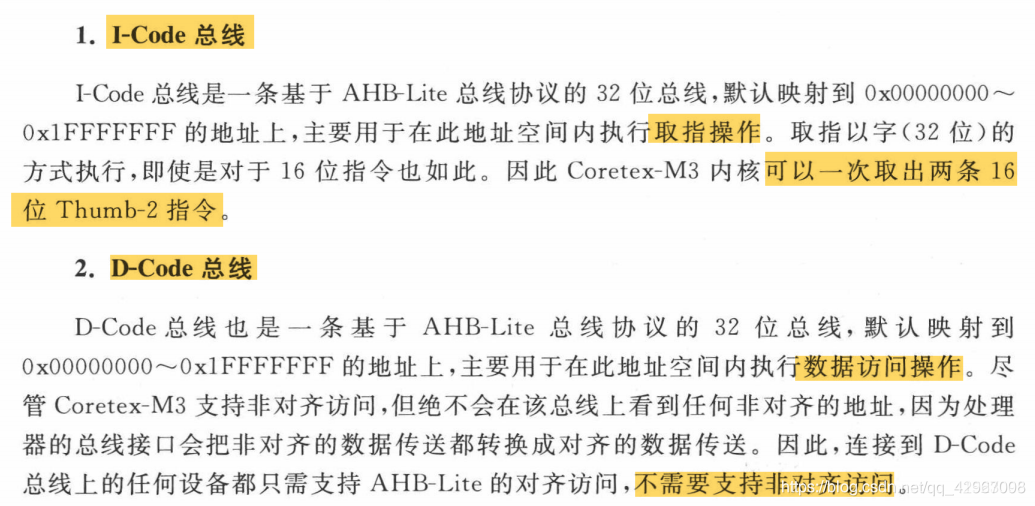

Cortex M3的总线接口

指令和数据总线均32位

Cortex M3的调试系统

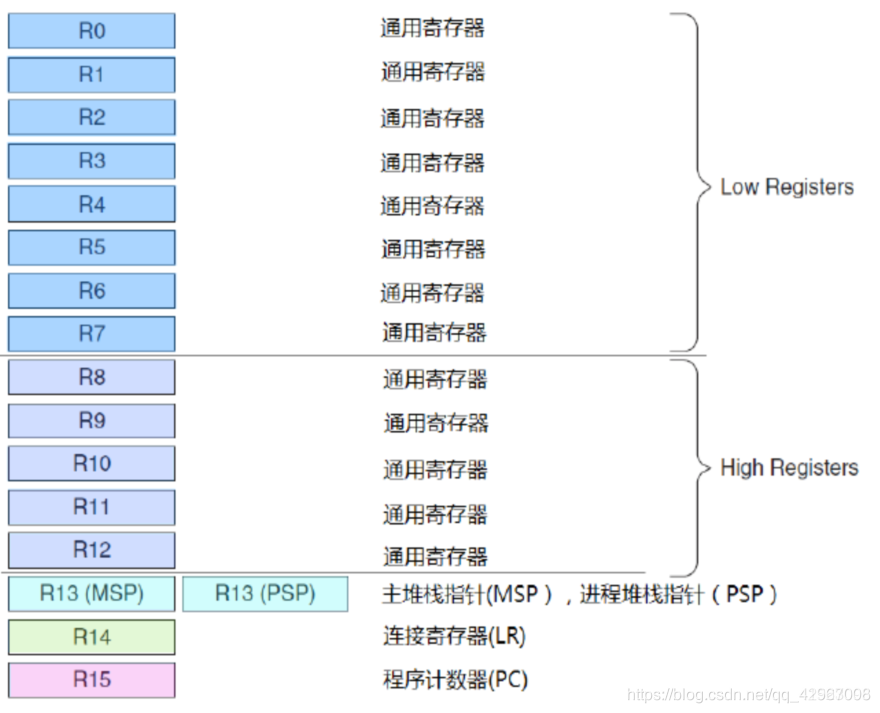

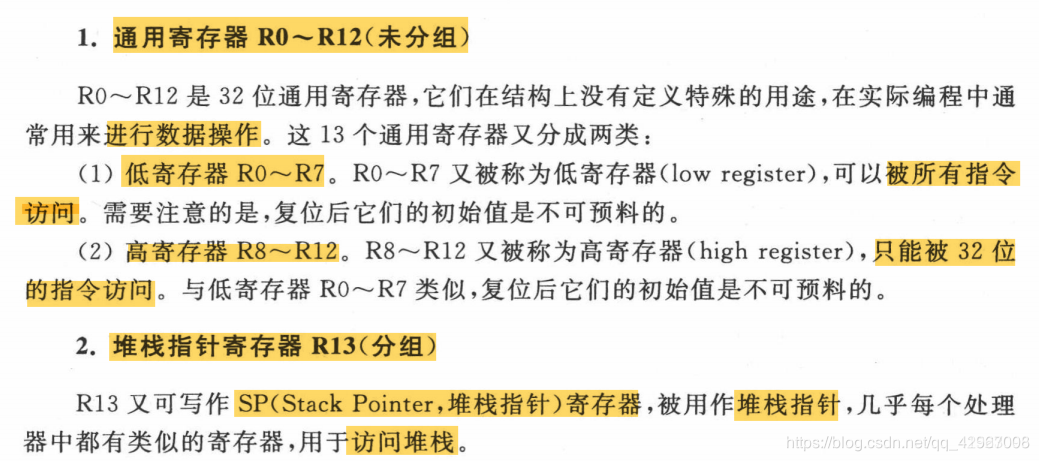

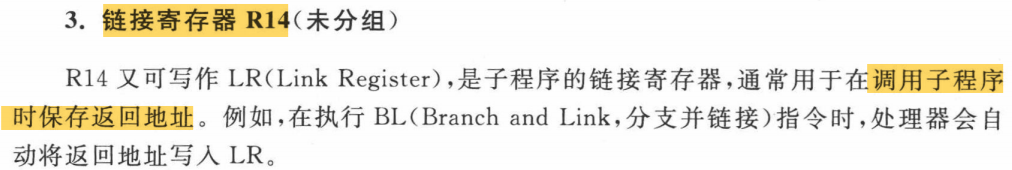

Cortex M3的寄存器及其作用

16个寄存器,分别作用如下:

另外CPSR SPSR ,CPSR:程序状态寄存器,SPSR:程序状态保存寄存器 SPSR用于保存CPSR的状态,主要用于中断.

通过读CPSR可以获得当前处理器的工作状态。读SPSR寄存器可以获得进入异常前的处理器状态。

Cortex M3的工作状态、特权分级及操作模式

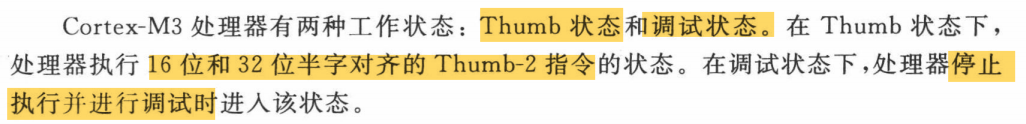

工作状态

特权级别

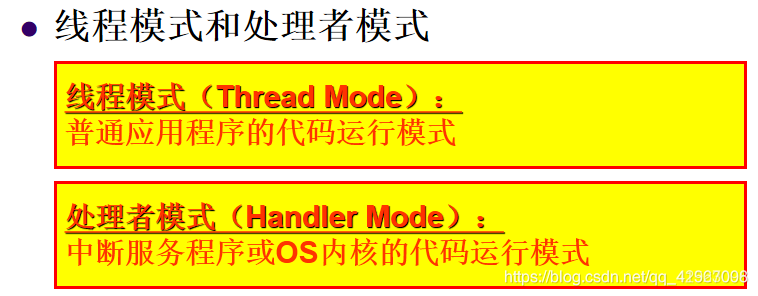

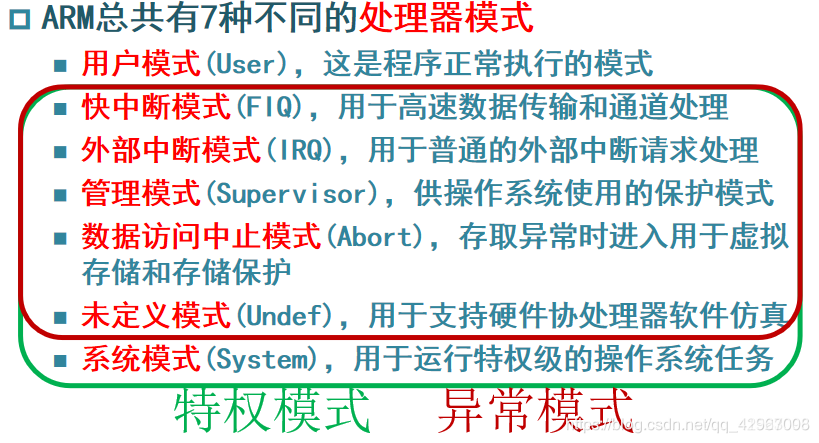

操作模式

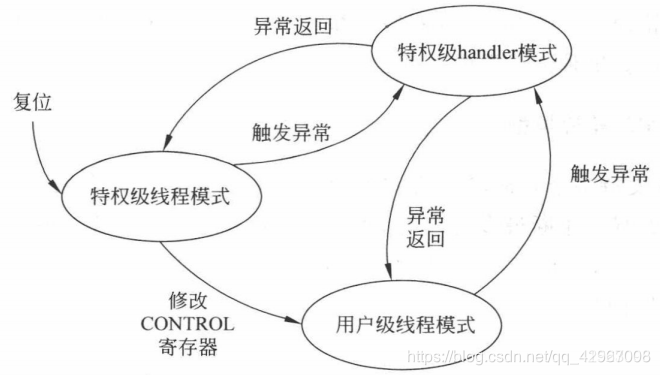

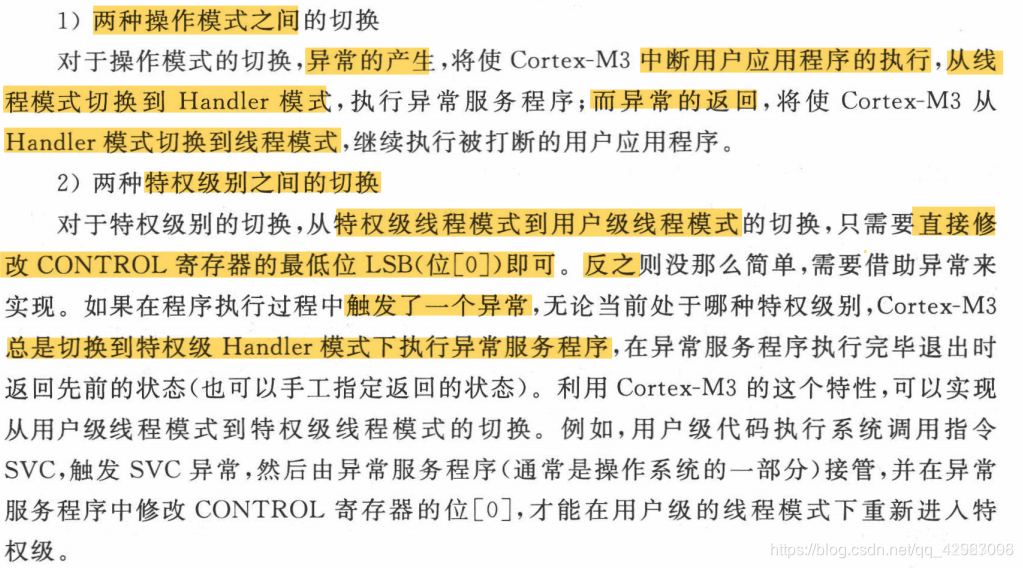

操作模式和特权级间的的相互转换

Cortex M3的中断与异常的处理过程

ARM Cortex-M3处理器支持 —— 11种系统异常(内部) ——240种外部中断

CM3内核所有中断机制都由嵌套向量中断控制器NVIC实现

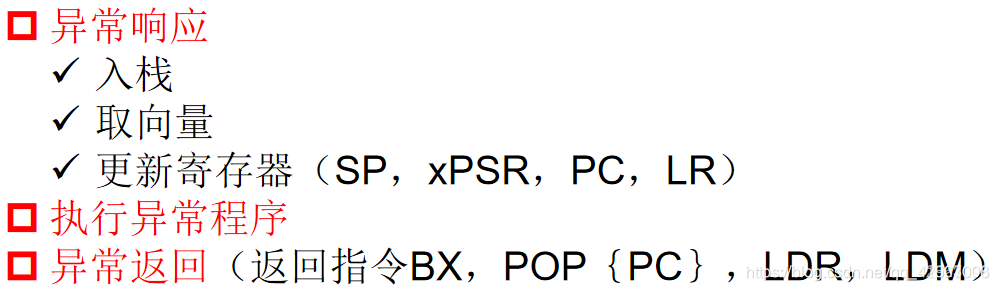

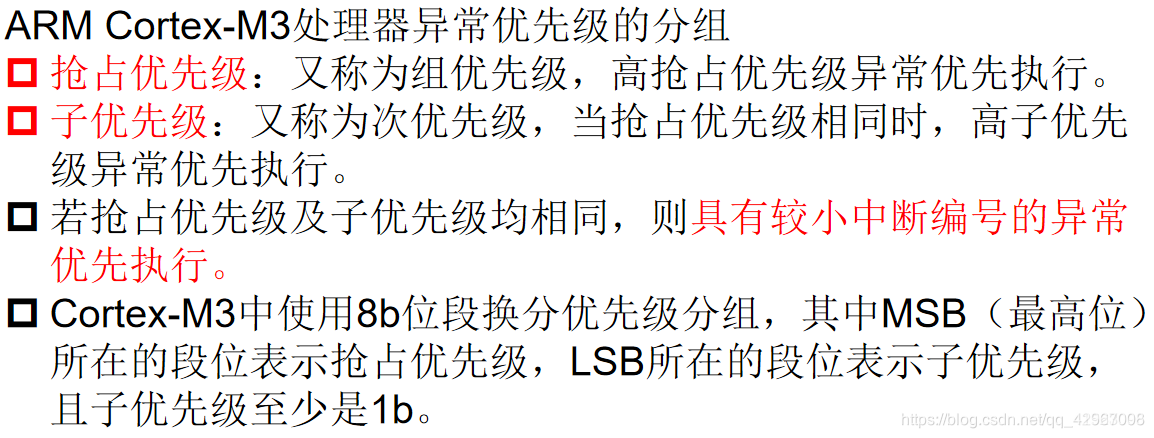

ARM Cortex-M3处理器异常处理过程

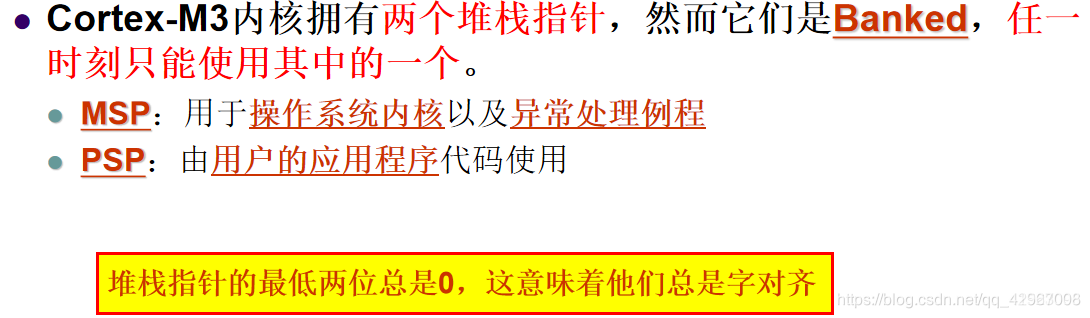

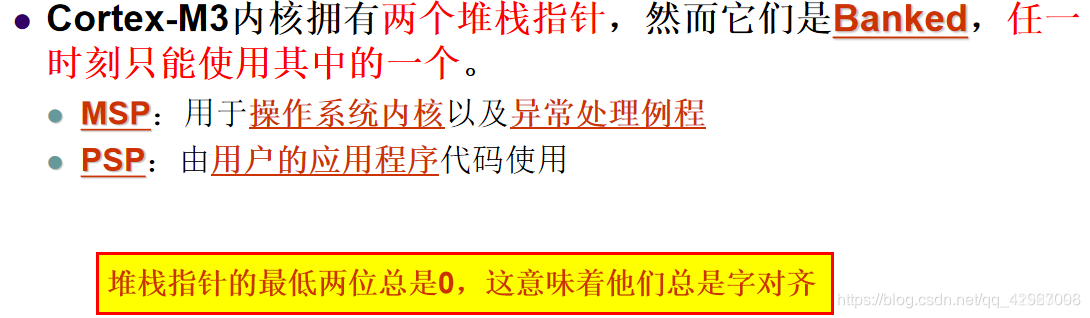

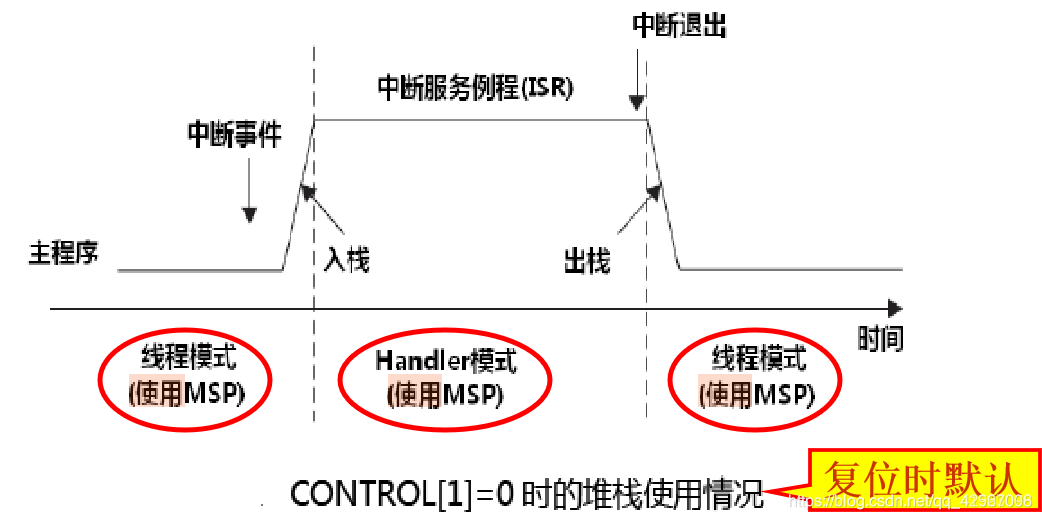

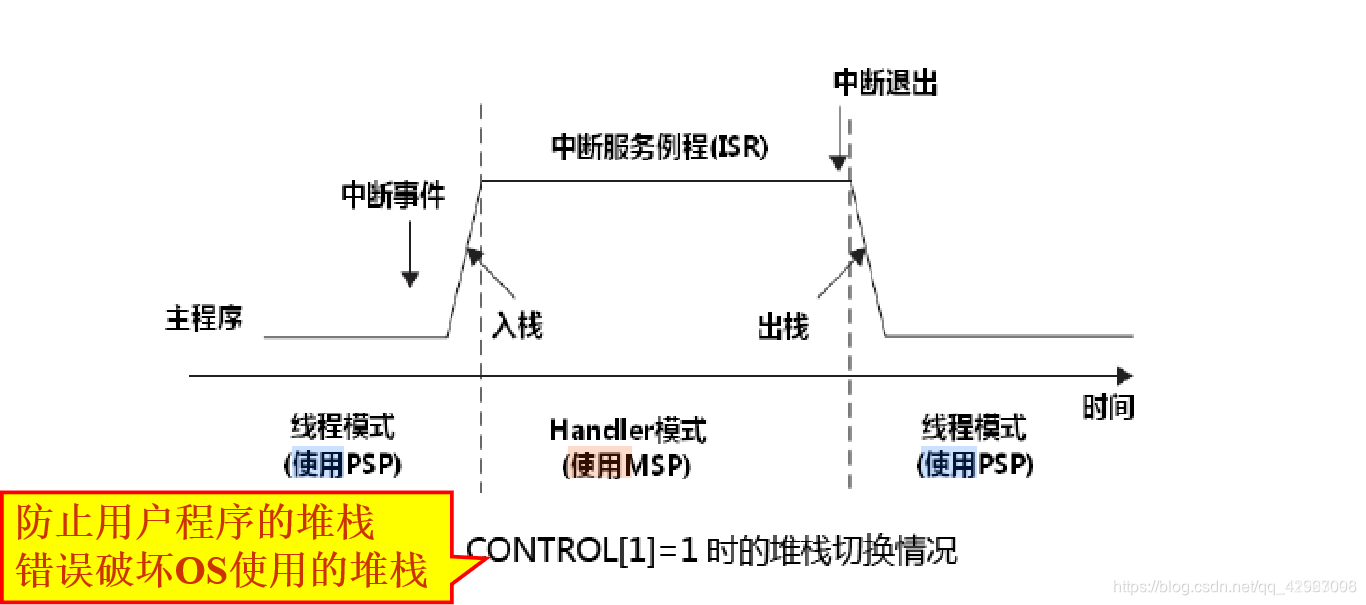

Cortex M3的双堆栈及其作用

CM3的堆栈是满递减栈,数据进栈指令由PUSH指令完成,数据出栈指令由POP指令完成

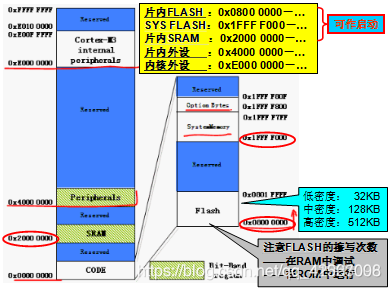

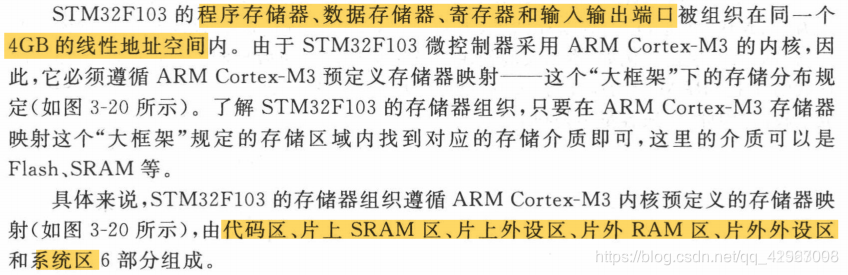

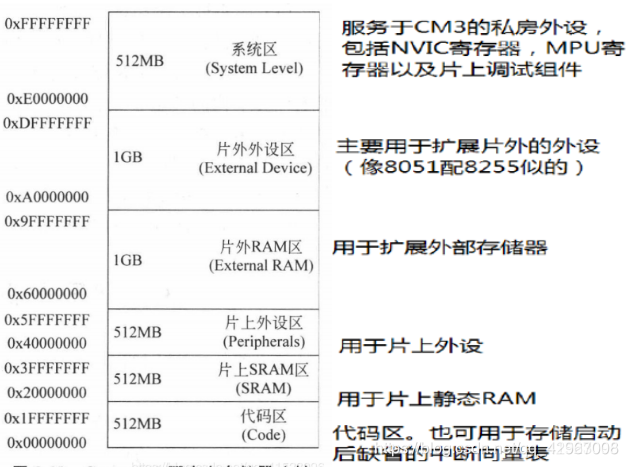

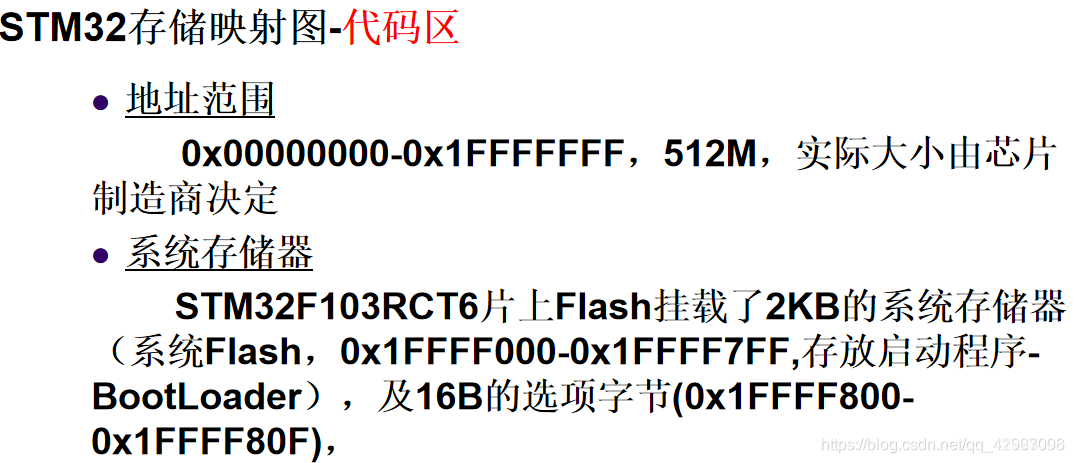

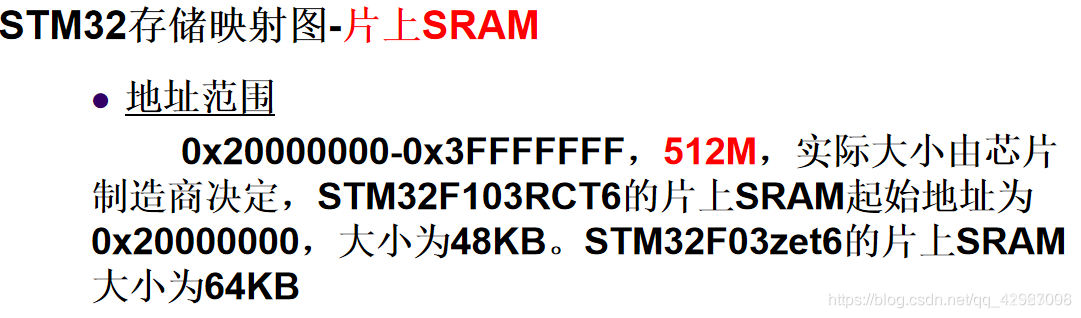

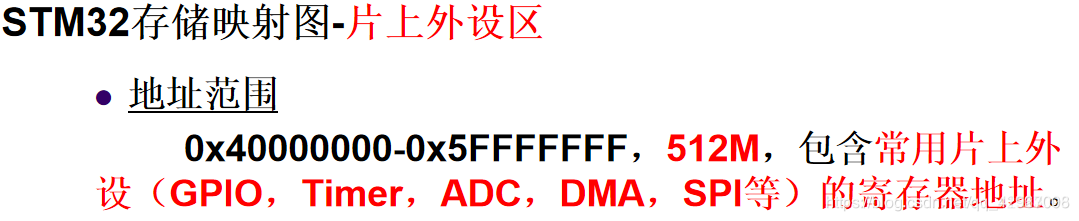

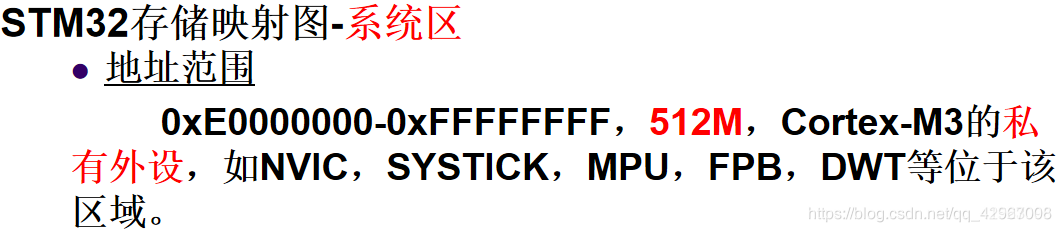

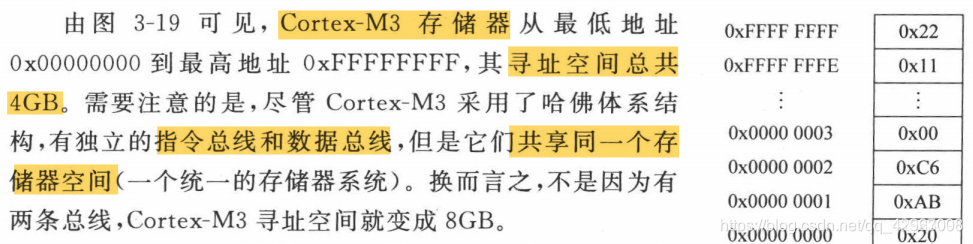

Cortex M3的存储映射

存储映射

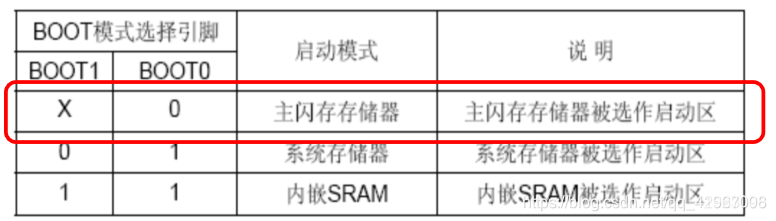

启动模式

STM32F103微控制器根据BOOT模式引脚的选择,将每个启动模式下的物理存储区域映射到存储块0(启动存储区),启动延迟后,CPU从启动存储器的0x00000004指示的地址开始执行代码。

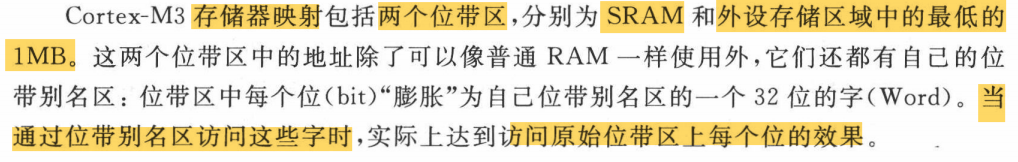

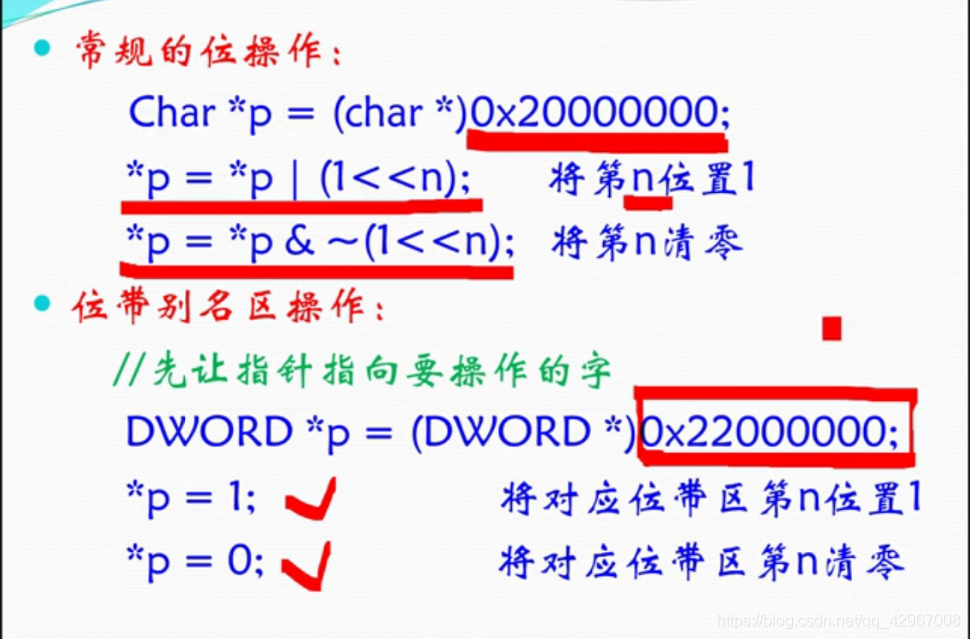

位带操作的作用,存储格式

位带操作

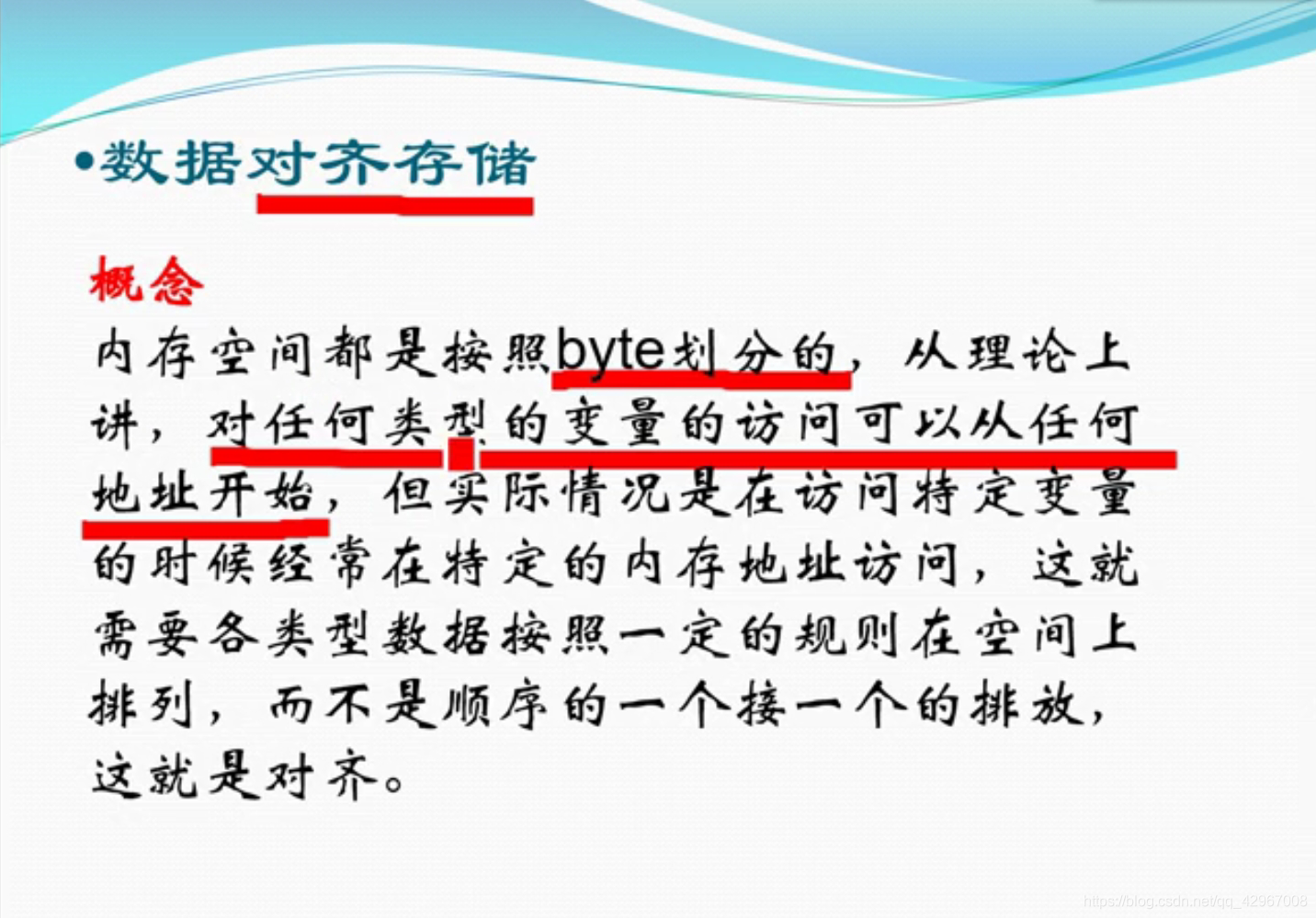

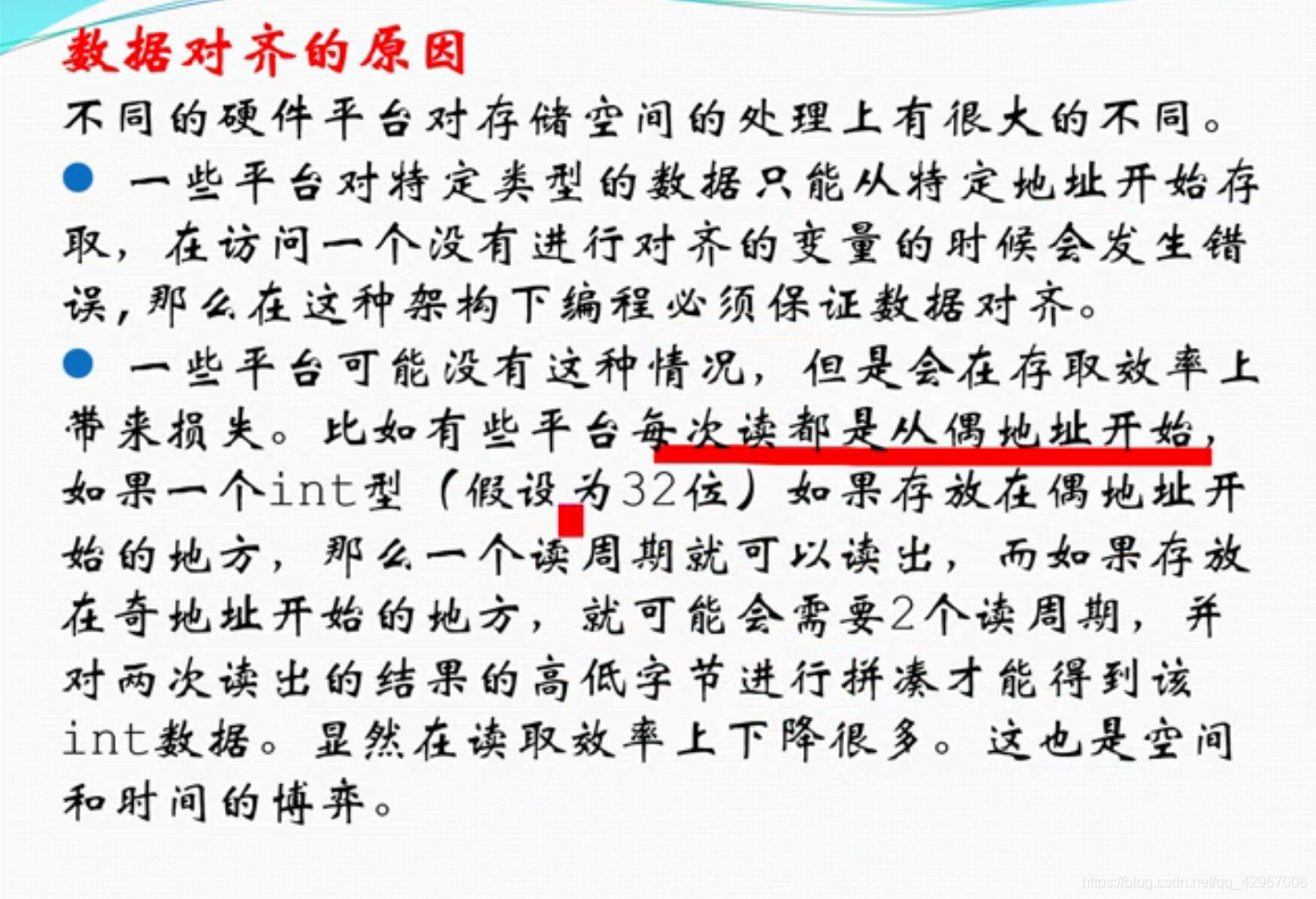

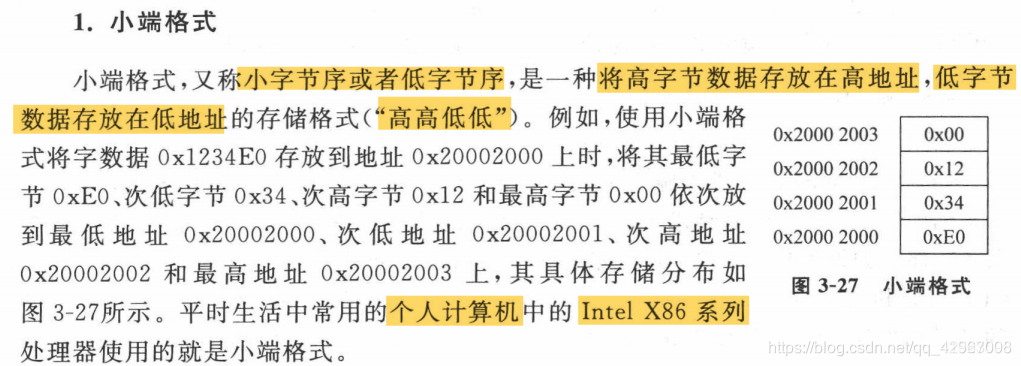

存储器格式(大小端格式)

![[图片]](https://img-blog.csdnimg.cn/20200310144610961.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzQyOTY3MDA4,size_16,color_FFFFFF,t_70)

低功耗模式

小结