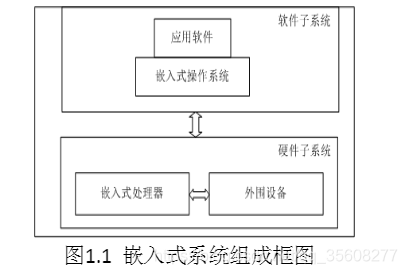

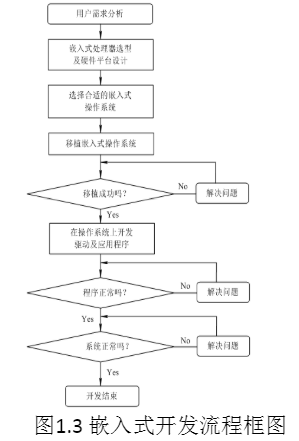

1嵌入式系统组成

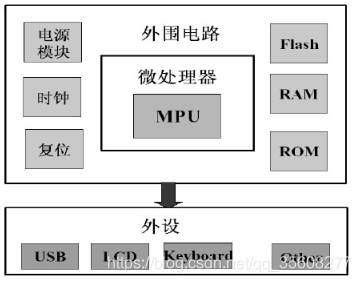

1.1 硬件子系统

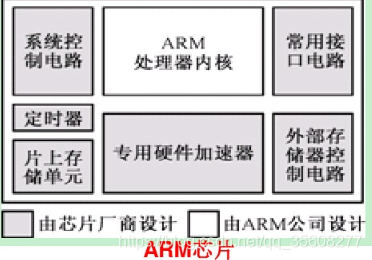

(1)嵌入式处理器

是系统的核心部件。代表ARM处理器,如图; MIPS PowerPC MC68000

(2) 外设

存储 SRAM RAM Flash

通信 RS232 SPI 以太网

显示 LCD

调试等

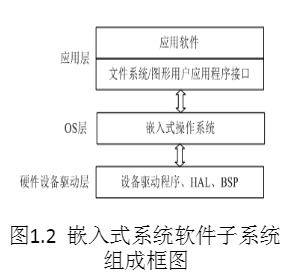

1.2 软件子系统

2 嵌入式处理器

2.1 基本结构

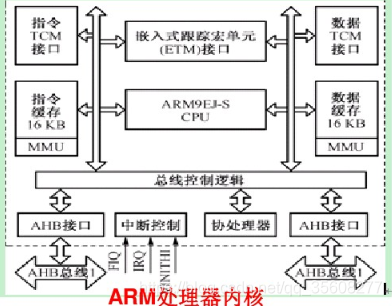

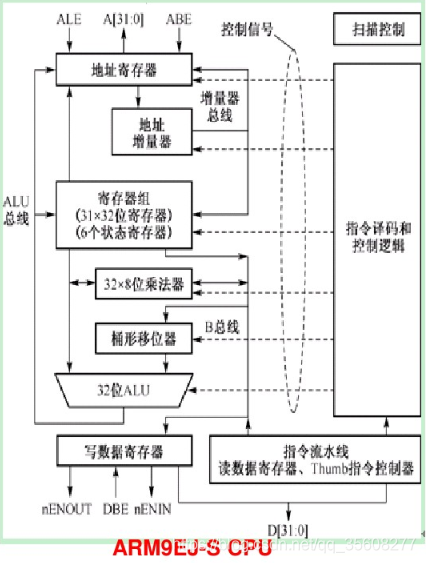

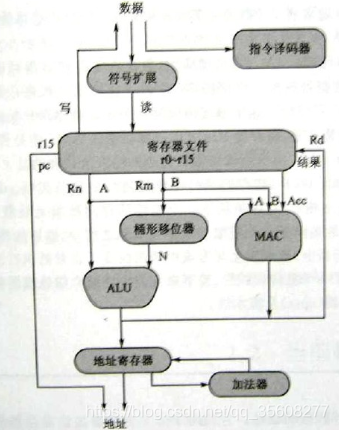

内核数据流

·

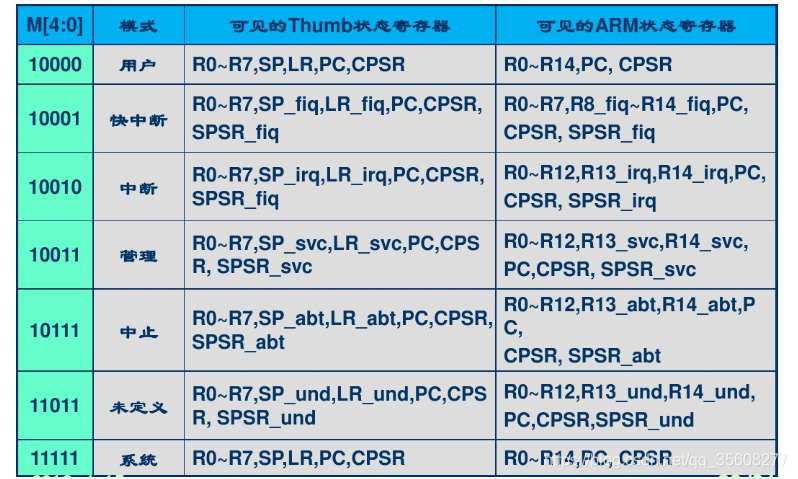

reg :37个寄存器按其在用户编程中的功能划分,

-

31个通用32位寄存器(包括程序计数器(PC指针))

-

6个32bits状态寄存器(用以标识CPU的工作状态及程序的运行状态)

共有37个寄存器。这6个状态寄存器在ARM公司文件中其名称分别为:

CPSR(Current Program State Register)、

SPSR_svc、

SPSR_abt、

SPSR_und、

SPSR_irq、

SPSR_fig。

32×32位桶形移位寄存器,左移/右移n位、环移n位和算术右移n位等都可以一次完成,可以有效的减少移位的延迟时间。

高速乘法器

算数逻辑单元ALU: 数值计算和逻辑计算,由两个操作数锁存器、加法器、逻辑功能、结果及零检测逻辑构成。

控制单元 :PC程序计数器(记录指令在内存中位置) IR指令寄存器

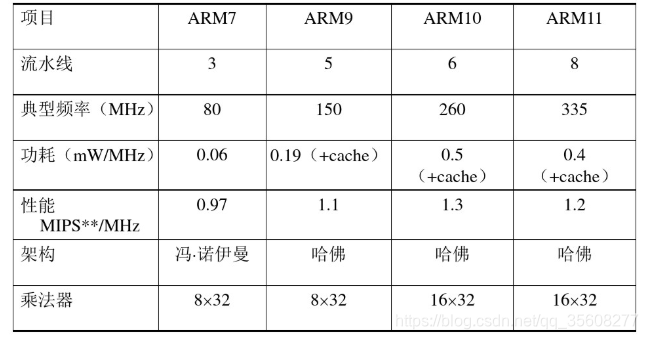

2.2 评价指标

(1)功耗

MIPS/W,单位时间单位功耗指令执行多少百万条指令

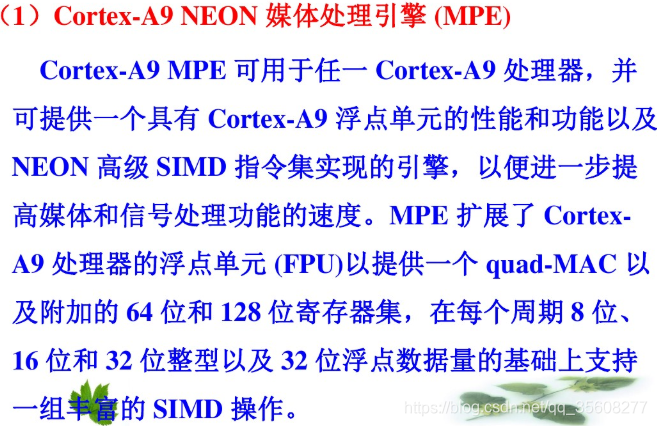

受运行模式影响(Cortex A9):Full Run Mode Standby待机模式;Shutdown停机模式、Dormant、Run Mode with MPE powered off、Run Mode with MPE disabled

(2)代码存储密度

(3)集成度

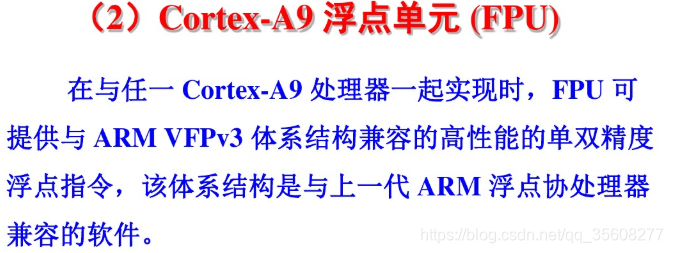

(4)多媒体加速

(5) 性能、效率分析

Dhrystones 整数和逻辑运算性能测试(MIPS) Whetstone 测试浮点运算性能(MFLOPS)

EEMBC 每秒算法执行的次数和编译代码大小

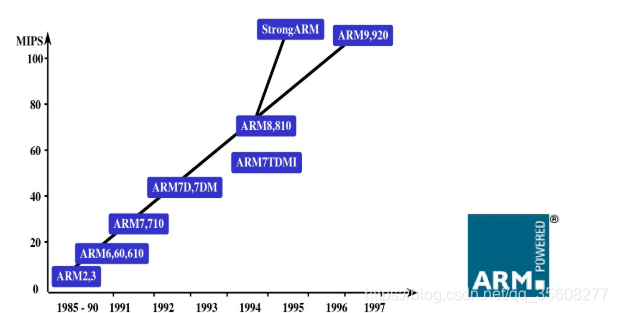

2.3 arm历史

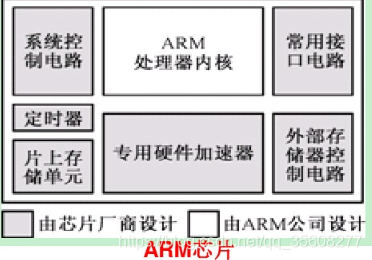

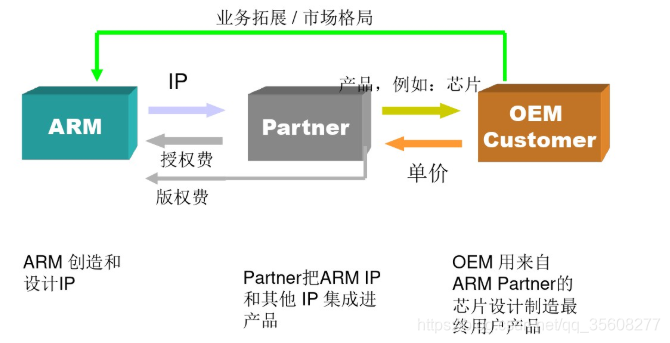

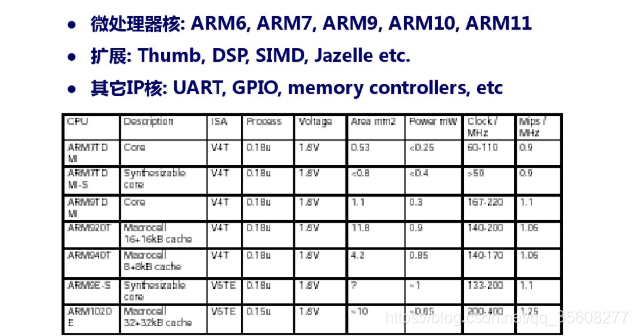

arm 公司只提供 arm系列RISC处理器内核 给半导体生产销售公司,intel ,freescale ,philips atmel sharp sumsung

91年第一个arm6核

93 arm7

业务模型

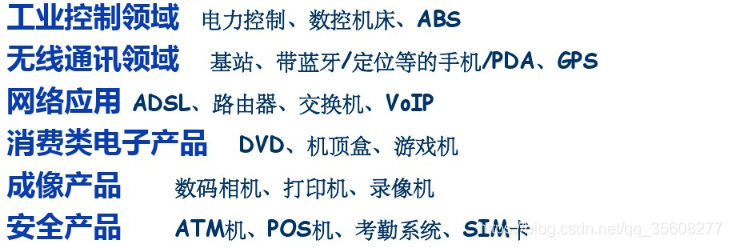

2.4应用领域

2.5特点

(1)RISC技术共同特点

- 大量寄存器,数据和指令的cache,

- 寄存器操作

-

- 定长指令格式,便于流水

- 寻址方式灵活简单

- 内核小,功耗低,成本低

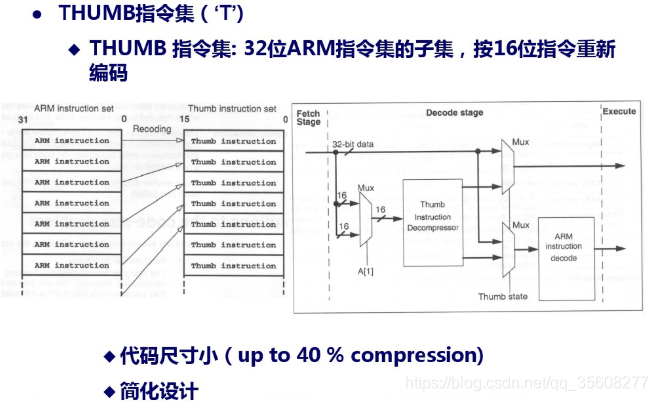

(2)ARM体系特别技术

- 支持Thumb 16bits 和ARM 32bits双指令集

- load/store 指令批量传输数据

- 三地址指令格式

- 数据处理指令包含算数逻辑单元和移位处理

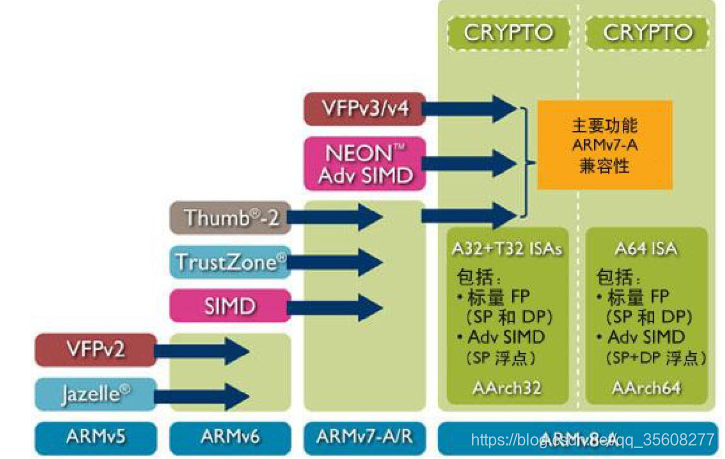

2.6 arm架构发展

v1 寻址空间64MB(26bits)

v3 寻址空间4GB(32bits)

V4 增加16bits Thumb指令集 ARM7 8 9 STRONG ARM

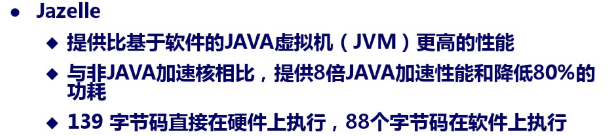

V5 增加指令,Jazelle ARM9、ARM10 XSCALE

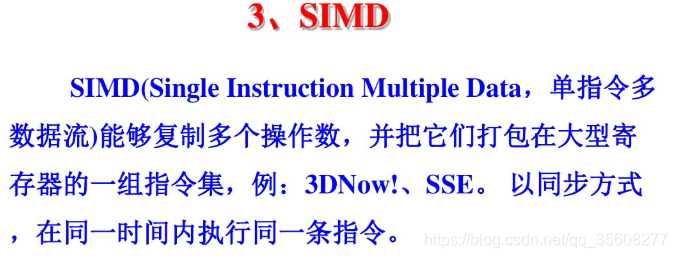

V6 SIMD multi-processing ARM 11

V7 支持Thumb-2技术 Cortex-A8 A9(v7-A)

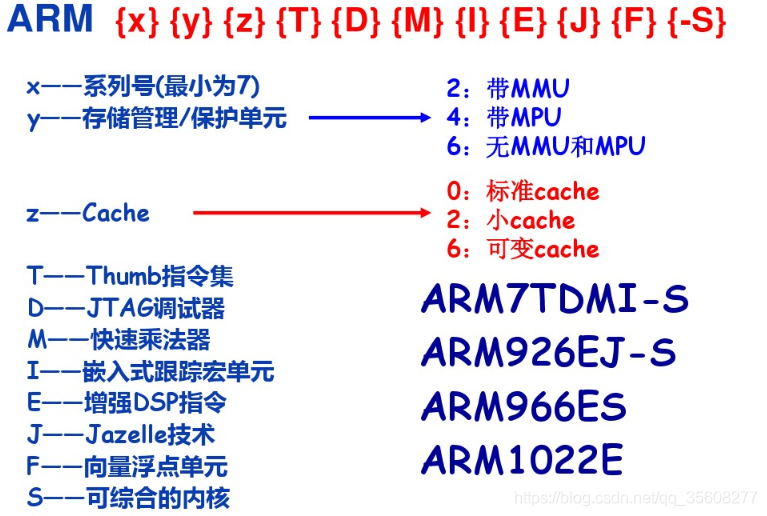

命名

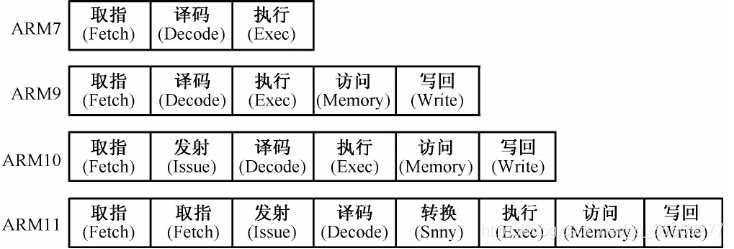

流水线

发展

流水线工作流程

CORTEX -A9

内核结构

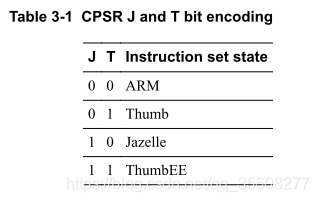

2.7工作状态

支持不同的指令和数据类型

ARM 状态 32bits(字) arm指令

Thumb状态16bits(半字) Thumb指令

Jazelle状态 可变长 Byte为单位 Java指令

ThumbEE状态

复位后ARM

切换

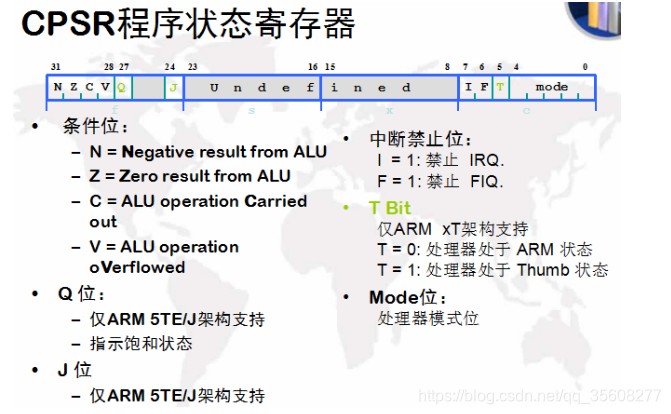

Current Program Status Register

跳转指令BX

2.8 处理器运行模式

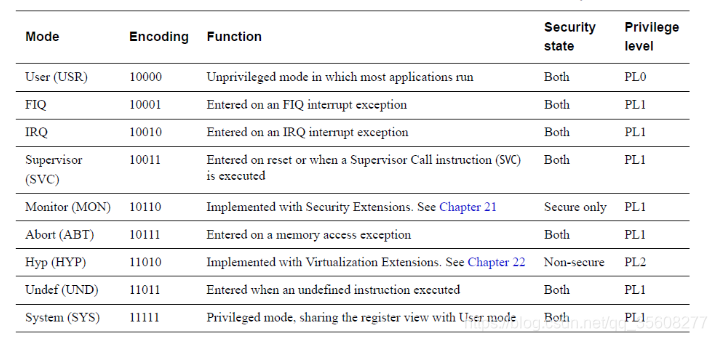

由CPSR Model位决定,

ARMv7理论上说拥有9个模式(3个特权等级PL0-PL2)。

当我们说成是7个的时候,通常是省略了MON和HYP这两个,其中MON主要用于trust OS(安全OS),而HYP主要用于hypervisor(虚拟化)。

- User : 非特权模式,大部分任务执行在这种模式,正常的程序执行状态

- FIQ : 当一个高优先级(fast) 中断产生时将会进入这种模式,用于高速数据传输或通道处理

- IRQ : 当一个低优先级(normal) 中断产生时将会进入这种模式,通用的中断处理

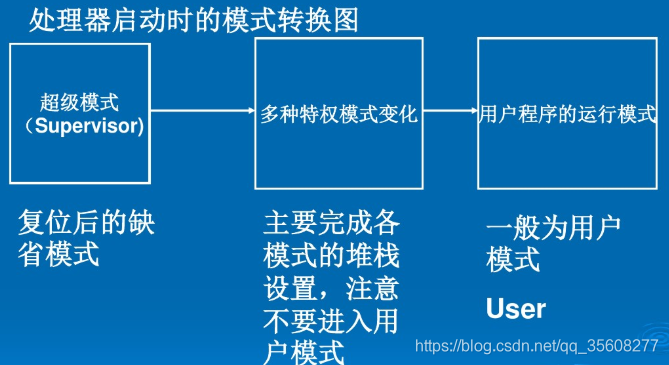

- Supervisor(svc) :当复位或软中断指令执行时将会进入这种缺省模式。操作系统的保护模式

- Abort (abt): 当存取异常时将会进入这种模式,指令预取终止(指令终止)./数据访问终止,可用于虚拟存储和存储保护

- Undef : 当执行未定义指令时会进入这种模式

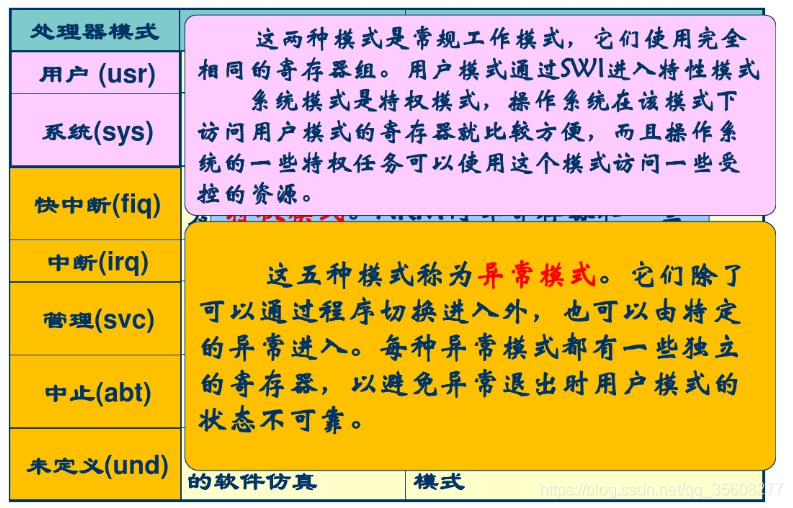

- System : 使用和User模式相同寄存器集的特权模式

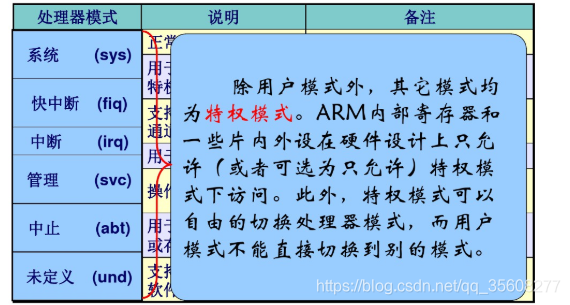

除User(用户模式)是Normal(普通模式)外,其他6种都是Privilege(特权模式)。

Privilege中除Sys模式外,其余5种为异常模式(Exception Modes)。

各种模式的切换,可以是程序员通过代码主动切换(通过写CPSR寄存器);

也可以是CPU在某些情况下自动切换。 各种模式下权限和可以访问的寄存器不同。

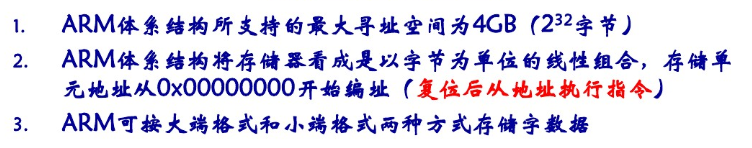

2.9 存储器格式

ARM体系结构允许使用现有的存储器和I/O器件进行各种各样的存储器系统设计。

(1)地址空间

ARM体系结构使用232个字节的单一、线性地址空间。将字节地址做为无符号数看待,范围为0~232-1。

从零地址开始的字节线性组合

32bits 4Bytes

4GB

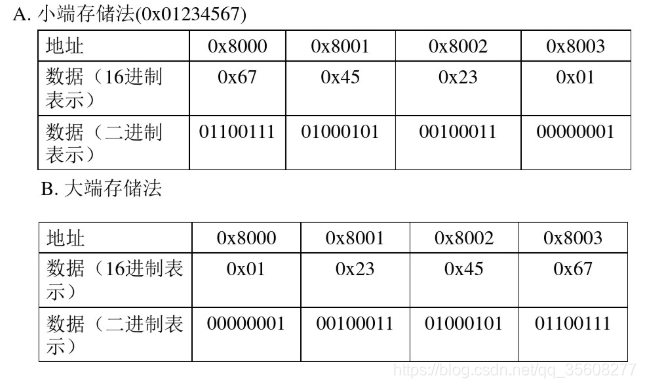

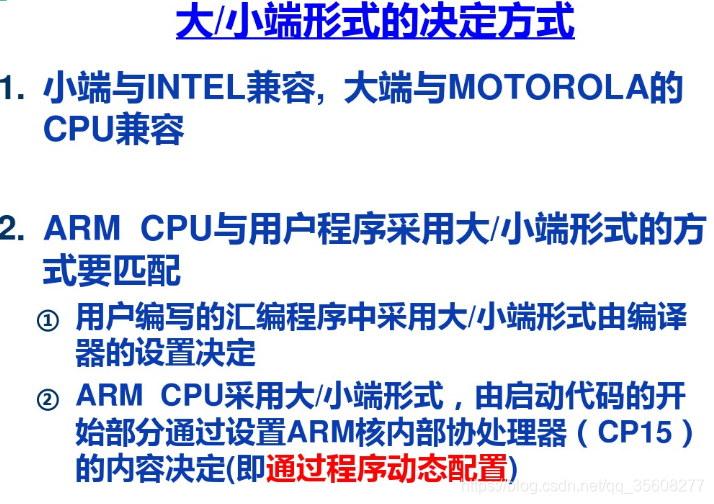

(2)存储器格式

(1)大端格式

word 数据的低字节放在地址的高位

eg

byte 在地址中对应7-0bit 15-8bit 23-16bit 31-24bit

(2)小端格式

小对小

是默认的方式

(3) ARM存储器结构

ARM处理器有的带有指令Cache和数据Cache,但不带有片内RAM和片内ROM。系统所需的RAM和ROM(包括Flash)都通过总线外接。

由于系统的地址范围较大(232=4GB),

有的片内还带有存储器管理单元MMU(Memory Management Unit)

ARM架构处理器还允许外接PCMCIA。

(4).存储器映射I/O

ARM系统使用存储器映射I/O。I/O口使用特定的存储器地址,当从这些地址加载(用于输入)或向这些地址存储(用于输出)时,完成I/O功能。

加载和存储也可用于执行控制功能,代替或者附加到正常的输入或输出功能。

然而,存储器映射I/O位置的行为通常不同于对一个正常存储器位置所期望的行为。

例如,从一个正常存储器位置两次连续的加载,每次返回的值相同。而对于存储器映射I/O位置,第2次加载的返回值可以不同于第1次加载的返回值。