Cortex - M3 CPU

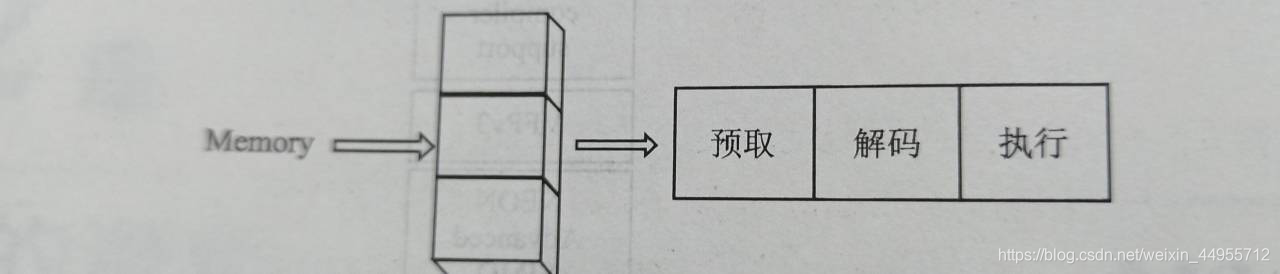

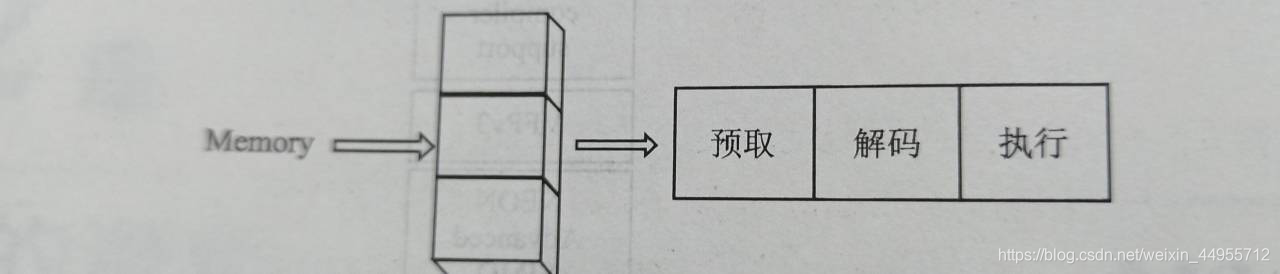

管道

Cortex - M3 CPU使用三级管道,并且使用分支预测技术提高管道使用率

原理:当一个分支指令来临时,会进行一次预测性的装载,从而使每一种可能的结果都得到执行,

而不会对CPU性能产生负面影响。最坏的情况是某个分支里,预测性的装载无法进行,需要刷新管道

Cortex - M3 CPU三级管道技术

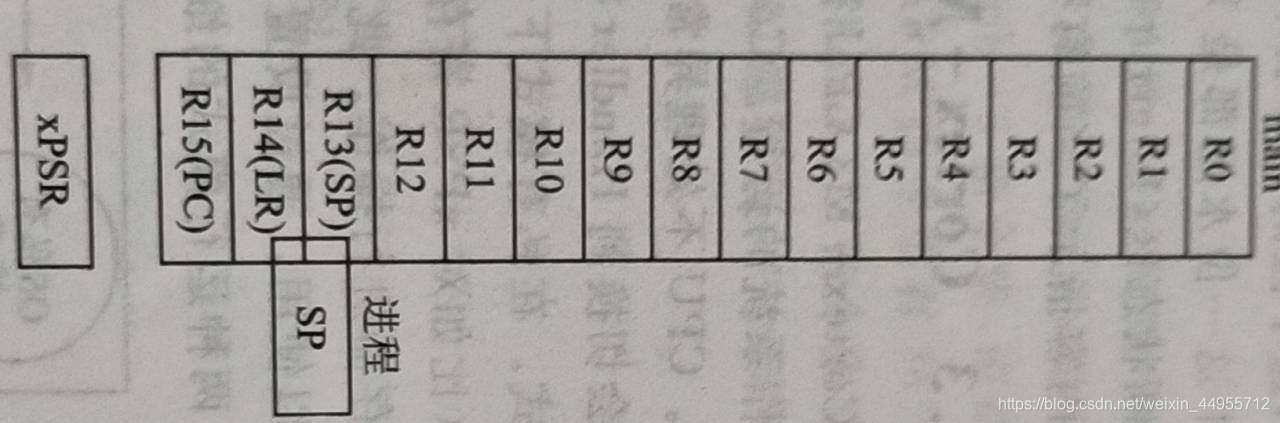

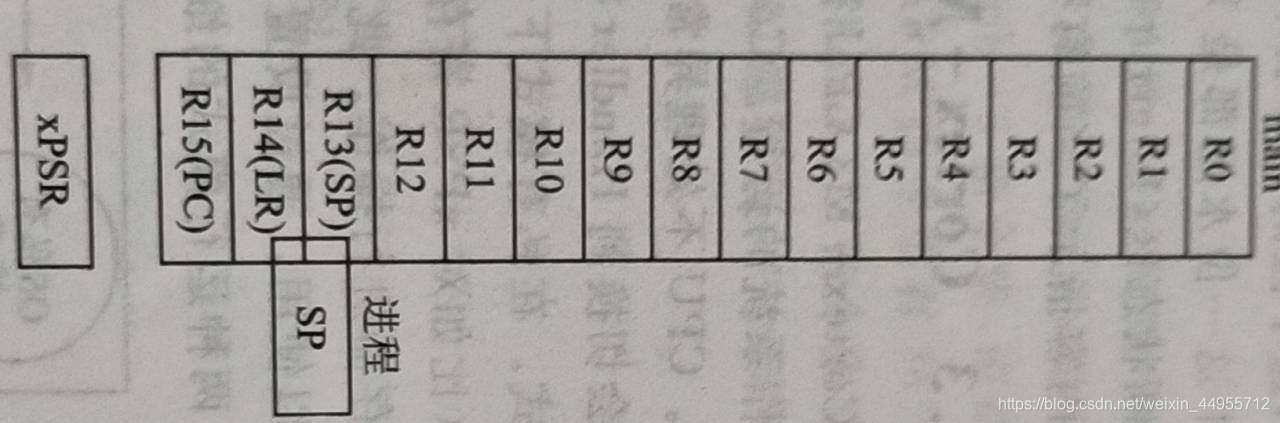

编程模型

Cortex - M3 CPU是基于“载入-储存”式的架构。寄存器组包含16个32位的寄存器。

R0~R12是基本寄存器,用来保护程序变量

R13~R15是特殊功能寄存器。

R13 寄存器来保护堆栈指针,允许CPU的两种操作模式都拥有自己的对栈空间,将两个堆栈分别称为主堆栈和进程堆栈。

R14 寄存器为链接寄存器,执行跳转指令时保存程序返回地址,可以加快CPU快速调出进程

R15 寄存器是程序计数器(PC),和其他寄存器一样进行读写操作

Cortex - M3 CPU的运行模式

Cortex - M3 CPU的两种运行模式:线程模式和处理模式

CPU不处理异常事件时会运行在线程模式;

当CPU需要处理一个异常事件时用处理模式

Cortex - M3 CPU的两种处理代码的方式:私有模式和非私有模式

私有模式下,CPU处理所有指令;

在非私有模式下,部分指令是被禁止执行,同时不能的CPU的系统控制区中的寄存器进行操作

非对齐存取接口

原因:由于数据必须对齐取的原则,浪费了SRAM。同时Cortex - M3处理器的“位带”技术允许程序标志位写入“字”或者“半字”变量内部,又扩大浪费。

Cortex - M3 CPU可以实现字”或者“半字”对齐的寻址方式,同时可以使用非对齐存取方式。