时钟的选择输入

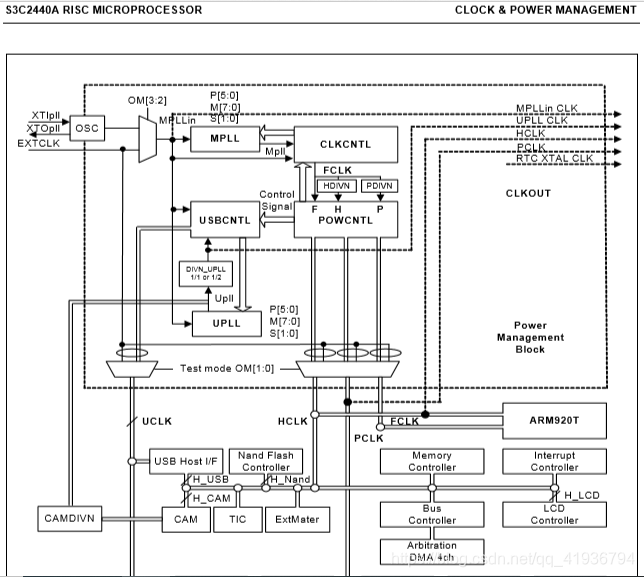

S3C2410/S3C2440的时钟控制逻辑即可以外界晶振,然后通过内部电路产生时钟源,也可以直接使用外部提供的时钟源,它们通过引脚的设置来选择,可以看出2440的时钟来源有两个,一个是晶振OSC(图左上角),可以通过EXTCLK引脚输入的时钟,然后通过OM [3 :2]选择器,

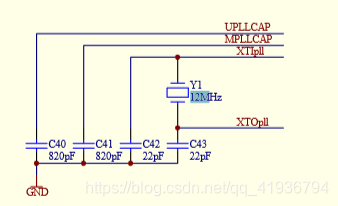

查看下面原理图,我们可以知道JZ2440的晶振来源时12Mhz,看上图晶振12MHz通过OM进入到MPLL,使用P [5:0],M [7:0],S [1:0]来控制输出的频率,晶振12MHz通过OM进入到UPLL,使用P [5:0],M [7:0],S [1:0]来控制输出的频率,

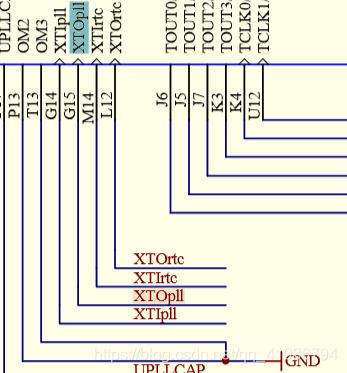

根据原理图可以知道OM2,OM3为00,根据芯片得知00时使用外部晶振源作为时钟输入也就是12Mhz

不同时钟源的不同应用

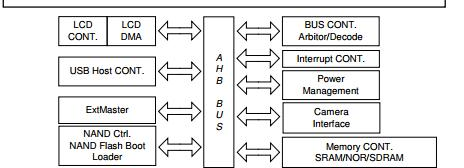

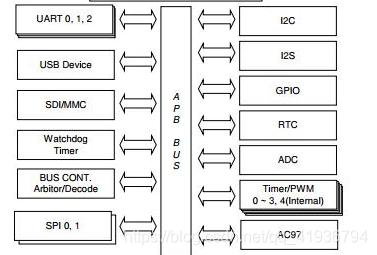

时钟控制逻辑给整个芯片提供3种时钟:FLCK(用于cpu核),HCLK(用于AHB上总线上的设备),PCLK(用于APB总线上的设备)

AHB总线:主要用于高性能模块

APB总线:主要用于低带宽的周边外设连接

提高系统时钟的方法

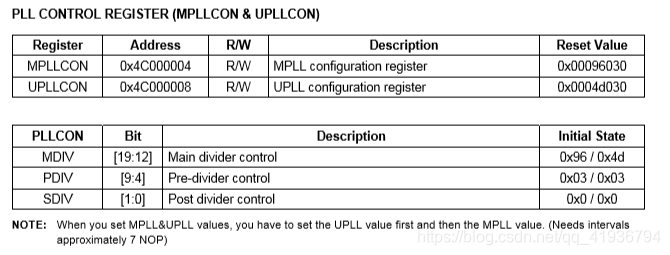

S3c2440的CPU核的工作电压为1.2时,主频可以达到300Mhz,工作电压为1.3V时,主频可以达到400Mhz,一般为了减少电磁干扰,可以接上频率较低的外部晶振,然后通过PLL提高系统时钟,S3C2440里有两个PLL:MPLL和UPLL,MPLL用来产生FCLK,HCLK,PCLK的高频工作时钟,UPLL用来为USB提供工作频率,PLL原理如下

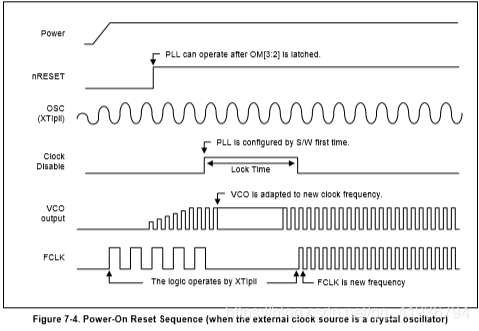

1.上电几毫秒后,图中的晶振(OSE)输出稳定后,FLCK此时等于晶振频率,复位信号变成高电平

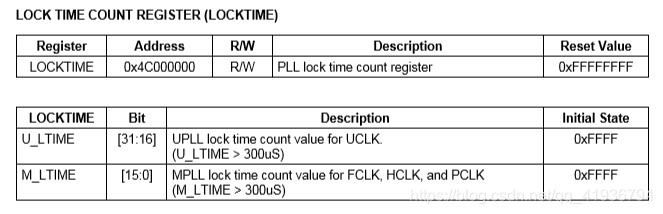

2.读取MPLL的设置,此时FLCK停振,lock time的长短由寄存器LOCKTIME决定

3.LOCKTIME之后,MPLL输出正常,CPU工作在新的FCLK下

编程寄存器控制:

锁定时间LOCKTIME一般采取默认值

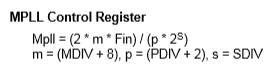

用于设置FCLK和外部晶振的输入比列关系,公式如图

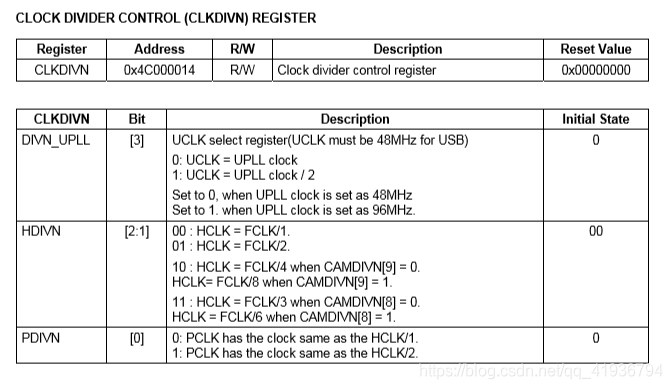

用于设置时钟之间的比例

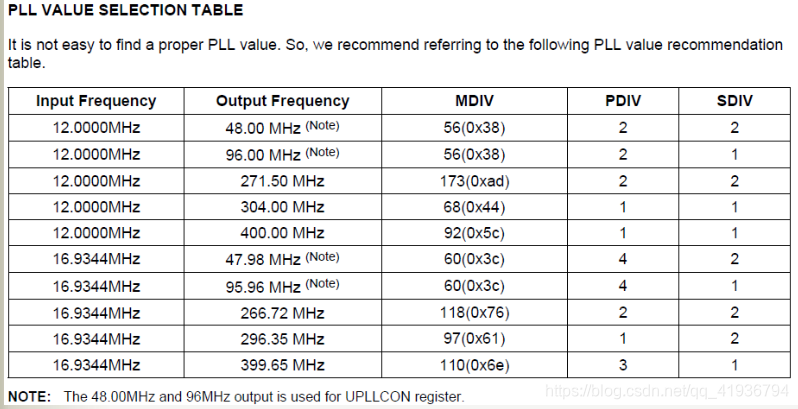

默认参考值

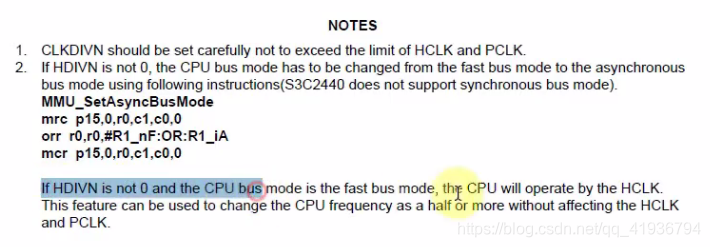

如果HDIVN不等于0,CPU必须设置为异步模式,CPU会工作于HCLK,如下图

代码:

start.S

.text

.global _start

_start:

/*关闭看门狗*/

ldr r0,=0x53000000

ldr r1,=0

str r1,[r0]

/*初始化时钟*/

/*设置locktime*/

ldr r0,=0x4C000000

ldr r1,=0xFFFFFFFF

str r1,[r0]

/*设置工作于异步模式下*/

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000

mcr p15,0,r0,c1,c0,0

/*设置时钟比例*/

ldr r0,=0x4C000014

ldr r1,=0x5

str r1,[r0]

/*设置提高时钟倍数*/

ldr r0,=0x4C000004

ldr r1,=(92<<12)|(1<<4)|(1<<0)

str r1,[r0]

/*判断是nand启动还是nor启动*/

mov r1,#0

ldr r0,[r1]

str r1,[r1]

ldr r2,[r1]

cmp r1,r2

ldr sp,=0x40000000+4096

moveq sp,#4096

streq r0,[r1]

bl main

halt:

b halt

led.c

#include "s3c2440_soc.h"

void delay(volatile int d)

{

while(d--);

}

int main(int argc, char * * argv)

{

int val = 0;

int tmp;

GPFCON&=~((3<<8)|(3<<10)|(3<<12));

GPFCON|=((1<<8)|(1<<10)|(1<<12));

while (1)

{

tmp = ~val;

tmp &= 7;

GPFDAT &= ~(7<<4);

GPFDAT |= (tmp<<4);

delay(100000);

val++;

if (val == 8)

val =0;

}

return 0;

}