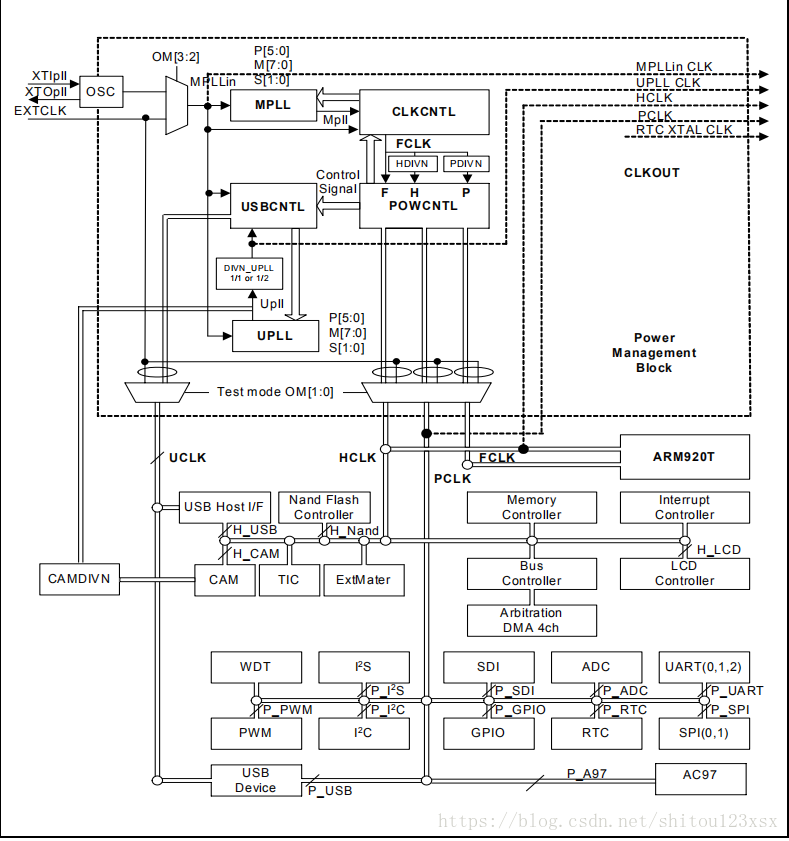

首先来看一下S3C2440的时钟整体框图:

CPU工作于FCLK FCLK UP TO 400MHZ

AHB工作于HCLK HCLK UP TO 136MHZ

APB工作于PCLK PCLK UP TO 68MHZ

如何得到以上时钟频率(时钟源:12M晶振):通过PLL锁相环可以得到以上3个所需要的时钟

S3C2440有两个PLL 一个MPLL是提供时钟给CPU用 另一个UPLL提供时钟给USB设备使用

S3C2440时钟源有两种:1:外部时钟源EXTCLK

2:外部晶振

可通过OM[3:2]引脚进行选择外部时钟模式,通过OM3 OM2引脚电平可以进行选择时钟源。

通过MPLL的得到FCLK提供给CPU

通过HDIVN分频得到HCLK

通过PDIVN分频得到PCLK

通过以上框图可以看出来通过设置寄存器控制MPLL HDIV PDIV便可以来设置时钟频率。

用来设置Lock Time时间

/*设置MPLL FCLK:HCLK:PCLKI=400:100:50*/

/*LOCKTIME(0X4C000000)=0XFFFFFFFF*/

ldr r0,=0x4c000000

ldr r1,=0xffffffff

str r1,[r0]

通过设置CLKDIVN寄存器可以设置HCLK和PCLK的所分频率

/*CLKDIVN(0X4C000014)=0X5,tFCLK:tHCLK:tPCLK=1:4:8*/

ldr r0,=0x4c000014

ldr r1,=0x5

str r1,[r0]

当HDIVN不为0时,需要设置CPU工作于异步模式,否则CPU的工作频率为HCLK所产生的频率

/*设置CPU工作在异步模式*/

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

设置MPLL让FCLK输出400M,

M=92

P=1

S=1

通过设置MDIV PDIV SDIV寄存器可设置MPLL

设置FCLK频率为400M

/*设置MPLLCON(0X4C000004)=(92<<12)|(1|4)|(1<<0)

m=MDIV+8=92+8=100

P=PDIV+2=1+2=3

S=SDIV=1

FCLK=2*M*Fin/(P*2^S)=2*100*12/(3*2^1)=400m

*/

ldr r0,=0x4c000004

ldr r1,=(92<<12)|(1<<4)|(1<<0)

str r1,[r0]

以下为配置S3C2440时钟的汇编代码:

/*设置MPLL FCLK:HCLK:PCLKI=400:100:50*/

/*LOCKTIME(0X4C000000)=0XFFFFFFFF*/

ldr r0,=0x4c000000

ldr r1,=0xffffffff

str r1,[r0]

/*CLKDIVN(0X4C000014)=0X5,tFCLK:tHCLK:tPCLK=1:4:8*/

ldr r0,=0x4c000014

ldr r1,=0x5

str r1,[r0]

/*设置CPU工作在异步模式*/

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

/*设置MPLLCON(0X4C000004)=(92<<12)|(1|4)|(1<<0)

m=MDIV+8=92+8=100

P=PDIV+2=1+2=3

S=SDIV=1

FCLK=2*M*Fin/(P*2^S)=2*100*12/(3*2^1)=400m

*/

ldr r0,=0x4c000004

ldr r1,=(92<<12)|(1<<4)|(1<<0)

str r1,[r0]

/*一旦设置PLL,就会锁定lock time直到PLL输出稳定

然后CPU工作于新的频率FCLK

*/