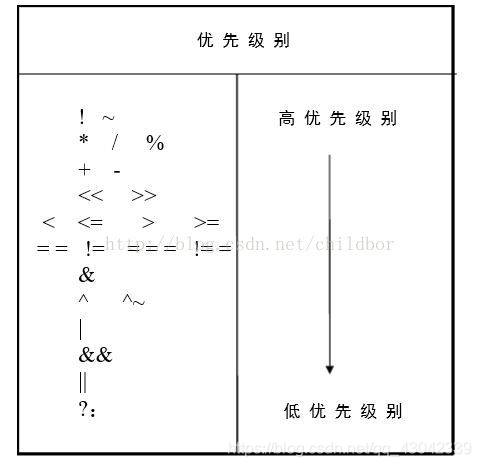

A选项考虑优先级的问题。

B考察阻塞赋值和非阻塞赋值。

【1】组合逻辑的always模块中使用阻塞赋值(=),一旦敏感列表没有 posedge 就用”=”,一旦看到 assign 就用”=”;

【2】时序逻辑的always模块中使用非阻塞赋值(<=),一旦看到敏感列表有 posedge 就用”<=”;

【3】可以这样理解,组合中计算马上赋值(实时变化),时序逻辑中上升沿计算,下降沿赋值(由时钟控制)

【4】时序逻辑和组合逻辑分成不同的模块,即一个 always 模块里面只能出现非阻塞赋值”<=”或者”=”。

关键是组合逻辑中是实时变化的,而时序逻辑中一个cycle才变化一次

比如:

always @(a or b)

begin

c = a + b;

end

always @(posedge clk)合看看,或者哪位高人补上~~应该注意的是,如果想象不出这种

怪异的 coding 方式会产生何种电路,就不要这么写,因为实现这种逻辑最好

begin

if(rst)

c <= 0;

else

c <= a + b;

end

在组合逻辑的always block中,a和b的变化都会引起c值的变化;

而时序逻辑中c至少会维持一个clock cycle,也就是说如果a和b的变化导致c变化的时间是在下一个clock的上升沿,而不会让c立刻改变。

阻塞赋值“=”与非阻塞赋值“<=”的本质区别在于:

【1】非阻塞赋值语句右端表达式计算完后并不立即赋值给左端,而是同时启动下一条语句继续执行,可以将其理解为所有的右端表达式RHS1、RHS2等在进程开始时同时计算,计算完后 ,等进程结束时同时分别赋给左端变量LHS1、LHS2等;

【2】而阻塞赋值语句在每个右端表达式计算完后立即赋给左端变量,即赋值语句LHS1=RHS1执行完后LHS1是立即更新的,同时只有LHS1=RHS1执行完后才可执行语句LHS1=RHS2,依次类推。前一条语句的执行结果直接影响到后面语句的执行结果;

【3】阻塞赋值可以看成一条导线,而非阻塞赋值可以看成是寄存器;a操作就是将a中的每一位按位逐一进行异或,例如a=4’b1010,则b=1010=0,由此可以判断a中为1的位数是奇数还是偶数,是一个便捷的操作。

【4】时序逻辑内的判断越简单越好,尽量都放在组合逻辑里面做,时序逻辑只负责 flop 一下。

【5】begin/end块内的多条阻塞赋值语句是串行执行的。多条非阻塞赋值语句却是并行执行的,这些非阻塞赋值语句都会在其中任何一条语句执行完成之前开始执行。

https://www.cnblogs.com/danh/archive/2010/12/24/1915810.html

C选项考察可综合的语句:

【1】所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri(用来表示多驱动器驱动的网络型数据),supply0(地),supply1(电源),reg(reg类型的变量则为无符号数),integer(integer类型的变量为有符号数),default,for,function,and,nand,or,nor,xor,xnor,buf(实际电路存在延迟,仿真时可以使用buf语句模拟延迟的产生),not,bufif0,bufif1,generate,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。

(2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。

(3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。

建立可综合模型的原则

要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点:

(1)不使用initial。

(2)不使用#10。

(3)不使用循环次数不确定的循环语句,如forever、while等。

(4)不使用用户自定义原语(UDP元件)。

(5)尽量使用同步方式设计电路。

(6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。

(7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有https://www.cnblogs.com/danh/archive/2010/12/24/1915810.htmlhttps://www.cnblogs.com/danh/archive/2010/12/24/1915810.htmlhttps://www.cnblogs.com/danh/archive/2010/12/24/1915810.html的输入信号。

(8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。

(9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。

(10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。

(11)如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。

(12)避免混合使用上升沿和下降沿触发的触发器。

(13)同一个变量的赋值不能受多个时钟控制,也不能受两种不同的时钟条件(或者不同的时钟沿)控制。

(14)避免在case语句的分支项中使用x值或z值。

不可综合verilog语句2009-04-14 19:33

1、initial 只能在test bench中使用,不能综合。(我用ISE9.1综合时,有的简单的initial也可以综合,不知道为什么)

2、events : event在同步test bench时更有用,不能综合。

3、real :不支持real数据类型的综合。

4、time :不支持time数据类型的综合。

5、force 和release : 不支持force和release的综合。

6、assign 和deassign :不支持对reg 数据类型的assign或deassign进行综合,支持对wire数据类型的assign或deassign进行综合。

7、fork join :不可综合,可以使用非块语句达到同样的效果。

8、primitives :支持门级原语的综合,不支持非门级原语的综合。

9、table :不支持UDP 和table的综合。

10、敏感列表里同时带有posedge和negedge

如:always @(posedge clk or negedge clk) begin…end ,这个always块不可综合。

11、同一个reg变量被多个always块驱动

12、延时: 以#开头的延时不可综合成硬件电路延时,综合工具会忽略所有延时代码,但不会报错。

如:a=#10 b;

这里的#10是用于仿真时的延时,在综合的时候综合工具会忽略它。也就是说,在综合的时候上式等同于a=b;

13、与X、Z的比较: 可能会有人喜欢在条件表达式中把数据和X(或Z)进行比较,殊不知这是不可综合的,综合工具同样会忽略。所以要确保信号只有两个状态:0或1。

1、在使用verilog描述电路时,既可以进行行为级的描述,也可以进行结构级的描述。

①行为级描述:侧重对模块行为功能的抽象描述。

②结构级描述:侧重对模块内部结构实现的具体描述。

2、行为级描述

①描述体的组成

※由多个并行运行的过程块组成。

※过程块由过程语句(initial和always)和块语句(串行块begin-end和并行块fork-join)组成。

※块语句由过程赋值语句和高级程序语句构成。

◇过程赋值语句:阻塞与非阻塞式赋值。

◇高级程序语句:C语言如if-else、case、while、wait等组成。

行为级:行为级是RTL级的上一层。最符合人类思维的描述方式。主要用于快速验证算法的正确性,不关注电路的具体结构,不一定可以综合成实际电路结构。注重算法。以直接赋值的形式进行,只关注结果。常采用大量运算,延迟等无法综合的语句。其目的不在于综合,而在于算法。

RTL级:**使用寄存器这一级别的描述方式来描述电路的数据流方式。**RTL在很大程度上是对流水线原理图的描述。接近实际电路结构的描述,可以精确描述电路的原理、执行顺序等。其目的在于可综合。

门级:使用逻辑门这一级别来描述。RTL 中的寄存器和组合逻辑,其物理实现还是对应到具体门电路。但目前寄存器,组合逻辑等的电路结构基本稳定。一般EDA工具可以把RTL描述自动编译为门级描述。所以一般不直接使用门级编程。

D项考察的是^的用法:奇偶判断

a操作就是将a中的每一位按位逐一进行异或,例如a=4’b1010,则b=1010=0,由此可以判断a中为1的位数是奇数还是偶数,是一个便捷的操作。

参考博客:

【1】https://blog.csdn.net/weixin_30614109/article/details/96806110

【2】https://blog.csdn.net/u012694677/article/details/89601675

【3】https://blog.csdn.net/Mys_GoldenRetriever/article/details/83796538

【4】https://blog.csdn.net/Leo_Luo1/article/details/72848752

【5】https://www.cnblogs.com/danh/archive/2010/12/24/1915810.html