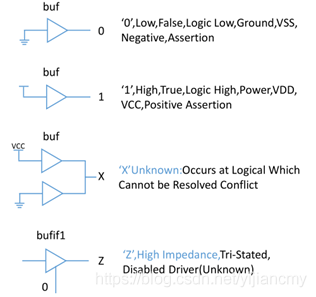

逻辑值

逻辑0:表示低电平,也就对应电路GND;

逻辑1:表示高电平,也就对应电路的VCC;

逻辑X:表示未知,有可能是高电平,也有可能是低电平;

逻辑Z:表示高阻态,外部没有激励信号,是一个悬空状态。

如图所示:

数字进制格式

Verilog数字进制格式包括二进制(b)、八进制(o)、十进制(d)和十六进制(h)。一般常用的为二进制、十进制和十六进制。

二进制表示:4’b0101表示4位二进制数字0101

十进制表示:4’d2表示4位十进制数字2(二进制0010)

十六进制表示:4’ha表示4位十六进制数字a(二进制1010)

最前面的数值4代表位宽(同二进制的位宽单位对应),若未指定位宽,默认32位位宽,若没有指定进制,默认十进制。

16;b1001_1010_1010_1001 = 16’h9AA9 (下划线为了增强可读性,对程序数值表示没有影响)

标识符

标识符(identifier)用于定义模块名、端口名、信号名等。

标识符可以是任意一组字母、数字、$符号和_(下划线)符号的组合,但标识符的第一个字符必须是字母或者下划线,标识符区分大小写。

不建议大小写混合使用,普通内部信号建议全部小写,信号命名最好体现信号的含义、简洁、清晰、易懂。

数据类型

在Verilog语言中,主要有三大数据类型:寄存器数据类型、线网数据类型和参数数据类型。真正在数字电路中起作用的数据类型应该是寄存器数据类型和线网数据类型。

寄存器类型

寄存器表示一个抽象的数据存储单元,通过赋值语句可以改变寄存器存储的值,寄存器数据类型的关键字是reg,reg类型数据的默认初始值为不定制X

//reg define

reg [31:0] delay_cnt; //延时计数

reg key_reg; //若未定义位宽,默认为1位宽

reg类型的数据只能在always语句和initial语句中被复制。

如果该过程语句描述的是时序逻辑,即always语句带有时钟信号,则该寄存器变量对应为触发器;

如果该过程语句描述的是组合逻辑,即always语句不带有时钟信号,则该寄存器变量对应为硬件连接;

线网类型

线网数据类型表示结构实体(例如门)之间的物理连线。线网类型的变量不能存储值,它的值是由驱动它的元件所决定的。

驱动线网类型变量的元件有门、连续赋值语句、assign等。如果没有驱动元件连线到线网类型的变量上,则该变量就是高祖的,即其值为z。

线网数据类型包括wire型和tri型,其中最常用的就是wire类型。

//wire define

wire key_flag; //没有定义位宽,默认为一个位宽

参数类型

参数其实就是一个常量,在Verilog HDL中用parameter定义常量。

可以一次定义多个参数,参数与参数之间需要用逗号隔开。

每个参数定义的右边必须是一个常量表达式。

//parameter define

parameter H_SYNC = 11'd41;

parameter H_BACK = 11'd2;

参数型数据常用于定义状态机的状态、数据位宽和延迟大小等。采用标识符来代表一个常量可以提高程序的可读性和可维护性。在模块调用时,可通过参数传递来改变被调用模块中已定义的参数。

运算符

Verilog中操作符按照功能可以分为下述类型:1.算数运算符;2.关系运算符;3.逻辑运算符;4.条件运算符;5.位运算符;6.移位运算符;7.拼接运算符

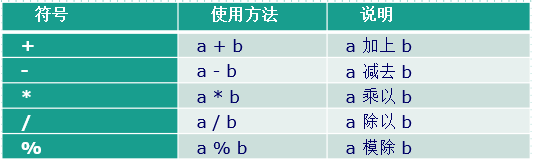

算数运算符 /的结果小数部分被省略,取整;%求余操作

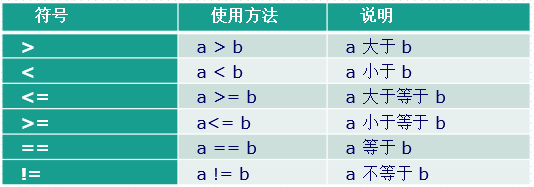

关系运算符

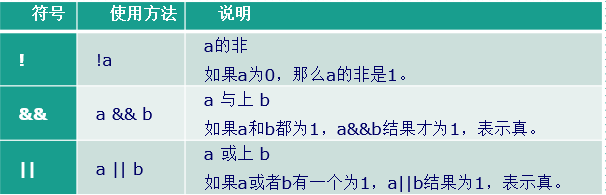

逻辑运算符

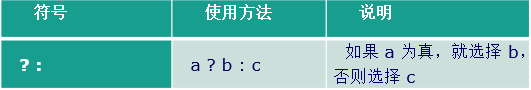

条件运算符

位运算符

如果两个数的位宽不一样,位宽小的那个变量前面补0。

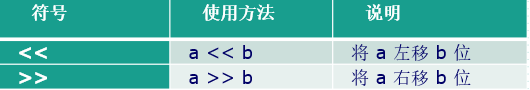

移位运算符

两种移位运算符都用0来填补移出的空位,左移时,位宽增加;右移时,位宽不变。

例:4’b1001 << 2 = 6b’100100; 4b’1001 >> 1 = 4b’0100;

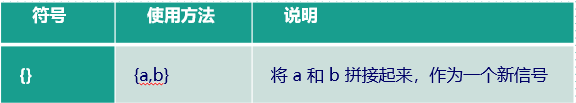

拼接运算符

例: c = {a,b[3:0]}; 将a与b的低四位拼接起来。

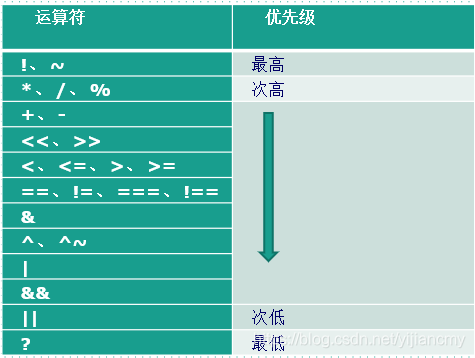

运算符的优先级