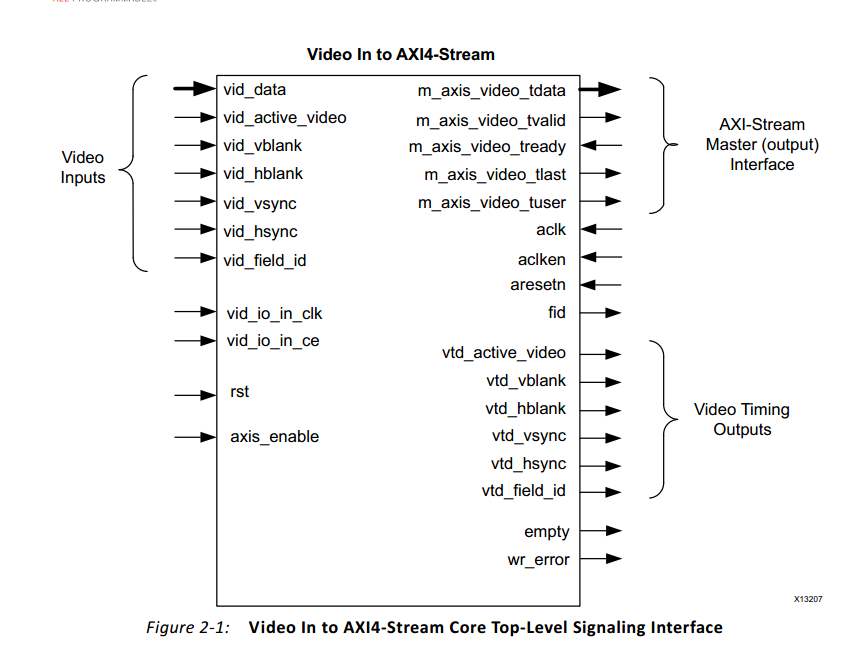

当今Xilinx的IP CORE一般都是以AXI4接口。我们今天来介绍一下Video In to AXI4-Stream 这个IP,这个IP的作用是把标准的VESA信号转为AXI4-Stream信号。在ZYNQ 7000里面,这样的AXI4-Stream接口就可以DMA IP结合实现把FPGA采集到的视频数据直接DMA到PS端的DDR3缓存里面,非常实用。下面看一下这个IP 的接口:

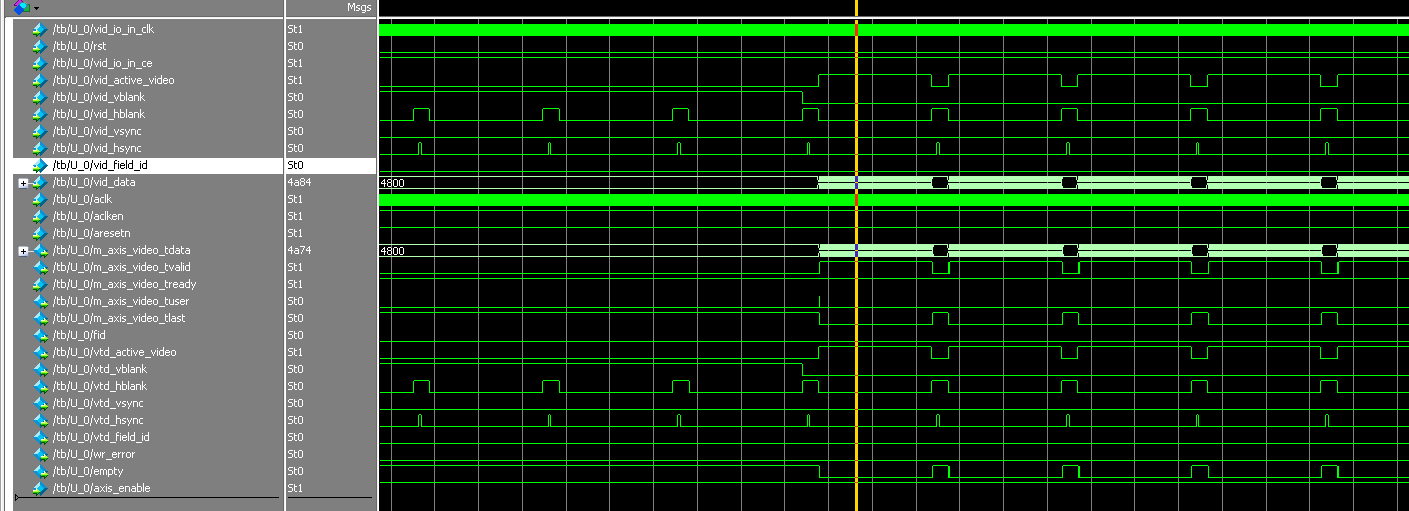

但是按照VESA标准把激励标准的 1080p 60Hz的视频信号 输入到 Video In to AXI4-Stream,调试的时候就是没有m_axis_video_tdata信号输出。后来才知道在IP 正常 工作的时候, rst 应该一直为低电平。 在初始化的时候, rst 要高电平(时间 > 2个时钟周期),然后就可以一直低电平。这时候 IP Core 就可以正常工作了。

介绍下这个IP的关键信号

READY/VALID Handshake

A valid transfer occurs whenever READY, VALID, ACLKEN, and ARESETn are high at the rising edge of ACLK. During valid transfers, DATA only carries active video data. Blank periods and ancillary data packets are not transferred via the AXI4-Stream Video protocol.

Driving m_axis_video_tready

The m_axis_video_tready signal can be asserted before, during, or after the cycle in which the Video in to AXI4-Stream core asserted m_axis_video_tvalid. The assertion of m_axis_video_tready may be dependent on the value of m_axis_video_tvalid. A slave that can immediately accept data qualified by m_axis_video_tvalid should preassert its m_axis_video_tready signal until data is received. Alternatively, m_axis_video_tready can be registered and driven the cycle following VALID assertion. It is recommended that the AXI4-Stream slave should drive READY independently, or pre-assert READY to minimize latency.

SOF ‐ m_axis_video_tuser

The SOF signal, physically transmitted over the AXI4-Stream tuser signal, marks the first pixel of a video frame. The SOF pulse is 1 valid transaction wide, and must coincide with the first pixel of the frame. SOF serves as a frame synchronization signal, which allows downstream cores to re-initialize, and detect the first pixel of a frame. The SOF signal may be asserted an arbitrary number of aclk cycles before the first pixel value is presented on tdata, as long as a tvalid is not asserted.

EOL Signal ‐ m_axis_video_tlast

The EOL signal, physically transmitted over the AXI4-Stream tlast signal, marks the last pixel of a line. The EOL pulse is 1 valid transaction wide, and must coincide with the last pixel of a scanline, as seen in Figure 2-6.

关键看黑体部分:

tuser在xilinx的设计中,变成了帧开始(SOF)信号。这点很关键,会在VDMA中用到。

tlast在xilinx的设计中,变成了行结束(EOL)信号。VDMA需要设置帧的分辨率,EOL用于写入像素的统计。

关于像素打包

在IP设置中,是允许对像素进行打包的。

入下图:

输入是RGB,每个分量是8bit,选择输出每个分量也是8bit,每个时钟1个像素。可以看到m_axis_video_tdata的位宽为24。

如果每个时钟选择2个像素,那m_axis_video_tdata的位宽就变成48了。

如果输入RGB每个分量是8bit,除了8bit,输出还可以设置成10,12,16。比如输出位宽为10,IP会自动将8bit映射到高8位,低2位填0。。。

如果输入RGB每个分量是10bit,除了10bit,输出还可以设置成8,12,16。比如输出位宽为8,IP会自动将高8位映射到输入,抛弃低2位。输出位宽位12,IP会自动将10bit映射到高10位,低2位填0。。。