第三课

Design and library objects

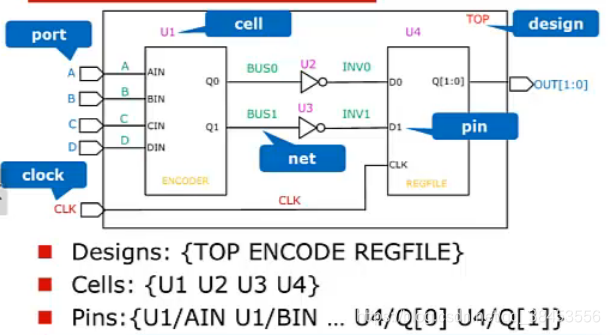

Design Object

-

Verilog层面

Object分为六种:Design, Clock, Port, Net, Cell和Pin。

几点区别:Design是目前所在的__顶层__,而Cell是顶层中__例化的模块__;Port是顶层和外界交互的端口,而Pin是例化模块和模块外部进行交互的端口。

**Object的概念类似于编程语言中的的“对象”。 -

Schematic层面

根据所选视角的不同,可以由同名不同类型的object,例如CLK可以是clock,net,也可以是pin,在写tcl语句时,需要对不同属性加以区分。尤其是design和cell随时会发生转换。

Commands

Q: 如何消除歧义?

例如命令 set_load 5 SUM ,没有指定SUM的类型是net还是port,那么5pF的电容负载无法确定加载在什么地方,默认会加载在port上。

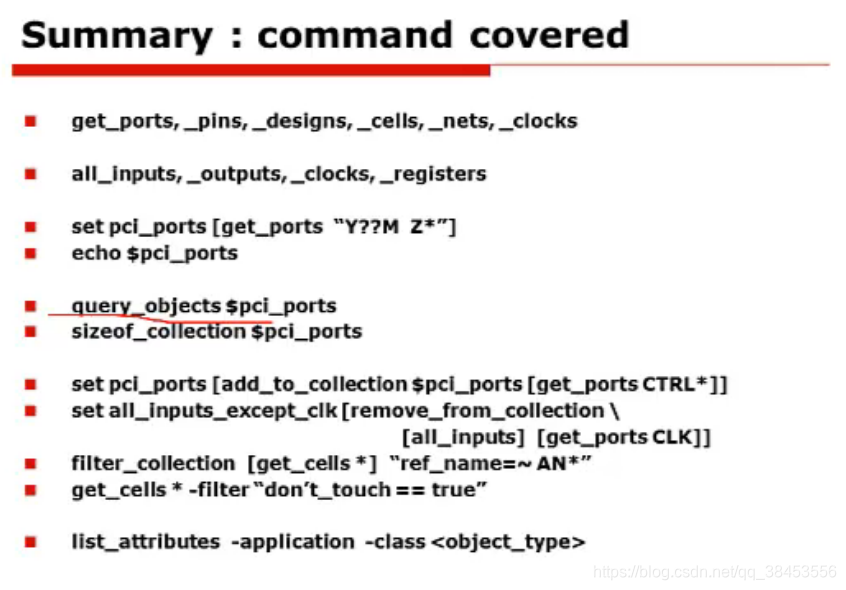

- get_* 命令

set_load 5 [get_nets SUM]

get_命令可以返回具有相应类型和名字的object,obejct名当中还可以使用“”和“?”通配符。如果没有符合条件的object,就会返回“empty collection”。

- all_命令

根据位置所对应的类型,会返回相应类型的所有物体。

remove_from_collection [all_inputs] [get_ports CLK]

此命令可以可以从前一个中括号指定的物集中去除后一个中括号中的物集。

命令总结:

Attributes & Collections

每种类型有其独特的属性(attributes),例如

ports:direction,driving_cell_rise,load,max_capacitance,etc.

cells:dont_touch,is_hierarchical,is_mapped,is_sequential,etc.

DC的约束文件本质上就是对object的attribute施加约束。

注:执行get_和all_命令之后,DC会生成对应object的集合(collection),并返回这个集合对应的句柄(handle)也就是“指针”

set foo [get_ports p*] //foo是collection的名字

sizeof_collection $foo //f输出foo内objection的个数

query_objects $foo //输出foo内所有object的列表

filter_collection [get_cells *] "reg_name =~ AN*" //从cell中过滤出以AN开头的object

foreach_in_collection cell [get_cells -hier * -filter "is_hierarchical == true"]

//相当于对符合条件的object遍历

- 补充

Q:DC有数组的概念吗?

A:有,可以利用命令"set ages(zhangsan) 23" 可以给age集合中的元素zhangsan的赋值23。

"echo $ages(zhangsan)"可以返回属性值。

DC还有自己事先定义的数组__env__,用命令"array names env"可以输出env中所有元素的名字,这个数组实际上就是环境变量的集合。

另外还有命令getenv/get_unix_variable可以获取环境变量。