第二课

Design and technology data

1.载入RTL设计和逻辑库(即Verilog文件和db文件)

2.载入physical technology和design data

包括milkway derectories, tf file, rc modeling files, floorplan data.

需要对一些协议和端口很熟悉,例如PCIE协议、AMPA协议(?)、AMBA总线协议、DMA、CPU等。

甚至比验证人员和后端设计人员要更加了解。

- 本节课需要掌握的命令

设置文件

- .synopsys_dc.setup

set_app_var target_library your_library.db

set_app_var link_library {* your_library.db}

set_app_var symbol_library your_library.sdb

set_app_var search_path " .<Install_dir>/libraries/syn ..."

DC一旦启动,三个目录下面拥有此名字的文件会按顺序执行,分别是:

- $SYNOPSYS/admin/setup(default)

- ~user (user’s general)

- DC startup directory (CWD)

第一个优先级最低,第三个优先级最高,需要修改设置时只修改第三个也就是启动目录下面的文件,保证前两个文件的完整性。

- target library

target library指向厂商所给的工艺库,用来在编译过程中创建基于这个工艺库的门级网表

printvar target_library //打印参数

set_app_var target_library libs/65n_wc.db //设置目标库

set target_library libs/65n_wc.db //set_app_var更容易发现错误,比set更安全

write -format berilog -output mapped/MYREG_mapped.v //以verilog形式保存生成的netlist

目标库的设置一定要在compile命令之前,否则没有意义

生成netlist的用途:用于后仿,生成netlist时除了指定的verilog文件还会生成.sdf和.ddc(.sdc)文件

.ddc ≈ .v + .sdc ,但.ddc文件包含的内容实际上比这两者加起来要多

- link_library

link library有时和target library指的是同一个东西,但实际上有一些区别。

例如有的公司提供IP时只会提供.db/.ddc文件,可以在代码中例化使用但不能查看,这种文件就需要包含到link library当中,供DC综合使用。

DC寻找模块的顺序(1)在DC软件的内存中找和design的名字相同的模块(2)去link_library指定的库列表中寻找library_cell的名字相同的模块

(星号*代表首先在DC的内存当中搜索)

set_app_var link_library "* $target_library"

- search_path

另外还可以使用 search_path 命令告诉DC需要去哪里寻找verilog文件,这样就可以省略.v文件前面的路径。

read_verilog MYREG_mapped.v //只要已经在search_path中指定之前的路径,就不需要在命令中打出来

search_path = " .<Install_dir>/libraries/syn" //这里的小数点代表__启动DC__的目录

搜索路径的顺序(1)cwd 即启动软件的目录(2)search_path中列举的目录

读入RTL级代码

- read_verilog

用read_verilog 读入.v文件之后使用current_design 确定当前所在的层级(hierarchy)

check_design可以帮助再次检查代码,例如(1)还存在没有连接的输入或者端口确实(2)存在递归结构或者重复的例化;若返回0则表明代码还存在问题,返回1表明可以进行综合。

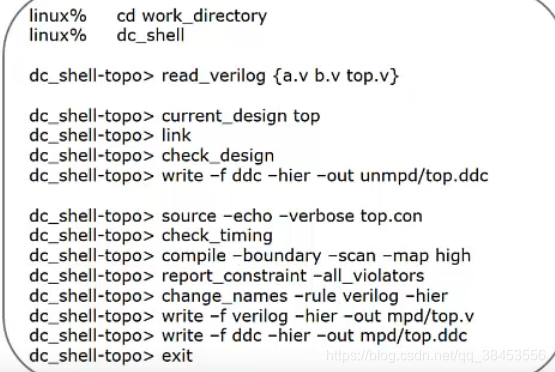

//向DC载入RTL级代码的过程

dc_shell-topo> read_verilog {A.v B.v TOP.v}

dc_shell-topo> current_design MY_TOP

dc_shell-topo> link

dc_shell-topo> check_design

dc_shell-topo> source TOP.con

- analyze&elaborate

另外还有用analyze&elaborate的方式,这种方式不需要current_design或者link命令

-format还支持vhdl和SV,但是 并非所有SV语言都可以综合

dc_shell-topo> analyze -format verilog {A.v TOP.v}

dc_shell-topo> elaborate MY_TOP

analyze命令将读入文件转化为.pvl文件,elborate命令再用GTECH格式表示这个.pvl文件

elaborate命令不仅可以指定顶层,还可以用-parameters选项指定参数值,覆盖module中的默认参数值。

dc_shell-topo> elaborate MY_TOP -parameters "A_WIDTH=9, B_WIDTH=16"

- 保存ddc文件

link(elaborate)后编译前,及时保存由GTECH写成的ddc文件可以避免浪费时间二次操作,但是一定要记得一旦源文件被修改,.ddc文件也要重新综合生成

dc_shell> write -format ddc -hier -output unmpad/MY_TOP.ddc

DC综合是基于path完成的,所以电路图中的每一条路径都必须要有相应的约束条件。

注:此编译非vcs中对verilog文件的编译。

编译完成之后同样需要保存ddc文件以供后端使用,命令顺序如下所示:

dc_shell> link

dc_shell> check_design

dc_shell> write -format ddc -hier -output unmapd/MY_TOP.ddc

dc_shell> source TOP.con

dc_shell> check_timing

dc_shell> compile_ultra

dc_shell> change_names -rule verilog -hier

dc_shell> write -format verilog -hier -output mapd/MY_TOP._net.v //提供给非synopsys的后端软件使用

dc_shell> write -format ddc -hier -outpu mapd/MY_TOP.ddc //提供给支持synopsys格式的后端软件使用

实例

read_verilog -rtl [list top.v fsm_moore.v counter.v]

这里的 [list] 表示,将list后面的每一个对象都交给前面的命令和选项去完成,相当于把相同的命令压缩在了一起。

list_libs

这个命令可以列出所有库的名字、对应文件和路径。

report_lib [库的名字]

再用以上命令可以显示指定库的具体内容。

如果想不起来某个命令的用处可以用以下选项

[命令] -help

man [命令]

DC载入代码文件之后可以用 list_designs 显示所有已经读入的设计文件,后面带有星号 (*) 表明这是用户当前所在的设计文件。

注意:只有top层和top层所含的子模块会被综合,因此综合之前要确定自己所在的位置。