2018-2019-1 20175314 《信息安全系统设计基础》第4周学习总结

教材学习内容总结

- ISA:一个处理器支持的指令和指令的字节级编码称为它的指令集体系结构。不同的处理器具有不同的ISA。

- 冒险:一条指令的位置或操作数依赖于其他仍在流水线中的指令。

- Y86-64有15个程序寄存器,其中%rsp被入栈、出栈、调用和返回指令座位栈指针,标志位ZF、SF、OF保存着最近的算数或逻辑指令所造成影响的有关信息。

- Y84-64只包括8字节整数操作。指令的字节级编码需要1~10个字节不等,每条指令的第一个字节表明指令的类型,这个地接的高四位是代码部分,低4位是功能部分。

- Y84-64的一些基本指令见课本P246,同IA32一样,其采用小段法编码。

- 指令集的一个重要性质就是字节编码必须有唯一的解释。

- Stat是程序员可见的状态:①AOK,正常操作;②HLT,遇到器质性halt指令;③ADR,遇到非法地址;④INS:遇到非法指令。遇到异常时,中止程序或者调用一个用户自定义的信号处理程序。

- pushq指令会把栈指针减8,并且讲一个寄存器的值写入内存中。但是当执行pushq %rsp指令时,处理器的行为是不确定的,因为要入栈的寄存器会被同一指令修改。

- 将很多的逻辑门组合成为一个网:①两个或者以上逻辑门的输出不能连在一起;②这个网必须是无环;③每个逻辑门的输入必须连接到一个系统输入或某个存储器单元的输出或者某个逻辑门的输出。

- 组合电路从本质上讲是不存储任何信息的。为了产生时序电路,必须引入按位存储信息的设备。存储设备都是由同一时钟控制的。

- 实现所有Y6-64指令所需要的计算可以被组织成6个基本阶段:取指、译码、执行、访问、写回、更新PC。

- SEQ的实现包括组合逻辑和两种存储器设备:时钟寄存器和随机访问存储器。

- 处理器遵循“从不回读”的原则,从来不需要为了完成一条指令的执行而去读由该指令更新了的状态,解决了类似pushq %rsq会造成“歧义”的情况。

- 通过将执行每条不同指令所需的步骤组织成一个统一的流程,就可以用少量的各种硬件单元以及一个时钟来控制计算的顺序,从而实现整个处理器。SEQ存在的问题是速度太慢,时钟必须非常慢从而来让一个信号能够在一个周期内传播所有的截断。

- 在命名系统中,大写的前缀指的是流水线寄存器,小写的前缀指的是流水线阶段。

- 猜测分支方向并根据猜测开始取指的技术称为分支预测。所有的处理器都采用了某种形式的此类技术。

- 流水线冒险可以分为两类:数据冒险和控制冒险,先考虑前者再考虑后者。

代码调试中的问题和解决过程

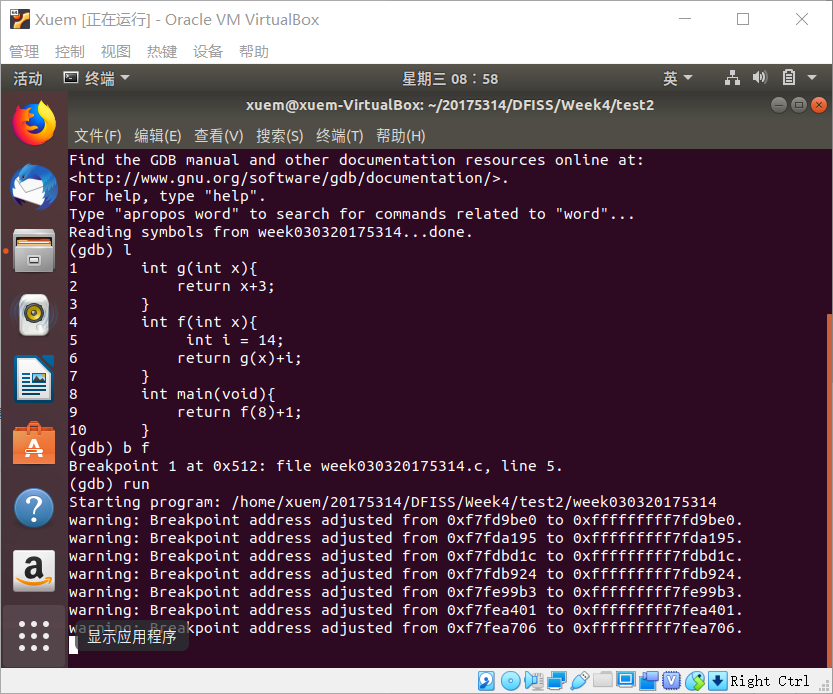

- 问题:使用32位编码后run会出现多个warning且无法继续

- 解决方法:更新jdb修复bug:

wget http://ftp.gnu.org/gnu/gdb/gdb-8.3.tar.xz

tar -xf gdb-8.3.tar.xz

cd gdb-8.3/

./configure

make

sudo cp gdb/gdb /usr/local/bin/gdb代码托管

感想心得

本周课堂测试较多,但是只要在课前做好充分的准备,还是可以保质保量地完成,虽然第一个测试因为电脑问题晚了两分钟才提交,但是后面的测试都顺利完成,体现了努力就会有看得见的成果。

学习进度条

| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | 重要成长 | |

|---|---|---|---|---|

| 目标 | 5000行 | 30篇 | 400小时 | |

| 第一周 | 200/200 | 1/1 | 20/20 | |

| 第二周 | 300/500 | 1/1 | 10/15 | |

| 第三周 | 200/500 | 1/1 | 10/12 | |

| 第四周 | 500/500 | 1/1 | 12/12 |

计划学习时间:12小时

实际学习时间:12小时