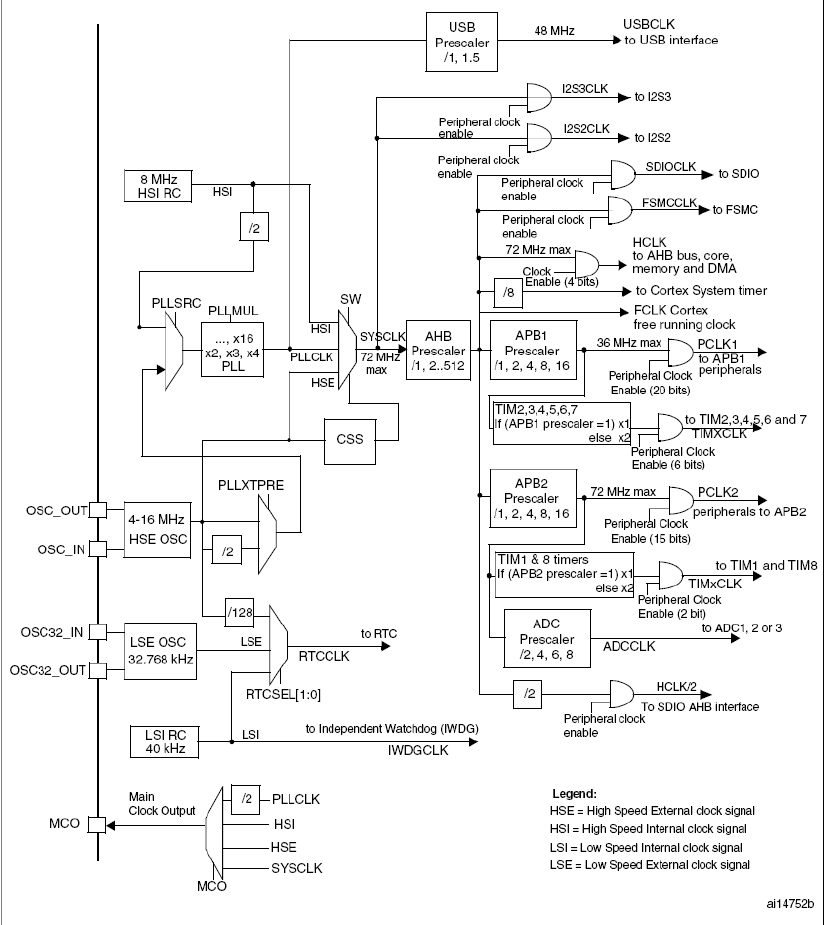

如图1:时钟树,可见Stm32有5个时钟源。

8M HSI RC:内部时钟,从图上看,有两路分支,一个是直接作为系统时钟SYSCLK使用,另一个是先二分频后,再通过PLLMUL倍频作为系统时钟SYSCLK

4-16M HSE OSC:外部晶振作为时钟源,可以看做有3路分支,第一是直接作为系统时钟SYSCLK使用,第二个通过PLL倍频后作为系统时钟SYSCLK,第三个是128分频后作为RTC时钟输入

32.768kHz LSE OSC:低速外部时钟源,可直接用作RTC时钟输入

40kHz LSI RC:低速内部时钟源,有两路分支,一个用作RTC时钟,一个用作看门狗时钟

PLLCLK:可以直接看做倍频器,也不能说得上是时钟源,和以上某些时钟源配合使用,配置系统时钟

掌握以上几个之后,直接看图就很容易配置相应的时钟源了

一下以外部晶振8M通过倍频作为系统时钟使用

Stm32时钟设置如图:假如我们要设置PPL倍频后的时钟作为系统时钟。首先,PLL时钟来自两个地方,一个是来自HSI2分频得到,一个是来自HSE直接或者2分频得到。我们用HSE作为PLL输入源的话,则必须先使能HSE时钟源,通过设置PLLXTPRE设置是否二分频输入。接着,既然选择HSE为PLL输入源,怎必须设置相应寄存器把HSE作为PLL时钟输入。再就是设置倍频PLLMUL位,把频率上升到需要的频率,注意最大频率不能超过72MHz。最后设置AHB等分频,供给系统外设。

图1:时钟树

系统时钟设置函数如下:

1 void SYSCLK_Init(u8 PLLMUL)//PLL倍频值 2 { 3 RCC->CR|=1<<16;//HSEON=1 时钟使能 4 while(RCC->CR&(1<<17)==0);//等待外部时钟就绪 5 6 RCC->CFGR|=0X00000400; 7 8 RCC->CFGR&=~(1<<17);//HSE不分频 9 RCC->CFGR|=1<<16;// 设置HSE作为PLL时钟源 10 FLASH->ACR|=0x32;//FLASH 2个延时周期 注意:这里必须有,否则设置不成功 11 12 RCC->CFGR|=(PLLMUL-2)<<18;//9倍频 13 14 RCC->CFGR&=0xffffff0c;//AHB不分频 15 RCC->CFGR|=0x00000002;//PLL作为系统时钟 16 17 RCC->CR|=1<<24;//enable pll 18 while((RCC->CR&1<<25)==0);//pll ready 19 }

有什么错误的请指正,多点交流,共同进步...

转载于:https://www.cnblogs.com/skeyzero/p/3181261.html