目录

相比于51来说,STM32F4的时钟比较难一点,我也是没想到,都有时钟树这种东西出来了,并且还有5个时钟,不过好在以前有51的基础,学习起来稍微轻松一点,就是要自己配置许多的东西和了解以及使用不同的时钟,个人觉得正点原子的课程讲的有点乱,所以这是我自己整理之后的笔记,按照每一个时钟的输入输出来解释,希望听不懂课程的同学可以理解。

接下来我们就来看一看时钟树吧,我是按照从上往下的顺序来一一讲解的!

梯形是选择器,是给不同外设选择时钟源用的。

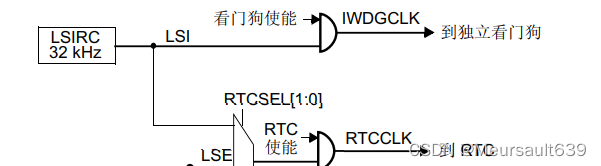

LSI时钟

第一个就是我们的LSI时钟,LSI RC 可作为低功耗时钟源在停机和待机模式下保持运行。时钟频率在 32 kHz 左右。

LSI RC 可通过 RCC 时钟控制(因为是时钟控制的,就没有那么标准)和状态寄存器 (RCC_CSR) 中的 LSION 位打开或关闭。 RCC 时钟控制和状态寄存器 (RCC_CSR) 中的 LSIRDY 标志指示低速内部振荡器是否稳定。 在启动时,硬件将此位置 1 后,此时钟才可以使用。如在 RCC 时钟中断寄存器 (RCC_CIR) 中 使能中断,则可产生中断。

输出

供独立看门狗 (一般都是这个用法) 或RTC选择器使用。

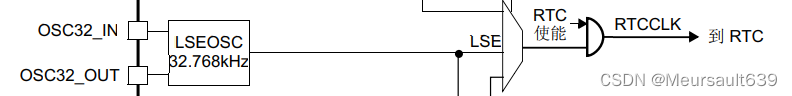

LSE时钟

第二个是LSE时钟,LSE 晶振是 32.768 kHz 低速外部 (LSE) 晶振或陶瓷谐振器,可作为实时时钟外设 (RTC) 的 时钟源来提供时钟/日历或其它定时功能,具有功耗低且精度高的优点。

输出

LSE时钟主要是供RTC选择器使用。

输入

然后它可以接外部的时钟,但必须使用占空比约为 50% 的外部时钟信号(方波、正弦波或三角波)来驱动 OSC32_IN 引脚,同时 OSC32_OUT 引脚 应保持为高阻态 (Hi-Z)。如下图所示。

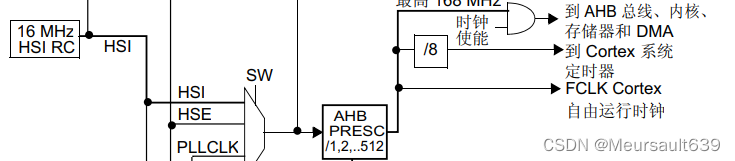

HSI时钟

第三个是HSI时钟,HSI 时钟信号由内部 16 MHz RC 振荡器生成,直可接用作系统时钟,或者用作 PLL 输入。 HSI RC 振荡器的优点是成本较低(无需使用外部组件)。此外,其启动速度也要比 HSE 晶振块,但即使校准后,其精度也不及外部晶振或陶瓷谐振器

输出

- 可以通过分频器供MCO1(PA8)引脚输出时钟。

- 可接用作系统时钟。

- 还可用作 PLL 输入(后面介绍)。

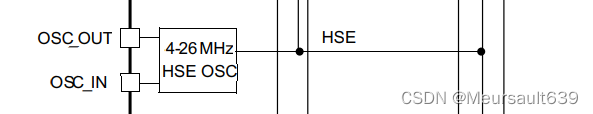

HSE时钟

第四个是HSE时钟 ,LSE 晶振是 32.768 kHz 低速外部 (LSE) 晶振或陶瓷谐振器,可作为实时时钟外设 (RTC) 的 时钟源来提供时钟/日历或其它定时功能,具有功耗低且精度高的优点。可接4~26MHz的晶振,正点原子开发板接的晶振是8MHz的晶振。

输出

- 可以供RTC选择器使用。

- 可以通过两个分频器供MCO1(PA8)以及MCO2(PC9)引脚输出时钟。

- 还可用作 PLL 输入。

输入

正点原子开发板接的晶振是8MHz的晶振,然后和上面LSE时钟是一样的,只不过LSE时钟是固定频率。

PLL时钟

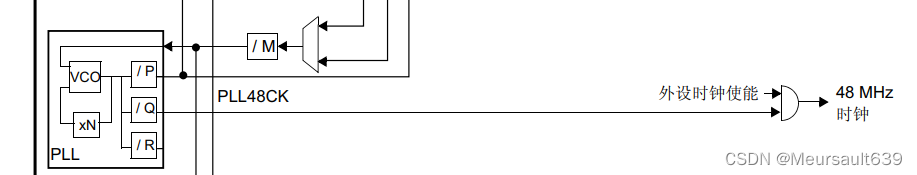

PLL有两个,分为主PLL和专用PLL,有许多分频器,计算的时候要注意(锁相环倍频输出),接下来我们一一进行介绍:

主PLL

主 PLL (PLL) 由 HSE 或 HSI 振荡器提供时钟信号,并具有不同的输出时钟:

- 可以输出用于生成高速系统时钟(最高达 168 MHz)

- 可以通过两个分频器供MCO1(PA8)以及MCO2(PC9)引脚输出时钟。

输入

主要由PLL分频器提供,来自于HSI和HSE时钟。

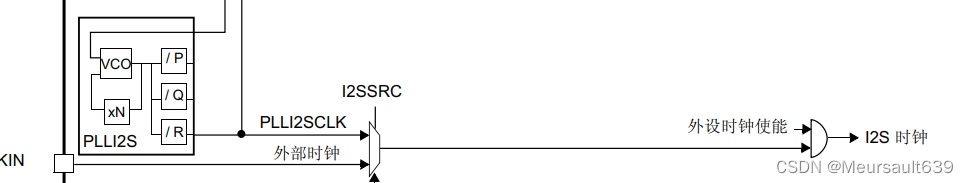

专用 PLL

输出

用于生成精确时钟,从而在 I2S 接口实现高品质音频性能

输入

和主PLL一样的

PLL时钟频率计算

例如我们的外部晶振选择 8MHz。同时我们设置相应的分频器 M=8,倍频器倍频系数 N=336, 分频器分频系数 P=2,那么主 PLL 生成的第一个输出高速时钟 PLLP 为:

PLL=8MHz * N/ (M*P)=8MHz* 336 /(8*2) = 168MHz

如果我们选择HSE为PLL时钟源,同时SYSCLK时钟源为PLL,那么SYSCLK时钟为 168MHz。 这对于我们后面的实验都是采用这样的配置。

系统时钟

输入

- HSE

- HSI

- PLL

输出

就是接着不同的外设,需要的时候找就行了

RCC寄存器

就介绍一点点,后面的可以去查以及配置。

RCC_CR

主要用来使能和就绪一些时钟,具体可以看原理图,用到了再查阅就不一一介绍。

RCC_PLLCFGR

主要用来控制PLL里的分频。

RCC_CFGR

主要用来时钟源的选择和部分分频器的选择。