1、前言

新项目中打算对现有的TMS320C6455+Kintex7 FPGA平台进行升级,采用TMS320C6657作为新核心,主要考虑到几点点:

1)具备DDR3接口,可以更加方便的移植图像处理算法,不再受片上L2空间大小的限制;

2)双核DSP,可实现更多的功能;

3)与C6455相比为新一代工艺,能耗比更高。

本文主要包含了硬件设计过程中的几个tips。

2、tips 1 : Flash

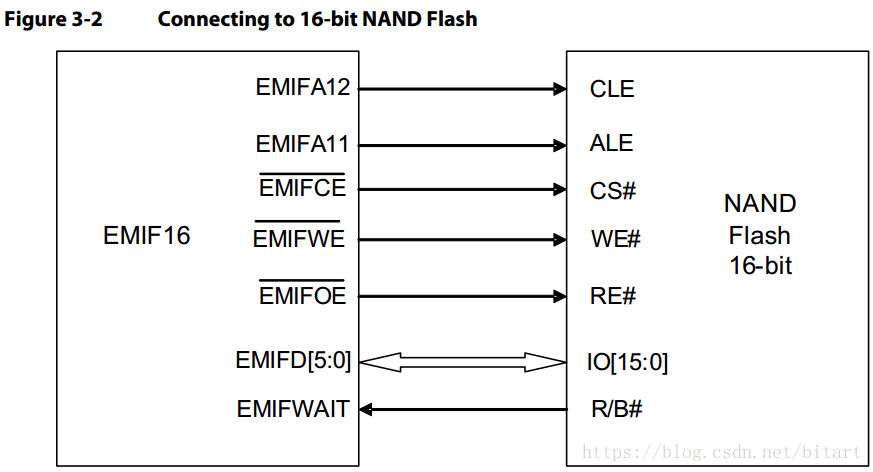

EMIF16是C6657的外部存储器控制接口,可以实现与多种异步存储器如ASRAM,NOR FLASH和NAND FLASH存储器的无缝连接,它只有异步传输模式。C6657的EMIF16接口数据位宽为16bit,地址位宽为24bit,片选CE0~CE4。

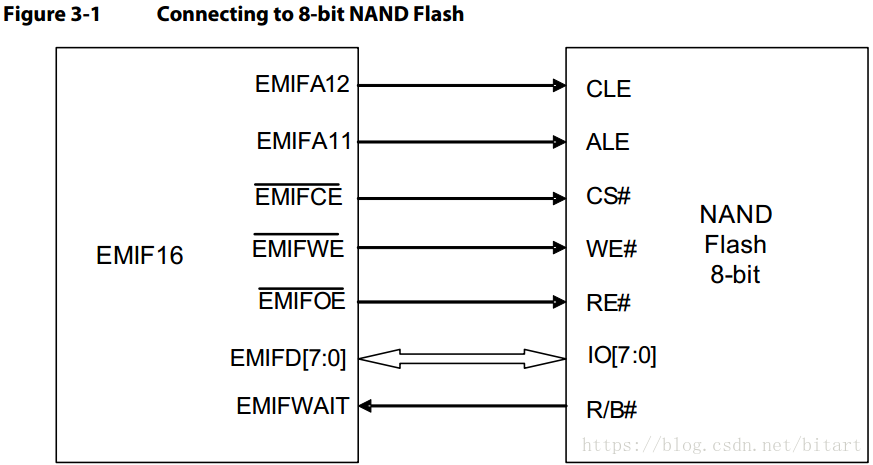

1)若选择NAND Flash作为程序存储器,由于8/16bit的IO口可复用为数据/地址/命令的传输通道,不仅能减少PIN的数量,而且在不同容量的器件之间可以保证接口的兼容,对存储容量进行升级时无需更改设计。8bit和16bit的连接方式如下:

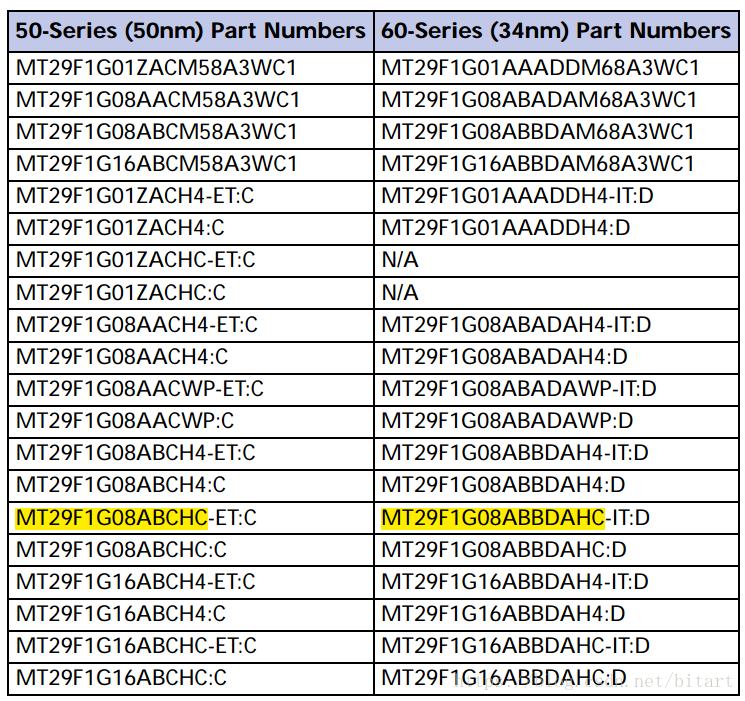

NAND Flash的型号常于Micron公司生产的 SLC NAND Flash Devices中选择,但不建议再使用50-series (50nm)系列器件,而应该从60-series (34nm)系列器件中选择需要的容量,在工艺、ECC功能、支持的命令、性能等表现方面,60系列均比50系列有所提升。若参考EVM板进行原理图设计,则注意对其板载NAND FLASH的型号更新如下:

2) Nor Flash

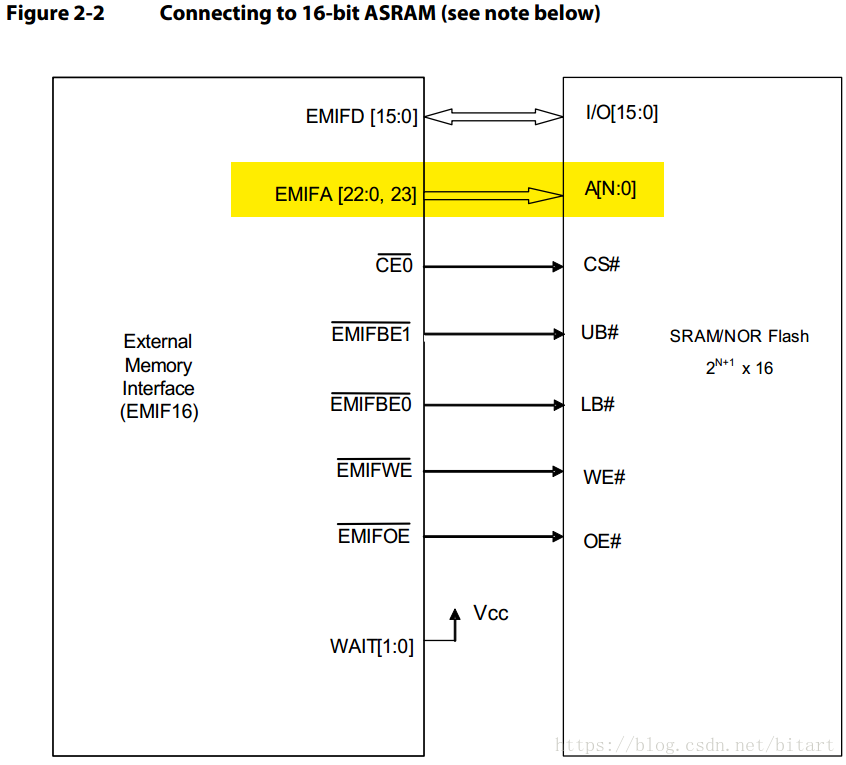

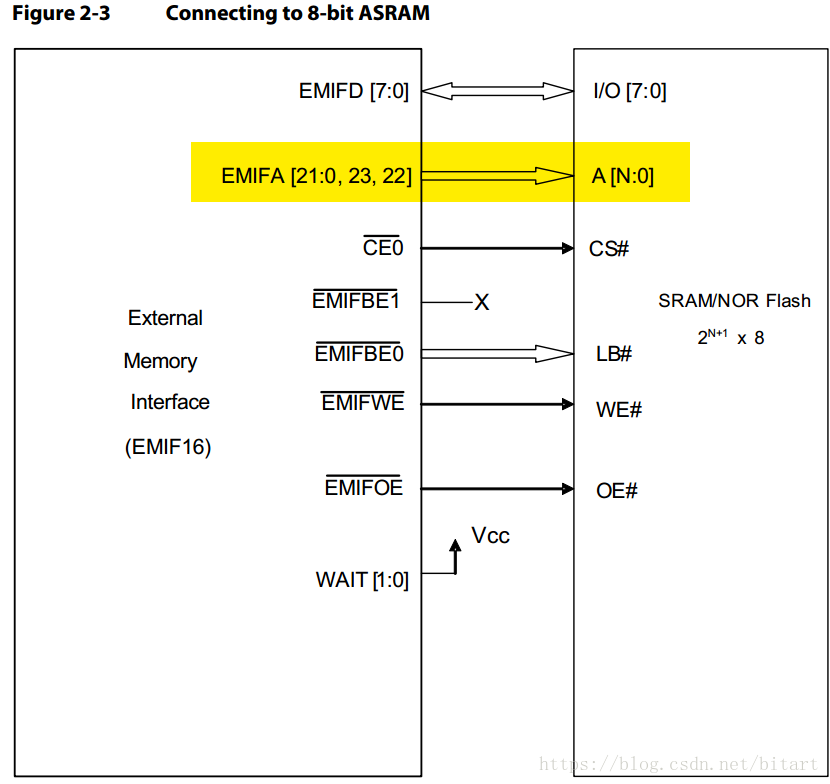

采用Nor Flash时,需要注意EMIFA信号与NorFlash地址信号的连接顺序,8bit/16bit模式各不相同,对于16bit模式,EMIFA23应该连接到NorFlash的A0;而对于8bit模式,EMIFA[23:22] 连接到Nor Flash的A[1:0],如下图所示。数据线是否有顺序要求,参考所采用的Flash Datasheet。

3、tips 2:boot configuration

C6657的boot配置由GPIO[15:0]来控制,常规的做法是设置Pull Up/Pull Down电阻构成配置矩阵,通过选择性焊接的方式来设置启动方式。缺点是需要占用一定的PCB面积。

本次设计的板卡中包含一片Artix 7系列FPGA,用户IO 250个,将DSP的GPIO[15:0]连接到FPGA的未用IO上,由FPGA来控制DSP的启动模式。这种方式有两个要点:

1)FPGA的BANK必须为1.8V,否则需要添加电平转换芯片;

2)DSP的POR在deassert时,一定要保证FPGA已经加载完毕且给出正确的GPIO配置值,否则DSP无法正常启动。这里可以通过“与门”芯片级联成整板的复位链实现,即级联关系:

PWR GOOD ---> FPGA boot complete ---> FPGA working --->DSP POR deassert;

或者由FPGA统一控制整板芯片的复位时序关系。

4、tips 3:时钟电路

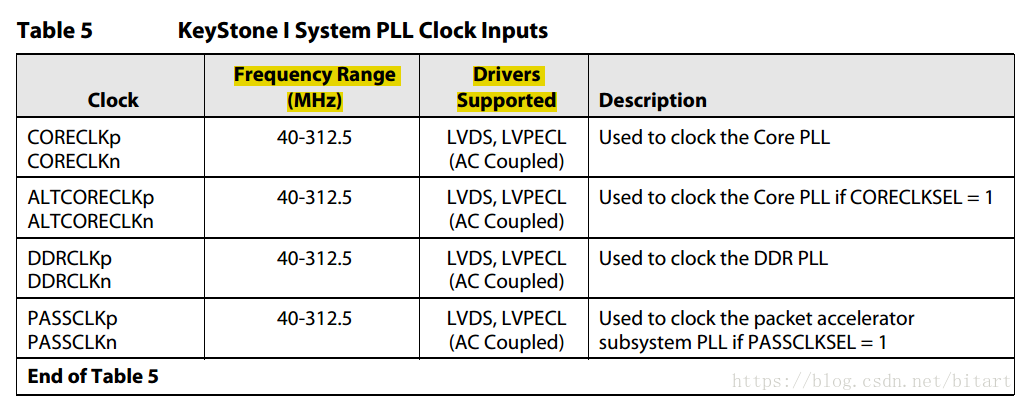

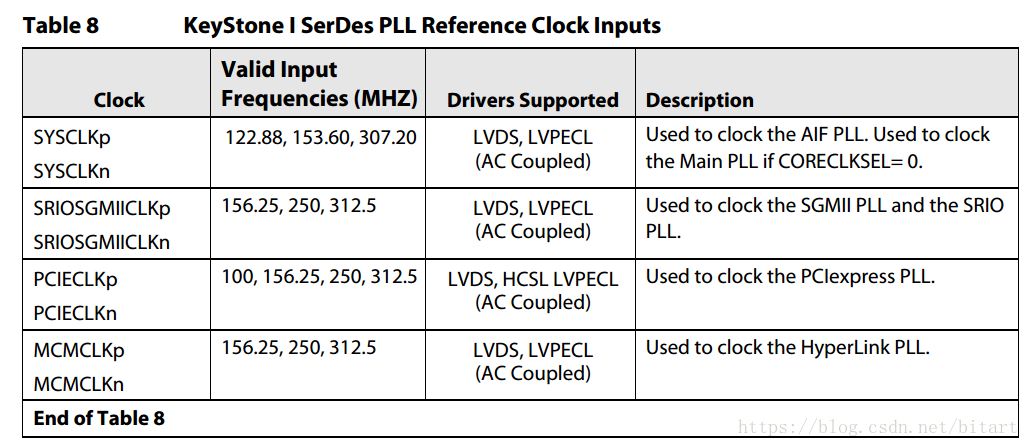

C6657支持的时钟输入频率范围以及类型如下:

1)C6657内置了并联终端电阻100Ω,因此必须采用AC耦合的方式。

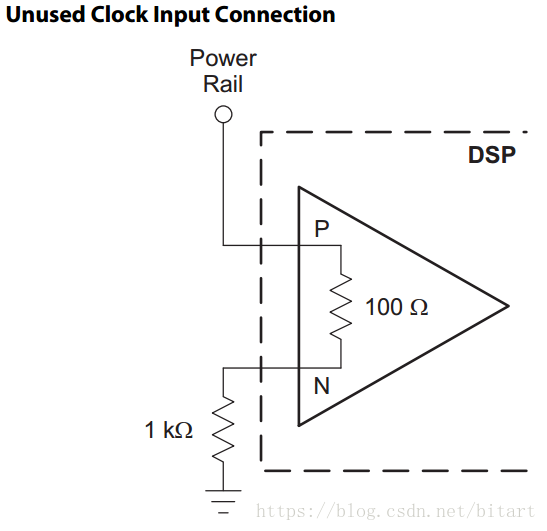

2)对于未采用的时钟输入引脚的处理方式:连接到合适的电源轨道以保证稳定的电压。官方推荐增加1k的下拉电阻以降低功耗,如下图:

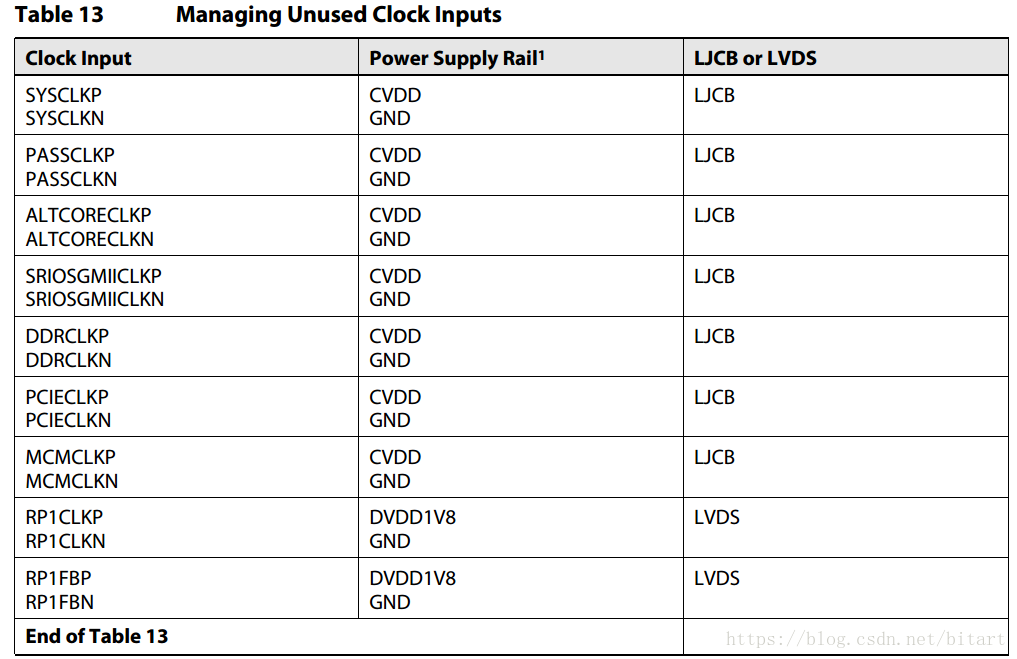

可以连接的电源如下:

3)AC耦合电容尽可能靠近DSP端放置;

4)要求POR拉高之前,时钟有效;但是在CVDD有效之前,时钟端必须为高阻态。

5、tips 4:启动配置和初始化

GPIO[0:15]的用来配置系统的启动方式,一般采用上拉/下拉电阻或者FPGA对其进行设置,根据器件内部默认上下拉的配置不同,外部的电阻容量也是不同的:若外部拉电平与内部默认拉电平相同,则采用4.7k电阻;否则,采用1k电阻;根据器件手册,只有GPIO[0]是内部上拉,GPIO[1:15]都是内部下拉的,因此,对于GPIO[0]而言,外部上拉时采用4.7k,下拉采用1k;而对于GPIO[1:15]而言,外部上拉需要1k电阻,下拉需要4.7k电阻。

启动模式和其它器件配置在RESETFULL引脚的上升沿被锁存。当这些引脚的电平值被锁存到配置寄存器后,这些引脚即可用作用户IO。

6、tips 5:复位顺序

1)POR:

- 上电过程中以及时钟有效之前必须持续为低,此时,几乎所有的输出都为Hi-Z状态。

- RESET先于POR释放;

- POR内部电路无法检测电源系统的有效性,因此在释放POR之前,一定要保证电源正常。

- 一般采用电压监视电路,检测到DSP电源失效后,拉低POR,以免过流烧毁器件。

2)ResetFull

用于复位内部的配置寄存器到默认值,功能与POR类似。要求ResetFull滞后于POR/RESET释放。而当POR被拉低时,要求RESERFULL同时被拉低。

3)Reset

Reset并不会锁存boot配置以及其它配置,也不会复位内部已经锁存的相关数据。

7、tips 6:关于SmartReflex

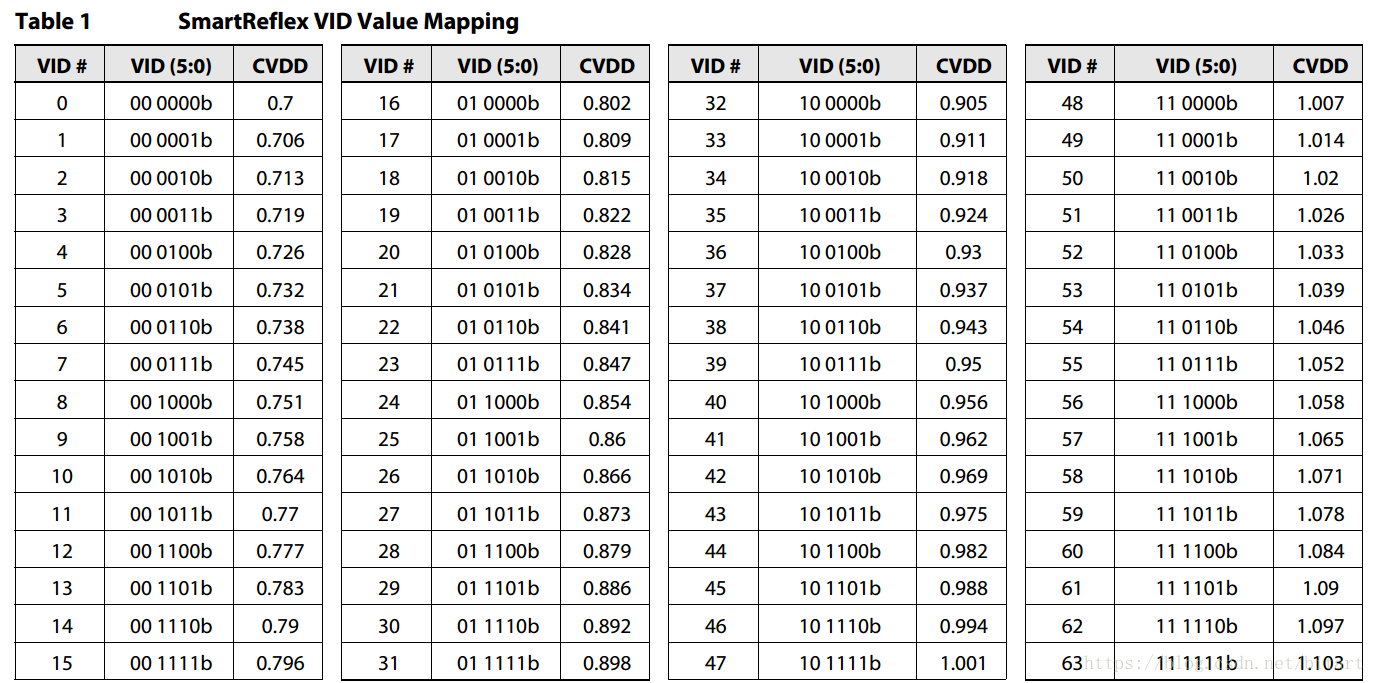

对于C6657这一类KeyStone器件而言,CVDD是可调的,CVDD的实际电压值可在一定范围内变化,并且每个器件都是不同的,因此对于CVDD的供电,必须使用SmartReflex-compliant电路。初始时被设定为1.1V,然后被SmartRefex电路调整到器件所需的值。

每个器件由制造商进行的生产测试确定了一套编码用于标识理想电压值:

测试结束后,器件可接受的最低电压对应的编码被永久性的写入到器件中,这个6bit的编码,称作VID(Voltage Identification)值,代表着该器件的最优化电压。

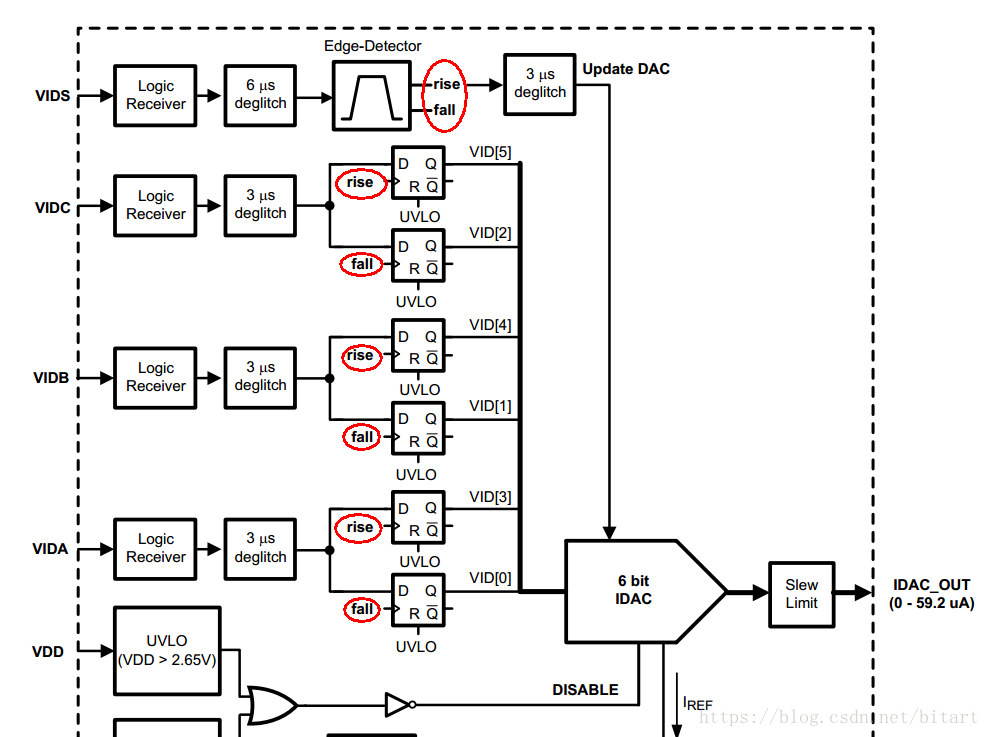

每个器件的VCNTL[3:0]引脚用于传输6bit编码至SmartReflex电路中,这组引脚为OD输出,需要接4.7k上拉电阻至DVDD1V8。注意:this transition will occur only a single time after a power-up reset has occurred.关于其详细描述如下:

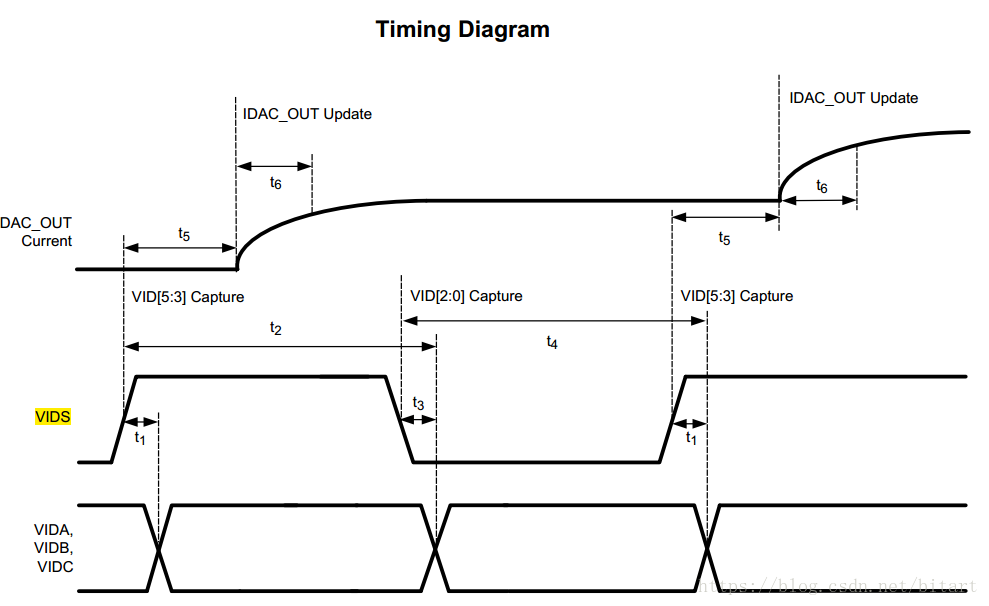

The falling edge of VIDS latches in the data from VIDC, VIDB, and VIDA as the lower three LSB of the IDAC value. After a

minimum hold time, the rising edge of VIDS latches in the data from VIDC, VIDB, and VIDA as the upper three LSB of the IDAC value . Four pins are used to communicate with the LM10010. VIDC, VIDB, and VIDA are data lines, while VIDS is a latching strobe that programs in the LM10010 data. As shown in the Timing Diagram in Figure 2, the falling edge of VIDS latches in the data from VIDC, VIDB, and VIDA as the lower three LSB of the IDAC value. After a minimum hold time, the rising edge of VIDS latches in the data from VIDC, VIDB, and VIDA as the upper three LSB of the IDAC value. Internally, a delay on VIDS allows for the setting of all VID lines simultaneously.The VID data word is set so that the lowest output current is seen at the highest VID data word (59.2 µA at a code of 0d). Conversely, the lowest current is seen at the highest VID data word (0 µA at 63d). During VID operation with the regulator, this will translate to the lowest output voltage with the lowest VID word, and the highest output voltage with the highest VID word. The communications pins can be used with a low voltage microcontroller, with a maximum VIL of 0.4V and a minimum VIH of 1.1V. Upon startup, the IDAC is set at a code of 46d, which translates to approximately 16 µA. This default startupvalue is trimmed at final test.

总结:具备了电源、时钟、正确的复位顺序以及FLASH之后,C6657就具备了正常工作的环境,可连接仿真器进行调试。其它外设根据系统的需求进行增加即可。在图像处理系统中,一般还需要添加一组DDR3作为图像缓存,并打开SRIO接口作为图像的输入与输出端口。到此,基本完成了以DSP为运算核心的板卡设计。