1 Cameralink概述

CameraLink是从Channel link技术上发展而来的,基于视频应用发展而来的通信接口,在机器视觉系统中广泛应用。2000年10月美国NI、摄像头供应商和其他图像采集公司联合推出了CameraLink协议,CameraLink协议是一个工业高速串口数据和连接标准,旨简化图像采集接口,方便高速数字相机和数据采集卡的连接。

2 采集接口与信号说明

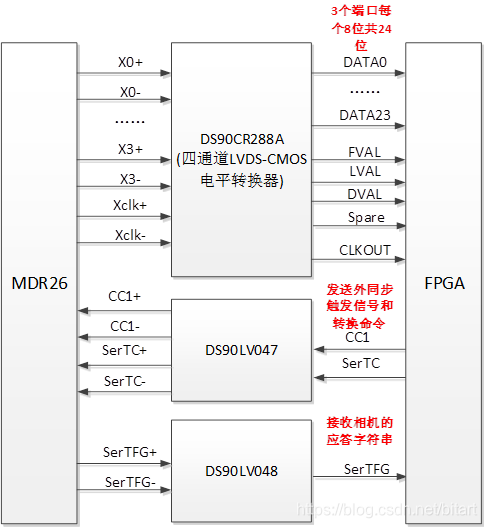

基本采集单元如上图所示。一条Cameralink电缆可以连接至一个MDR26连接器,其中包含了数据信号x0~x3,时钟信号xclk,CC控制信号、相机通信信号TC、TFG等。

2.1 图像数据

如果仅仅接收工业相机的图像,则只需要连接288A芯片即可。经过288A芯片的解码后,输出为28bits的并行数据信号、四个使能信号以及一个源同步时钟信号。其中四个使能信号的定义如下:

- FVAL—Frame Valid (FVAL) is defined HIGH for valid lines.

- LVAL—Line Valid (LVAL) is defined HIGH for valid pixels.

- DVAL—Data Valid (DVAL) is defined HIGH when data is valid.

- Spare— A spare has been defined for future use.

2.2 控制数据

保留的4路LVDS pairs用于相机控制,由camera厂商自己定义,具体功能需查询所用相机的数据手册。包括;

- Camera Control 1 (CC1)

- Camera Control 2 (CC2)

- Camera Control 3 (CC3)

- Camera Control 4 (CC4)

2.3 通信

一般来讲,相机厂家会预留通信协议,用于相机功能参数的设置,因此在Cameralink中,存在两个LVDS pairs用于camera和grabber的通信。

- SerTFG—Differential pair with serial communications to the frame grabber.

- SerTC—Differential pair with serial communications to the camera.

要求:一个起始位、一个停止位、无奇偶校验位。波特率需查询相机手册。

3 关于Taps配置的示意图

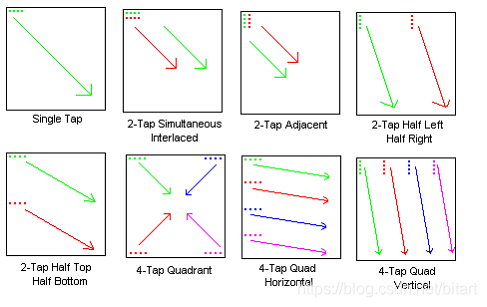

不同的相机采用不同的传输数据的方式,关于一些Cameralink协议上的术语可参考下图理解:single、interlaced、adjacent等。最常见数据传输顺序为图1和图3的方式。

4 FPGA实现Camlink数据的采集

4.1 数据位映射关系

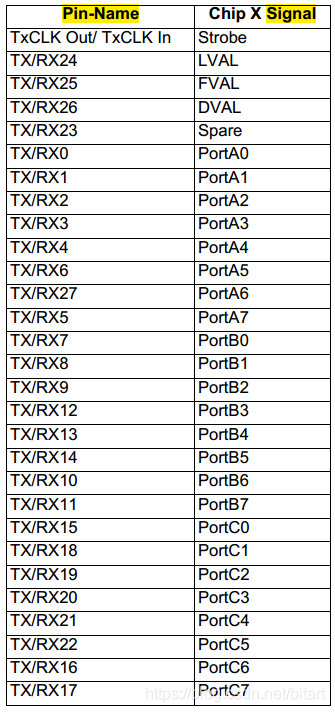

首先,在《Cameralink标准协议》的4.1章节,找到Bit Allocation,也就是DS90CR288A芯片的管脚分配与数据bit的对应关系:

wire [7:0] portA = { CR288_TX[5],

CR288_TX[27],

CR288_TX[6],

CR288_TX[4:0]};

wire [7:0] portB = { CR288_TX[11],

CR288_TX[10],

CR288_TX[14:13],

CR288_TX[12],

CR288_TX[9:7]};

wire [7:0] portC = { CR288_TX[17:16],

CR288_TX[22:18],

CR288_TX[15]};

wire fval = CR288_TX[25];

wire lval = CR288_TX[24];

wire dval = CR288_TX[26];

4.2 数据位分配

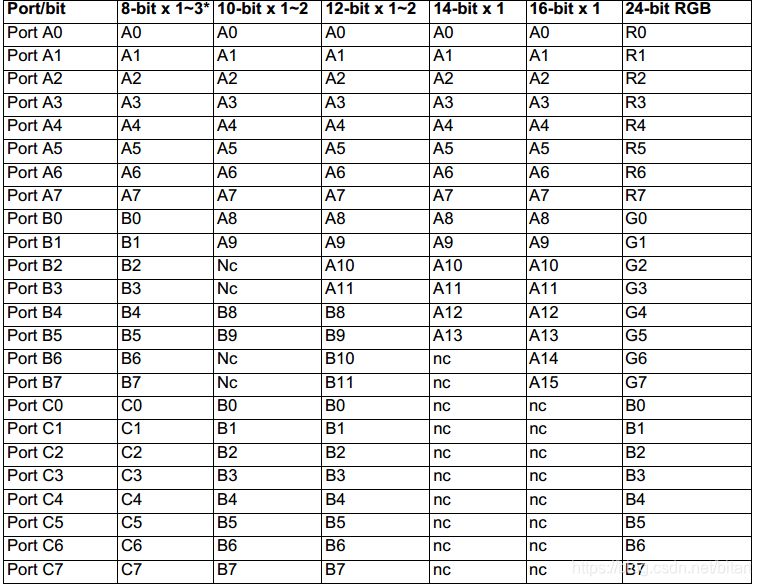

在《Cameralink标准协议》的5.1章节,找到位分配关系表:

以8bit 2Taps的相机配置为例:

reg cam_fval;

reg cam_lval;

reg [15:0] cam_data;

//

always @ (posedge cam_clk) begin

cam_fval <= fval;

cam_lval <= lval;

//cam_dval <= dval; //参考具体相机是否需要DVAL信号

cam_data[15:0] <= {portB[7:0],portA[7:0]};

end

assign fifo_wren = cam_fval & cam_lval;

assign fifo_wrdata[15:0] = cam_data[15:0];

经过FIFO之后,可将时钟转换为系统时钟,再根据FPGA系统的总体规划,将图像数据传递至DDR读写模块或直接发送给C6657 DSP的内存空间中。