作者:毛茏玮 / Saint

掘金:https://juejin.im/user/5aa1f89b6fb9a028bb18966a

微博:https://weibo.com/5458277467/profile?topnav=1&wvr=6&is_all=1

GitHub:github.com/saint-000

CSDN: https://me.csdn.net/qq_40531974

VHDL基础体会篇(四)

Part4:

1.VHDL主要描述语句:

(1)信号赋值语句

信号赋值语句包括顺序信号赋值语句和并行信号赋值语句。进程中使用顺序信号赋值语句,进程外使用并行赋值语句。

顺序信号赋值语句:一般信号赋值语句在Process内。

并行信号赋值语句:一般信号赋值语句在Process外;条件信号赋值语句;选择信号赋值语句。

①一般信号赋值语句:a<=x or y; a<=m after 2ns;

②条件信号赋值语句:

t<=a [after 10ns] when sel='0' else

b;

被赋值信号<=赋值信号1 [附加延时] when 条件表达式 else

赋值信号2 [附加延时] when 条件表达式 else

赋值信号3 [附加延时] when 条件表达式 else

赋值信号 4;

③选择信号赋值语句:

With sel select

t<=a [after 10ns] when”00” ,

b[after 10ns] when”01”or”11”,

c[after 10ns] when others;

With 条件表达式 select

被赋值信号<=赋值信号[附加延时] when条件1,

赋值信号[附加延时] when条件2,

赋值信号[附加延时] when条件3,

赋值信号[附加延时] when others;

(2)进程(Process)

①显示进程:以Process为关键字的进程。

Architecture logic of test is

Begin

p1:process(a,b,c)

Begin

y<=a and b;

z<=a xor c;

end process p1;

end logic;

[进程标号:]process(敏感信号表)

[说明]

Begin

顺序语句块;

End process [进程标号];

显示进程中用等待语句WAIT ON a,b,c;可以等同于敏感信号表的表示process(a,b,c)此处注意等待语句应放在顺序语句的最后面,防止进入语句直接挂起。

等待语句:

信号等待Wait on 信号列表; Wait on a,b,c; abc信号出现变化的时候激活进程

条件等待Wait until 条件表达式; Wait until clk=‘1’;时钟为1是激活进程

时间等待Wait for 时间表达式; Wait for 5ns;从0时刻起每隔5ns激活一次进程

Wait for clk_cycle/2; 从0时刻起每隔二分之一周期激活一次进程

无限等待Wait

②隐示进程:构造体中的每一个并发的信号赋值语句和元件调用语句都是一个隐示进程。

构造体里出现一般信号赋值语句:

Architecture logic of test is

Begin

C<=a and b; --一般信号赋值语句 process(a,b)

Y<=b when c=’0’else --条件信号赋值语句 process(b,e ,f,c)

e when c=’1’else

f;

End logic;

此时出现在构造体中的两个并发信号赋值语句可以等同于显示进程中的敏感信号表的表示方法。

(3)顺序描述语句

①顺序赋值语句:一般信号赋值语句,变量赋值语句。

②顺序控制语句:介绍两个常用的IF语句和CASE语句。

IF语句(Process里面,有优先级)

Process(sela,selb,a,b,c)

Begin

If sela=’1’ then

q<=a;

Elsif selb=’1’ then

q<=b;

Else

q<=c;

End if;

End process;

进程里的else有0个或者1个,elsif有任意个。

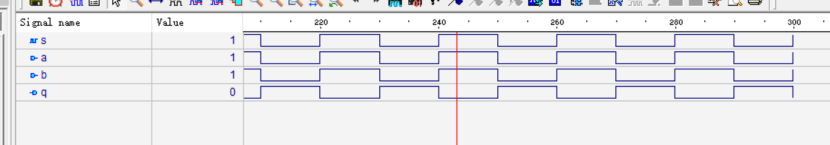

【用if语句和条件赋值语句设计优先级数据选择器】

【if语句顺序控制语句放在Process内】

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity priselector is

port(

a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

sela : in STD_LOGIC;

selb : in STD_LOGIC;

q : out STD_LOGIC

);

end priselector;

architecture behav of priselector is

begin

process(a,b,c,sela,selb)

begin

if sela='1'then

q<=a;

elsif selb='1'then

q<=b;

else

q<=c;

end if;

end process;

end behav;

【条件赋值语句】

architecture behav of priselector is

begin

q<=a when sela='1'else

b when selb='1'else

c ;

end behav;

Case语句(进程内,无优先级)

【用Case语句和选择赋值语句设计四输入数据选择器】

【case语句顺序赋值语句放在Process中】

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity selector_4 is

port(

a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

d : in STD_LOGIC;

sel : in STD_LOGIC_VECTOR(1 downto 0);

q : out STD_LOGIC

);

end selector_4;

architecture beh of selector_4 is

begin

process(a,b,c,d,sel)

begin

case sel is

when "00" =>q<=a;

when "01" =>q<=b;

when "10" =>q<=c;

when others=>q<=d;

end case;

end process;

end beh;

【选择赋值语句】

architecture beh of selector_4 is

begin

with sel select

q<=a when "00",

b when "01",

c when "10",

d when others;

end beh;

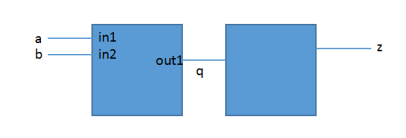

(4)结构描述语句

①元件语句(component)

元件申明:

component 元件名

[类属参数申明]

端口说明;

End component;

设计单元中的构造体中可以有多个元件申明。

元件调用:

元件实例名:元件名 port map(端口映射)

端口映射包括位置映射和名称映射

位置映射:U1:example port map(a,b,q);

名称映射:U1:example port map(in1=>a,in2=>b,out1=>q);

例:用与门作为底层设计与非门

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity nand2_gate is

port(

a : in STD_LOGIC;

b : in STD_LOGIC;

q : out STD_LOGIC

);

end nand2_gate;

architecture structure of nand2_gate is

component and2_gate

port(

in1,in2:in std_logic;

out1:out std_logic

);

end component;

signal s:std_logic;

begin

q<= not s;

U1:and2_gate port map(a,b,s);

end structure;

②生成语句(Generate)

【用生成语句设计四位移位寄存器】

四个D触发器组成四位移位寄存器。

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity dff is

port(

d : in STD_LOGIC;

clk : in STD_LOGIC;

q : out STD_LOGIC

);

end dff;

architecture rtl of dff is

begin

process(clk)

begin

if clk'event and clk='1'then

q<=d;

end if;

end process;

end rtl;

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity shift is

port(

a,clk : in STD_LOGIC;

b : out STD_LOGIC

);

end shift;

architecture structure of shift is

component dff

port(d,clk: in STD_LOGIC;

q: out STD_LOGIC

);

end component;

signal z:std_logic_vector(0 to 4);

begin

z(0)<=a;

U1:for i in 0 to 3 generate

U2:dff port map(z(i),clk,z(i+1));

end generate;

b<=z(4);

end structure;