作者:毛茏玮 / Saint

掘金:https://juejin.im/user/5aa1f89b6fb9a028bb18966a

微博:https://weibo.com/5458277467/profile?topnav=1&wvr=6&is_all=1

GitHub:github.com/saint-000

CSDN: https://me.csdn.net/qq_40531974

VHDL基础体会篇(二)

Chapter2

1.VHDL程序结构

当前设计的电路模型称为设计单元;已有的的可调用的基本逻辑门和电路模型称为元件。

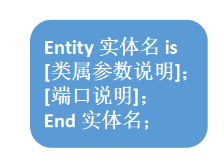

实体:描述设计单元的外围接口信号和内部参数

构造体:描述设计单元的内部结构和逻辑行为

配置:为设计单元从多个构造体中选择合适的构造体或从库中选取合适的元件,以便进行设计单元的仿真或综合。

程序包:存放各设计模块都能共享的数据类型、常数和子程序等。

库:存放已经编译好的元件和程序包。

2.实体(entity)

①类属参数说明:为用户设定指定待定参数,如定义端口宽度,器件延时。

Generic(参数名:类型:=初值);

类参数的说明一定要在端口说明之前!编译时可赋予新值,仿真和综合的时候只读。

②端口说明:设计单元与外部的接口

Port(端口名:方向 数据类型);

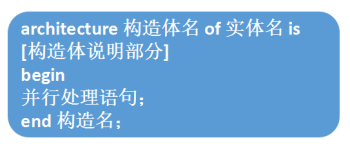

3.构造体(architecture)

①构造体说明部分:对内部信号,常数,数据类型,子程序,元件等定义说明。

②并行处理语句:使用并行语句描述设计单元的逻辑功能或结构,可以采用行为级描述behavior或者RTL和结构级描述。

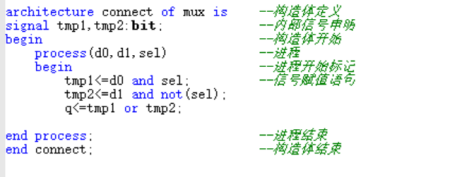

Mux设计单元:

4.VHDL描述方式:

行为级描述:五端口电路

行为级描述:五端口电路(全加器)

library ieee;

use ieee.std_logic_1164.all;

entity adder is

port(

x,y,cin:in std_logic;

sum,cout:out std_logic

);

end adder;

architecture rtl of adder is

signal s:std_logic;

begin

s<=x nor y;

sum<=s nor cin;

cout<=(x and y)or (s and cin);

end rtl;

结构级描述:五端口电路

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity adder is

port(

x : in STD_LOGIC;

y : in STD_LOGIC;

cin : in STD_LOGIC;

sum : out STD_LOGIC;

cout : out STD_LOGIC

);

end adder;

architecture structure of adder is

component half_adder

port(

a,b:in std_logic;

c,s:out std_logic

);

end component;

component or_gate

port(

in1,in2:in std_logic;

out1:out std_logic

);

end component;

signal a,b,c:std_logic;

begin

u1:half_adder port map(x,y,a,b);

u2:half_adder port map(a,cin,sum,c);

u3:or_gate port map(c,b,cout);

end structure;

5.设计:

(1)设计三输入与门

解答:用行为级描述编写

library ieee;

use ieee.std_logic_1164.all;

entity adder is

port(

x,y,cin:in std_logic;

sum,cout:out std_logic

);

end adder;

architecture rtl of adder is

signal s:std_logic;

begin

s<=x nor y;

sum<=s nor cin;

cout<=(x and y)or (s and cin);

end rtl;

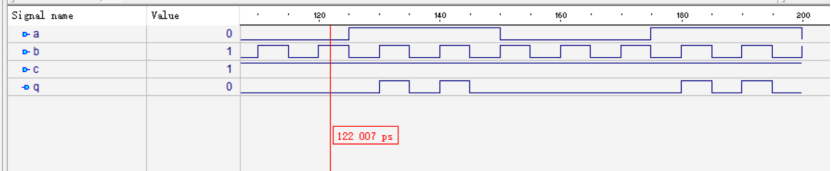

(2)设计三输入或门

解答:用行为级描述编写:改写一下q_vector即可

事实上上述两个设计可以直接用下面的方法:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity gate is

port(

a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

q : out STD_LOGIC

);

end gate;

architecture behav of gate is

begin

q<=(a or b or c);

end behav;

这种方法也是用的是行为级的描述,简洁明了,而前面提到的通过总结输入与输出的关系的方式适用于规律相对于普通门逻辑更复杂的设计,如全加器。

(3)半加器的设计【真值表暗示电路连接】

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity half_adder is

port(

a : in STD_LOGIC;

b : in STD_LOGIC;

sum : out STD_LOGIC;

cout : out STD_LOGIC

);

end half_adder;

architecture rtl of half_adder is

begin

sum<=a xor b;

cout<=a and b;

end rtl;

(4)全加器的设计

把握三种描述:behavior描述(真值表找规律,不出现逻辑门等),RTL描述(真值表推电路图),structure描述(直接描述元件连接关系)。