从本篇开始的接下来共三篇,咱们聊一聊xilinx 7系列FPGA的SelectIO。所谓SelectIO,就是I/O接口以及I/O逻辑的总称。SelectIO 篇可以分成3部分:第1部分介绍I/O的电气特性,第2部分介绍I/O逻辑资源,第3部分介绍高级的I/O逻辑资源(serializer/deserializer)。本篇咱们来说说xilinx 7系列FPGA的I/O的电气特性。

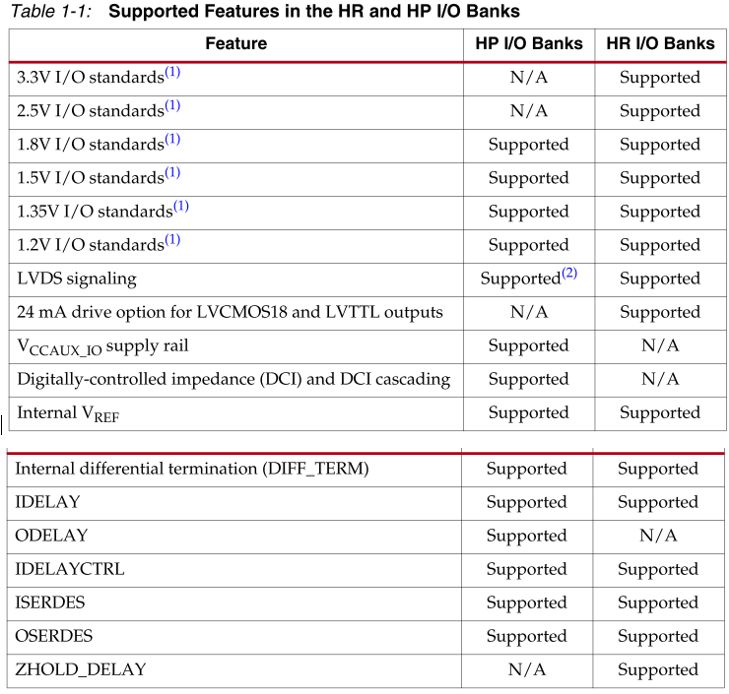

说到I/O,咱们必须先提到FPGA的BANK。在7系列的FPGA中,BANK分为HR(High-range)BANK和HP(High-performance) BANK。HP BANK只能支持小于等于1.8V电平标准的I/O信号,HR BANK则支持小于等于3.3V电平标准的I/O信号。HP BANK专为高速I/O信号设计,支持DCI(数控阻抗),而HR BANK则适合更大众化的所有I/O信号设计。下表列出了HP BANK 和HR BANK的特性。

无论是HR或者HP BNANK,每个BANK都包含50个I/O管脚,每个I/O管脚都可配置成输入、输出。每个BANK的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。

单端的I/O管脚支持LVTTL、LVCMOS、HSTL、PCI等等常用的电平标准。差分的I/O管脚则支持LVDS、差分HSTL等差分信号。但在其官方文档中,竟然没有描述支持很常用的LVPECL差分信号,甚是奇怪。如下图所示为1个I/O接口示意图(IOB):

总的来说,7系列FPGA同前几代相比,最大的区别就是:

1,多了专用于高速接口信号的HP BANK,该BANK最高只能支持1.8V电平。

2,每个BANK多达50个I/O。

其它电气性能基本保持一致,对咱们的使用不造成影响。