0.转载说明

FPGA开发,不知道所使用组件的特性,怎能开发出优秀的设计呢!!!

老早就想整理7系列FPGA的时钟结构,发现“小青菜哥哥”这位博主整理得非常棒,因此就转载整理合并过来,供大家参考,当然这篇文章基本就是点到为止,更多细节内容还需要查阅原文官方文档

7 Series FPGAs Clocking Resources User Guide。

以后有机会总结Ultrascale+系列的时钟结构,敬请期待。

原文链接:

xilinx 7系列FPGA时钟篇(1)_时钟结构简介

xilinx 7系列FPGA时钟篇(2)_时钟区域简介

xilinx 7系列FPGA时钟篇(3)_时钟操作法则

xilinx 7系列FPGA时钟篇(4)_CMT简介

原文图片均参考自

7 Series FPGAs Clocking Resources User Guide

1.时钟结构简介

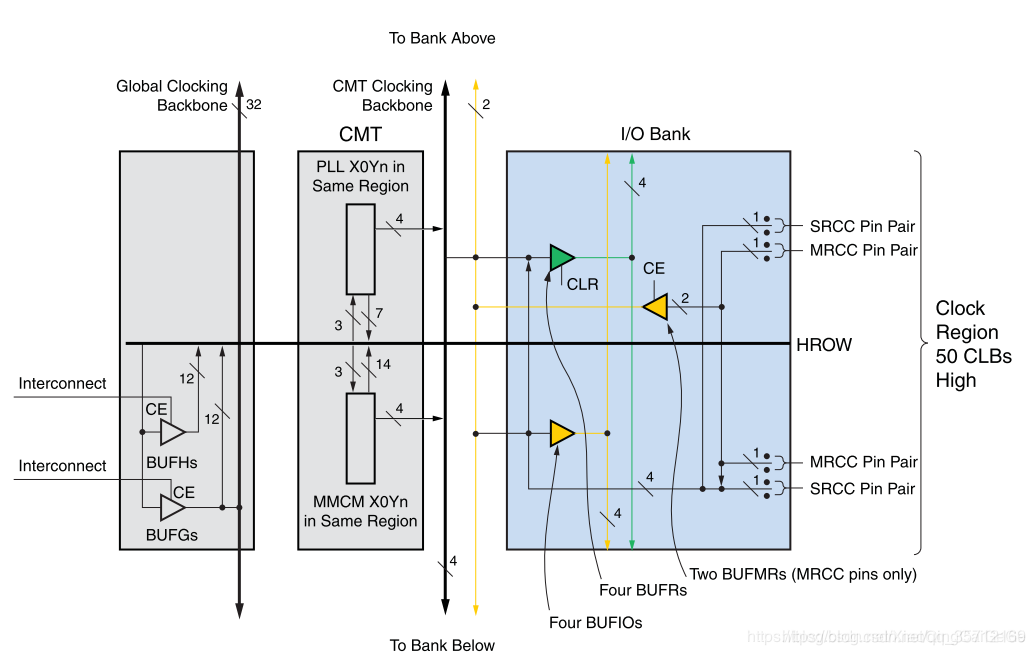

说起XILINX的FPGA时钟结构,7系列FPGA的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如图所示,理解了这张图,咱们就对7系列的FPGA时钟结构了如指掌,下面咱们就聊聊这张图:

- Clock Region:FPGA内部分成了很多个时钟区域。

- Horizontal Center:FPGA被Horizontal Center分成上下两个部分,每个部分包含16个BUFG

- Clock Backbone:全局时钟线的主干道,将FPGA分成了左右两部分,所有的全局时钟布线均要从此经过。

- HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

- I/O Column:外部信号/时钟输入管脚。

- CMT Backbone:对于相邻时钟区域的时钟布线,可以不使用珍贵的全局时钟网络,而使用每个时钟区域都包含的CMT Backbone通道。

- CMT Column:每个时钟区域都包含一个CMT,一个CMT由一个MMCM和一个PLL组成。

- GT Column:内含高速串行收发器。

总结来说,FPGA实际上就是被分成很多个大小一样时钟区域,每个时钟区域既可单独工作又可通过全局时钟Clock BackBone统一工作,同时水平相邻的时钟区域又可通过HROW来统一工作,上下相邻的时钟区域又可通过CMT Backbone统一工作。

2.时钟区域简介

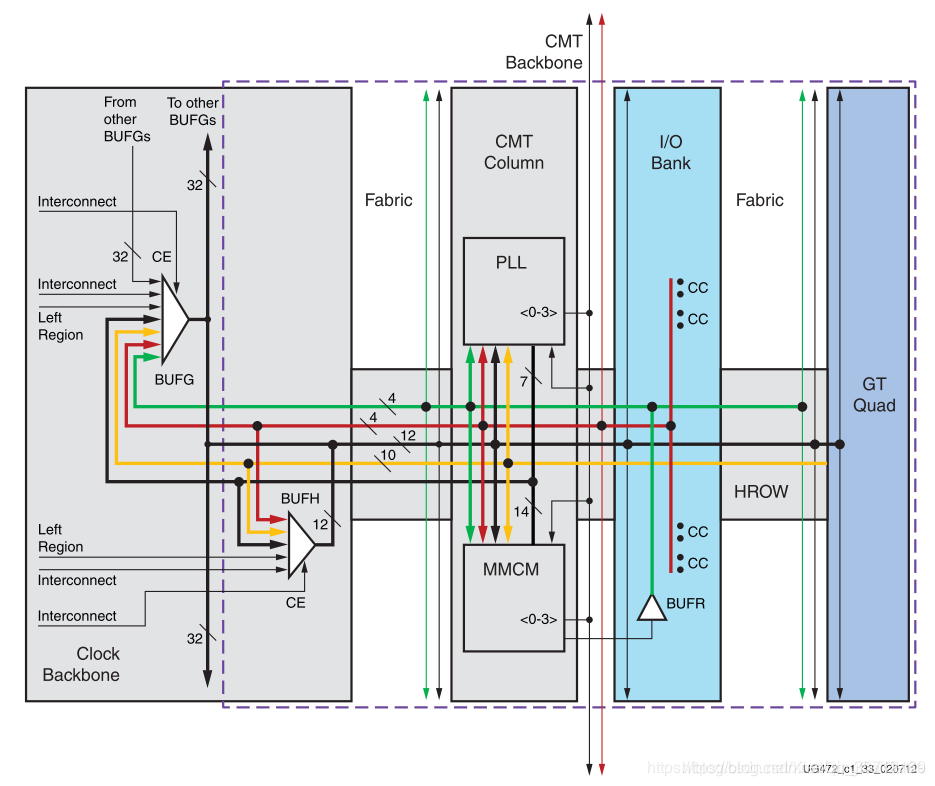

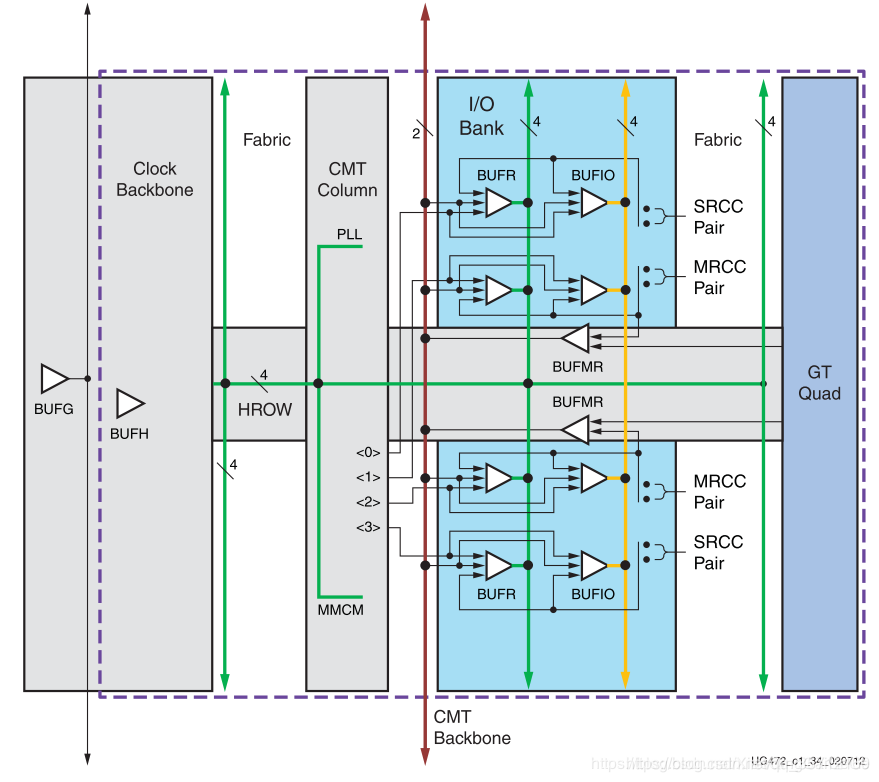

上一章咱们介绍了7系列FPGA的整体时钟架构,知道了FPGA是由很多个时钟区域组成,时钟区域之间可以通过Clock Backbone 和CMT Backbone来统一工作。本篇咱们就说一下时钟区域的内部结构,如下图所示的虚线框内即为一个时钟区域:

- BUFG即为全局时钟缓冲器,从图上看到,其输出时钟通过Clock

- Backbone可以到达任意一个时钟区域,而且BUFG通过HROW到达时钟区域内部的每个逻辑单元。

- BUFH即为水平时钟缓冲器,它相当于一个功能受限的BUFG,其输出时钟只能通过HROW在左右相邻的时钟区域内工作。

- BUFIO即为IO时钟缓冲器,其输出时钟只能作用在一个时钟区域的IO寄存器处,无法在FPGA内部逻辑使用。

- BUFR即为区域时钟缓冲器,其输出只能作用在一个时钟区域,相当于BUFH的阉割版。

- BUFMR即为多区域时钟缓冲器,其输出作用在本时钟区域,还可以通过CMT Backbone作用在上下相邻两个时钟区域。

- MMCM、PLL即时钟管理模块,用来消除时钟的延迟、抖动以及产生各种不同频率的时钟。

- CC即为外部时钟输入管脚,其管脚在内部可以连接到BUFG、BUFR、BUFIO、BUFH、MMCM、PLL等,看具体的应用具体连接。下图所示为更为细致的CC管脚连接图。一个时钟区域有4对CC管脚,其中2对SRCC,2对MRCC。SRCC作为区域时钟使用时,只能连接本时钟区域的BUFR和BUFIO。而MRCC则还可以通过BUFMR作用在上下相邻的时钟区域。

咱们自己结合这几张图好好分析下,就会彻底明白一个时钟区域内的具体时钟构造了,祝大家好运!利用上述所讲,下篇咱们将介绍如何在不同应用中来操作时钟。

3.时钟操作法则

上一章咱们介绍了7系列FPGA的时钟区域内部结构,本篇咱们接着介绍如何实际操作时钟。不说其它的,直接先上两张图,大家如果能看懂这两张图,那么就不用浪费时间看我接下来的废话了。。。。。

- MRCC:被外部差分/单端时钟驱动;可以驱动本时钟区域的4个BUFIO、4个BUFR、2个BUFMR、本时钟区域的CMT以及上下相邻时钟区域的CMT、16个BUFG、本时钟区域以及水平相邻时钟区域的BUFH。

- SRCC:和MRCC类似,但只作用在本时钟区域;其被外部差分/单端时钟驱动;可以驱动本时钟区域的4个BUFIO、4个BUFR、本时钟区域的CMT以及上下相邻时钟区域的CMT、16个BUFG、本时钟区域以及水平相邻时钟区域的BUFH。

- BUFIO:在相同的时钟区域内,其可以被MRCC、SRCC、MMCM的CLKOUT0~3、CLKFBOUT驱动,还可以被本时钟区域以及上下相邻区域的BUFMR驱动;其只能驱动本时钟区域内的ILOGIC、OLOGIC。

- BUFR:在相同时钟区域内,其可以被MRCC、SRCC、MMCM的CLKOUT0~3、CLKFBOUT驱动,还可以被本时钟区域以及上下相邻区域的BUFMR驱动;其能驱动本时钟区域内的CMT、本时钟区域内所有逻辑单元、以及16个BUFG(不推荐)。

- BUFMR:其只能被本时钟区域的MRCC以及某些GT时钟驱动;其能驱动本时钟区域以及上下相邻区域的BUFIO、BUFR。

- BUFG:其能被每个时钟区域内的SRCC、MRCC、CMT、GT、BUFR(不推荐)、其他BUFG;其可以驱动CMT、GT时钟、其他BUFG、FPGA内任何逻辑单元、BUFH。

- BUFH:其能被本时钟区域以及左右相邻时钟区域内的SRCC、MRCC、CMT、BUFG、GT时钟驱动;其能驱动本时钟区域的CMT、GT时钟、以及本时钟区域内的所有逻辑单元。

- GT时钟之RXUSERCLK、TXUSERCLK:其能被任何BUFG、以及本时钟区域内的BUFH驱动;其只能驱动专用的串行收发器模块。

- GT时钟之RXOUTCLK、TXOUTCLK:其被专用的串行收发器模块驱动;其能驱动BUFG、相同时钟区域内的CMT、BUFMR、BUFH以及相邻时钟区域内的BUFH。

- MGTREFCLK:其被外部MGT时钟源驱动;其能驱动BUFG、相同时钟区域内的CMT、BUFMR、BUFH以及相邻时钟区域内的BUFH。

- CMT(PLL&MMCM):其能被BUFG、SRCC(本时钟区域以及上下相邻时钟区域)、MRCC(本时钟区域以及上下相邻时钟区域)、GT(本时钟区域)、BUFR(本时钟区域或者上下相邻时钟区域加上BUFMR)、BUFMR、MMCM/PLL.CLKOUT0~3驱动;其能驱动BUFG、相同时钟区域内的BUFIO、BUFR、BUFH以及水平相邻的时钟区域的BUFH、MMCM/PLL。

咱们需要用的到时钟单元以及用法都在上面完整列出了(没有列出配置时钟,配置时钟不需要咱们操作),需要使用的时候就可以按照上述的方式来操作时钟。这样是不是使用起来很方便呢?

顺便提一下,CMT即MMCM和PLL很重要,基本上咱们在使用FPGA时,外部输入时钟都需要先用CMT进行校正、去抖、分频等,其输出时钟才能被咱们使用。所以下一篇咱们就单独说一下CMT这个时钟模块之中的重中之重!

4.CMT简介

上篇咱们仅仅简要的介绍了时钟的用法,并未详细的说明,主要是因为很多时钟用法是针对特定的应用需求,无法一一介绍。本篇咱们将重提上篇的CMT时钟模块,聊一聊它的用法。可以这么说,每个靠谱的FPGA应用里都应该用到CMT模块。

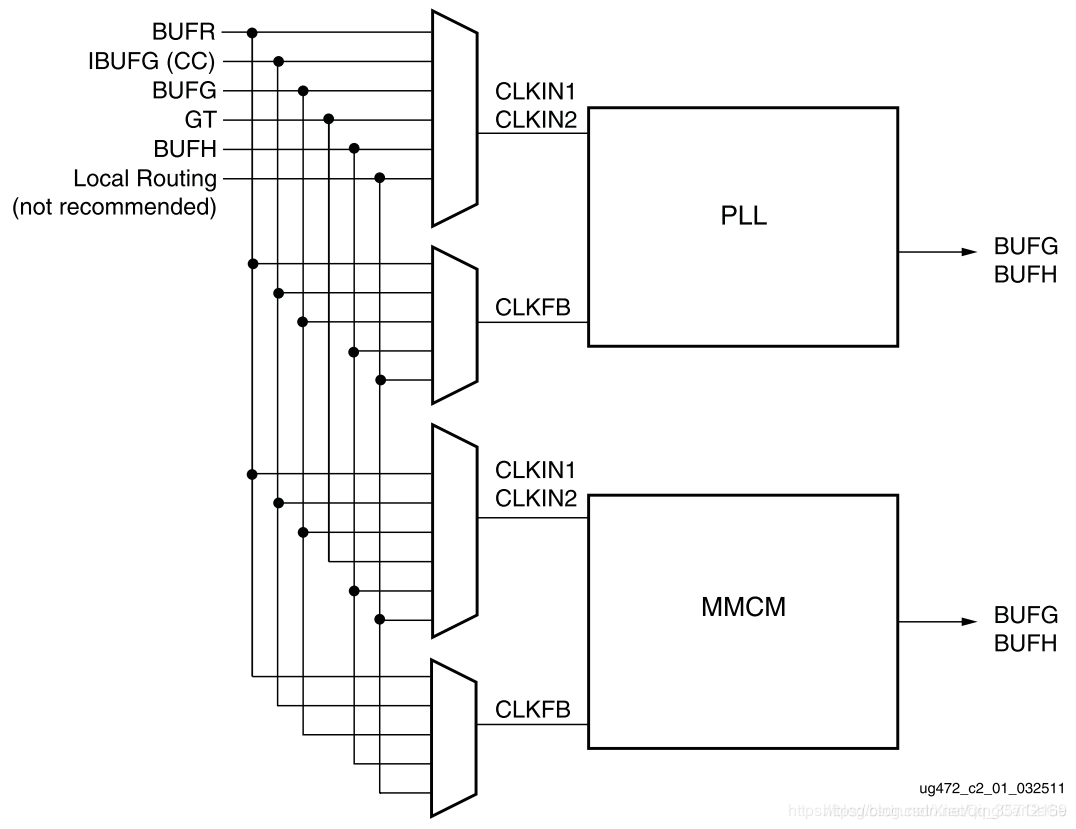

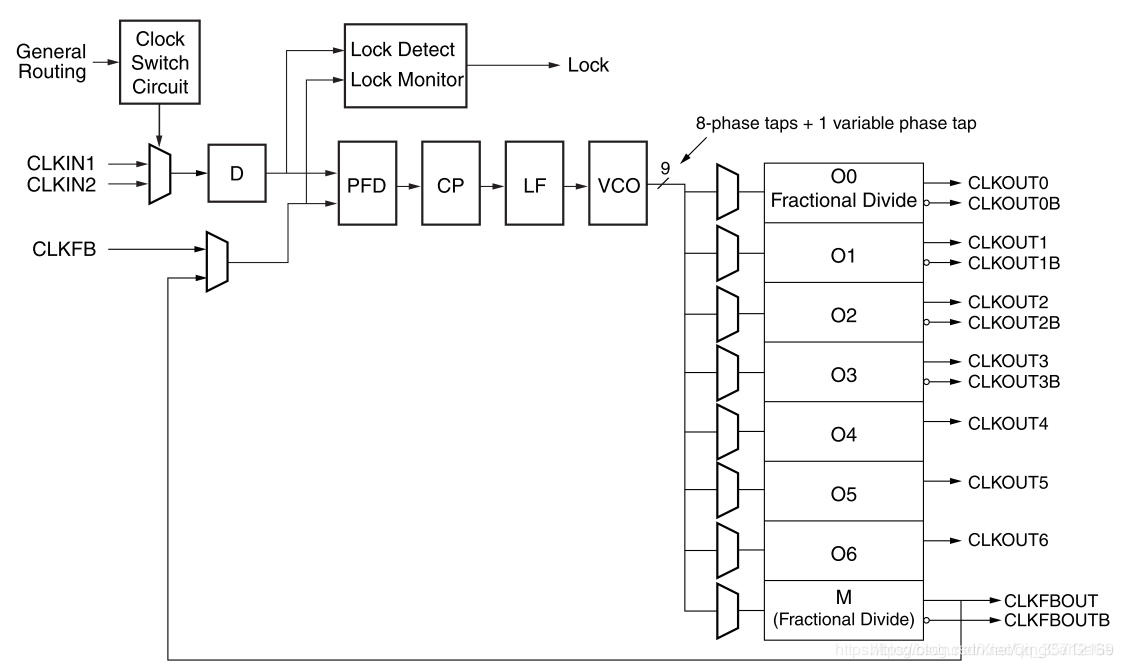

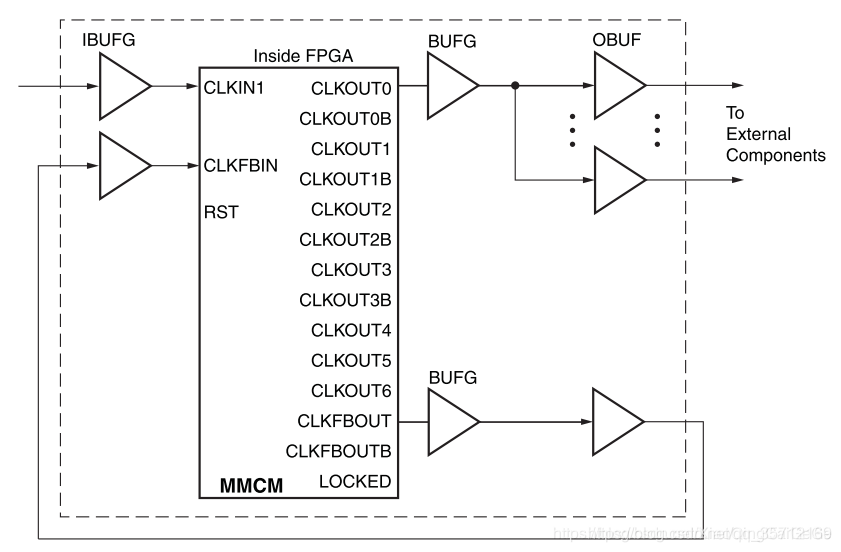

在7系列FPGA里,每一个时钟区域对应一个CMT(clock management tile),CMT由1个MMCM(mixed-mode clock manager)和1个PLL(phase-locked loop)组成,如图1所示为其输入/输出连接图。

MMCM、PLL的功能可以总结为3点:

- 频率综合:将外部输入的固定频率时钟调理成多路可调节频率的时钟。

- 去抖动(谷歌时钟抖动的含义,这里不具体介绍)。

- 去偏斜(谷歌时钟抖动的含义,这里不具体介绍)。

咱们这里强调下,7系列FPGA里的PLL只是MMCM的功能子集。这里咱们先介绍MMCM,如下图所示为其结构框图:

上图咱们一目了然,MMCM有2个时钟输入,使用时任选1路即可,输入时钟经过PFD(phase-frequency detector),CP(charge pump),LF(loop filter)后产生一定幅度的电压输入到VCO,VCO产生频率与输入电压幅度成比例的高频时钟,再被除以M倍并反馈到PFD。因此VCO的输出频率是一个稳定的、输入频率M倍的高频时钟,该时钟除以不同的倍数(用户可调)即可输出时钟clkout0clkout6。另外第0路输出和反馈输出是可以被分数除法,且第0路第3路提供反相180度的输出,VCO的输出还可以精确调整相位,这是7系列FPGA特有的。

咱们再看PLL的结构,如下图所示:

其结构与MMCM大体一致,但没有反相输出、分数倍数的除法、精确的动态相位调整以及CLKOUT6。

这里强调一下:MMCM、PLL均可实现时钟整数倍的频率综合、去抖、去偏斜,但MMCM还可以实现分数倍的频率综合、反相时钟输出以及动态的时钟相位调整。当然,对于咱们一般的应用来说,用不到MMCM的这些高端功能,两者使用没啥区别。

接下来咱们给出xilinx官方推荐的几种MMCM/PLL的使用方法:

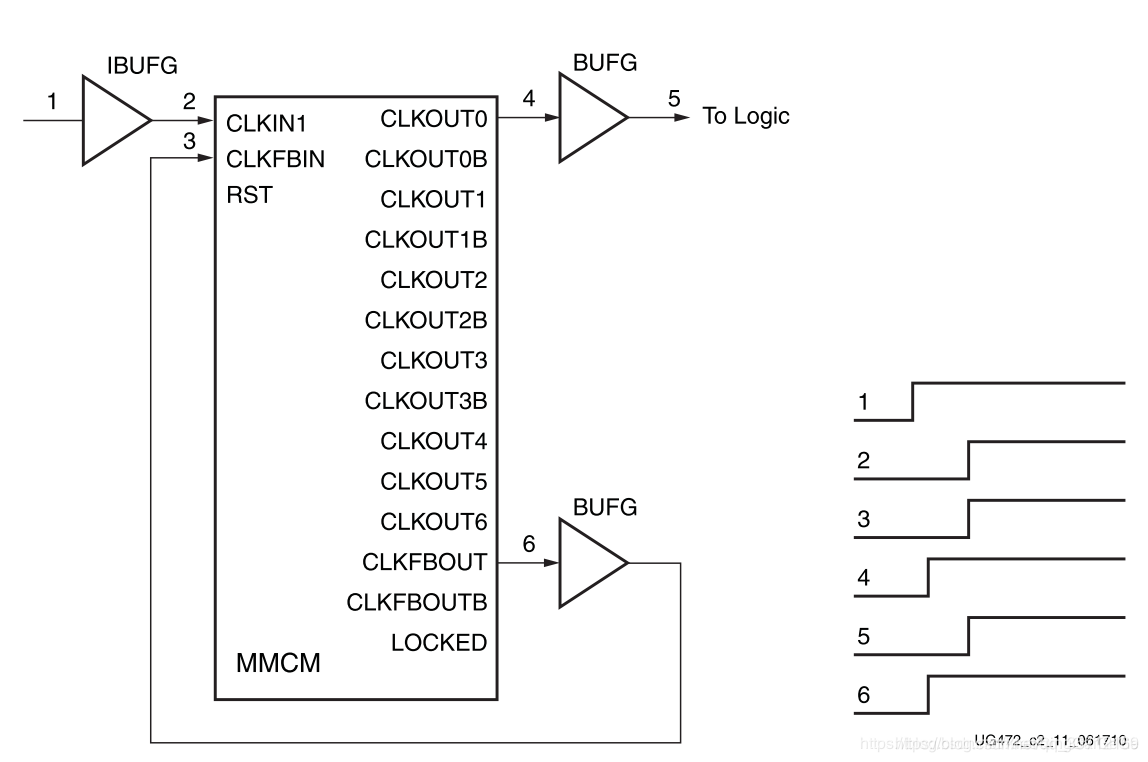

图4为最最常用的用法,目前被使用的最多,这种方式设计保留了输入与输出时钟之间的相位关系,时钟性能最高,系统最稳定,但需要使用2个BUFG,BUFG在FPGA里面属于稀缺资源,只有32个,对于某些特别复杂的系统可能就捉襟见肘了。

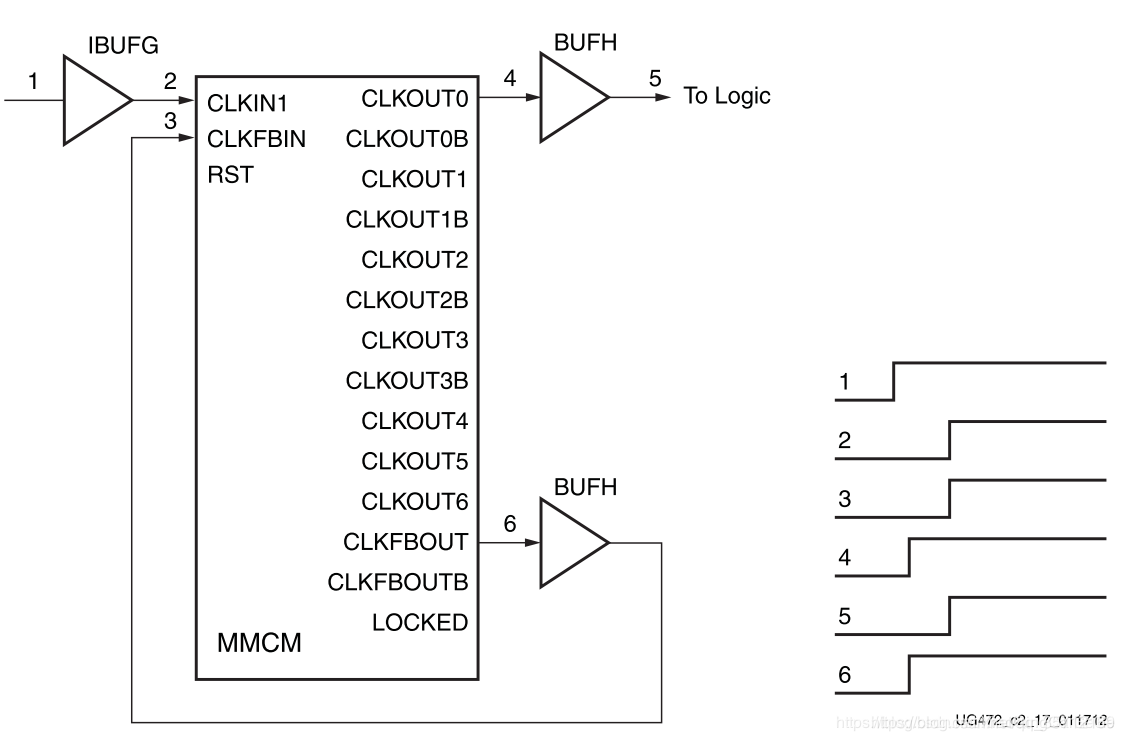

图5是将BUFG换成了BUFH,其系统性能是优于BUFG的,但前一篇咱们提到过,BUFH的使用范围只有左右相邻的时钟区域,对于逻辑资源使用量超过2个时钟区域的应用肯定就不合适了。

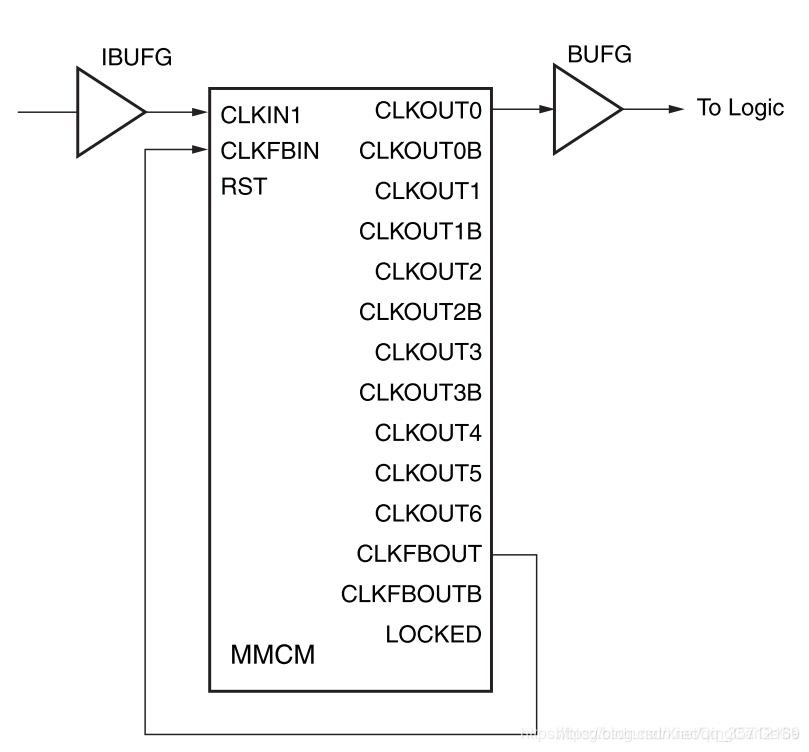

图6为时钟的内部反馈应用,由于没有引入反馈BUFG的噪声,因此输出时钟的噪声性能更好,但失去了输入与输出时钟之间的相位关系,所有这种用法适用于高精度的频率综合,对相位关系不太关注的应用。

图7为零延迟的时钟应用,这种应用适用于单个外部时钟源供给需要保持相位关系的多个数字系统。

到此咱们的7系列FPGA的时钟篇就算是简简单单的介绍完了,咱们下一部分就介绍7系列FPGA的内部逻辑资源吧,所有数字系统的功能实现都得靠它啦~

欢迎大家关注我创建的微信公众号——小白仓库

原创经验资料分享:包含但不仅限于FPGA、ARM、RISC-V、Linux、LabVIEW等软硬件开发,另外分享生活中的趣事以及感悟。目的是建立一个平台记录学习过的知识,并分享出来自认为有用的与感兴趣的道友相互交流进步。