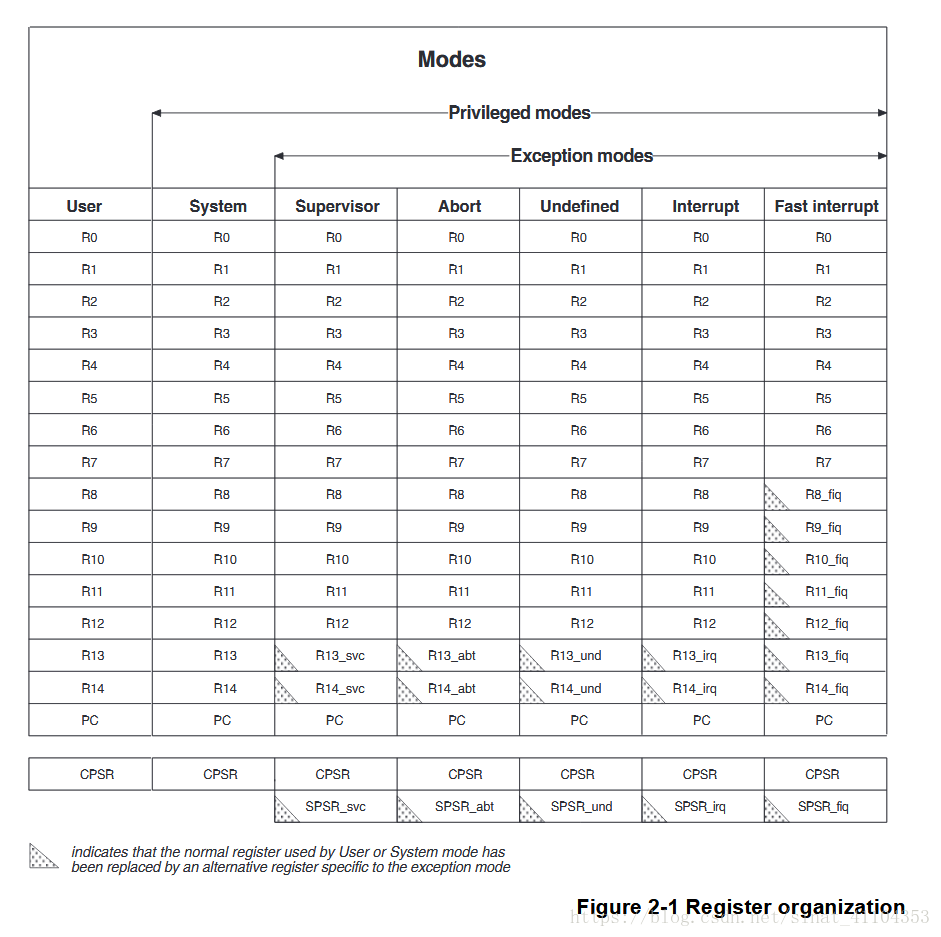

ARM 处理器总共有 37 个寄存器。

图片中的有半三角的就是分组寄存器。

那么我们怎么理解这个分组呢?

在 ARM Generic Interrupt Controller 的 4.1.4 小结有这样一段话:

Register banking refers to providing multiple copies of a register at the same address. The properties of a register access determine which copy of the register is addressed.

对这段话我的比喻是(以 R8-R12 为例):我们可以把 R8~R12 这 5 个寄存器看作 我们的 5 个手指头。当处于非 fiq 模式时,我们访问的是 5 个手指头的正面。但是一旦切换到 fiq 模式后,我们访问的就是这 5 个手指头的背面了。(手指头还是那些手指头,对应原文的 same address,每个手指头的正反面对应原文的 multiple copies of a register)

那么我们可能会有疑问:在非 fiq 模式下 R12 寄存器内保存了一些数据,切换到 fiq 模式后再继续访问同一寄存器 R12_fiq 会不会把原有数据给覆盖掉呢?

Benoit 在 sof 的回答是:

When the processor enters an exception, the banked registers are switched automatically with another set of these registers.

Virtually, the exception handler routine doesn’t have to save these registers on the stack to prevent them from being clobbered later on (by the exception handler functions). The processor just keeps a safe copy of that set; and will restore the original set on exception return.

翻译:

当处理器进入异常时,分组寄存器被自动切换到这些寄存器的另一组寄存器。

实际上,异常处理程序例程不必将这些寄存器保存在堆栈上,以防止它们在以后被异常处理函数破坏。 处理器只保留该组的安全副本; 并将在异常返回时恢复原始集。

所以,分组寄存器切换的时候,处理器应该会保留这些寄存器的安全副本,防止寄存器切换前的数据被破坏。

分组寄存器的目的:

stackexchange 上的回答觉得不错:

The primary purpose of this type of register banking is (typically) not to extend addressable storage but to provide faster interrupt handling by avoiding the need to save register values, load values used by the interrupt handler, and restore the original register values and to simplify interrupt handling.

更多关于分组寄存器的话题可以参考:https://stackoverflow.com/search?q=[arm]+banked+is%3Aquestion+closed%3Ano