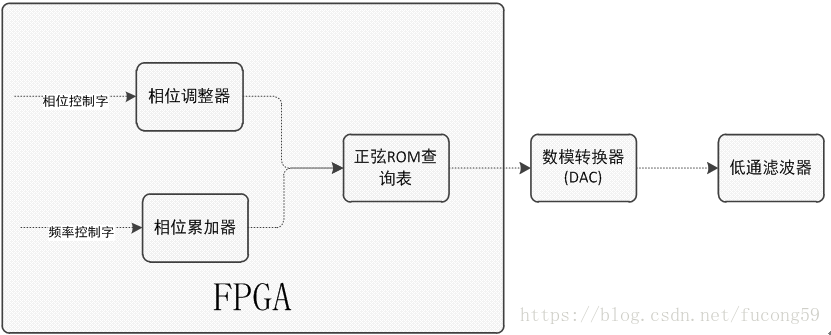

一、DDS的系统结构

DDS是直接数字式频率合成器(Direct Digital Synthesizer),系统结构可分为如下几个部分,其中相位控制字可调整输出正弦波的相位,频率控制字可以调整输出正弦波的频率。DAC把FPGA输出的数字量转换成模拟信号,因为信号中有大量高频信号,再加一级的低通滤波器可以使信号变得更加平滑。

图1:系统框图

二、实现基本原理

通过MATLAB可以生成一组2^N个点的正弦波查找表,如果系统时钟(Fclk)按地址加1的顺序循环读取ROM查找表的值,则可以产生一个周期为fclk/2^N的一个正弦波信号(称为基频)。因为系统时钟不能改变,而如果想得到更高频率的信号,可以通过减少输出ROM查找表的点的方法(跳过ROM表中的一些值)来加快ROM表周期读取实现,而如果想得到更低的频率,则可以通过重复输出一个点的值来减慢ROM表周期的读取来实现。

三、系统参数选择

相位累加器是实现DDS的核心,ROM的位宽和深度、系统时钟频率、相位累加器的宽度的参数选择是设计满足要求需要考虑的重要参数,这里通过一个例子说明:

假设系统时钟为50M, ROM的位宽为8位,即把一个正弦波的峰峰值用8位数据(256个点)来量化,则需要512个点去表示一个周期的正弦波,设置ROM表的深度为512。

因为ROM的深度为512(2^9)位,所以相位累加器要大于9位,只需取高9位作为ROM的输入地址,低位作为累计量。假设相位累加器是16位位宽,因此高9位作为ROM的地址输入。

频率控制字是相位累计器每次加的值,如果我们要得到这个假设系统的基频,则需要每个时钟沿都对ROM的地址加1,即16位相位累加器的第7位加1(见图2),则输入的控制字Fword为1000_0000,产生的基频为50M/512= 97656.25Hz,其中512是ROM的深度,也是2^16循环计数一次的个数,其取值为2^16/Fword。所以输出频率(Fout)可以用公式表示为:Fout=50M/(2^16/Fword)。假设系统频率为Fclk,相位累加器的位宽为N,则Fout=(Fclk*Fword)/2^N。我们可以通过设置不同的Fword大小来调节输出的正弦波频率。

图2:每次对第7位加1

在这个例子中Fword每加1即输出频率改变50M/2^16= 762.939453125,所以输出频率的最小分辨率约为763Hz,系统输出的最小频率也为763Hz;又因为当不断增加输出正弦波的频率的时候会跳过很多点去采样ROM表的数据,对于本例中如果系统要求一个周期必须输出16个正弦波的采样点,则满足要求的最大正弦波频率为50M/16=3.125MHz,则该设计满足要求的频率约为763Hz~3.125MHz,其中输出正弦波频率的最小分辨率约为763Hz。

由此可以知道在设计一个优良DDS之前首先我们需要知道DAC的位宽、输出频率范围、频率分辨率和最小周期采样点个数,根据这些要求我们可以通过计算出满足要求的系统的时钟频率、ROM位宽,数据深度、相位累加器的宽度这些参数满足设计的需求。

相位调整器是在把每次给ROM表的地址加上一个输入的一个固定偏移量即相位控制字Fphase,其位宽和ROM的地址位宽相同即可。

四、设计一个输出3KHz-3MHz的正弦波

假设要求输出每个正弦波的周期点为64个,因为最大的输出频率为3M,所以系统时钟至少应该为64*3M=192M。

假设DAC的位宽为16位,则为了尽可能利用好DAC的精度,我们设计ROM的位宽为16位,数据深度为131072。假设DAC的最大输出电压为5V则量化精度可以达到5V/65536≈0.0763mV。

因为输出频率的最小值为3k,累加器的宽度为log(192M/3k)≈15.965784,所以至少累加器需要设置为16位位宽。为了能达到更好的频率分辨率,我们设计累加器的计数位宽为32位,则该系统的输出频率分辨率为192M/(2^32)≈0.0447Hz。