DDS

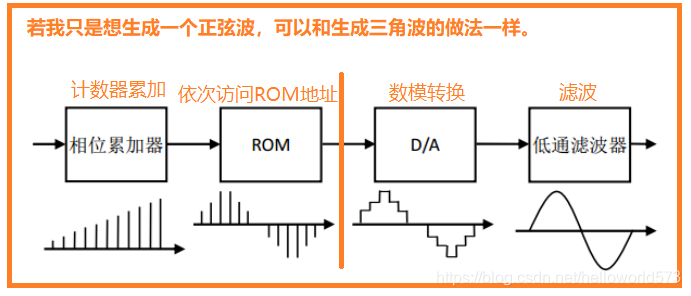

1 用ROM生成普通的正弦波

—>用ROM生成三角波

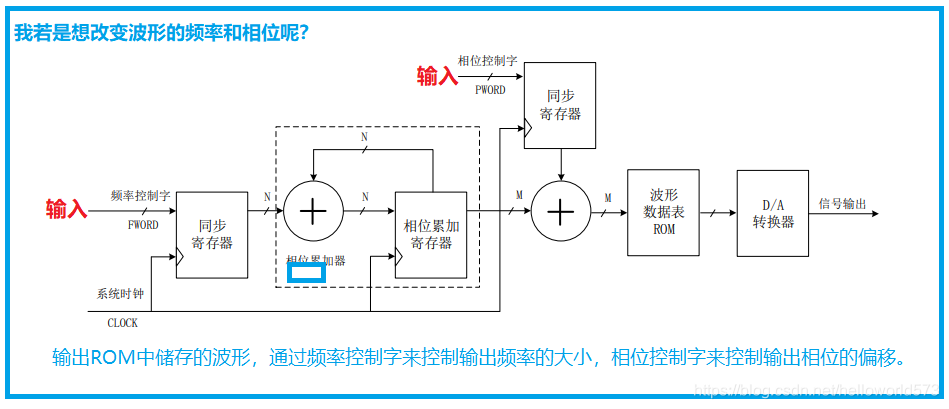

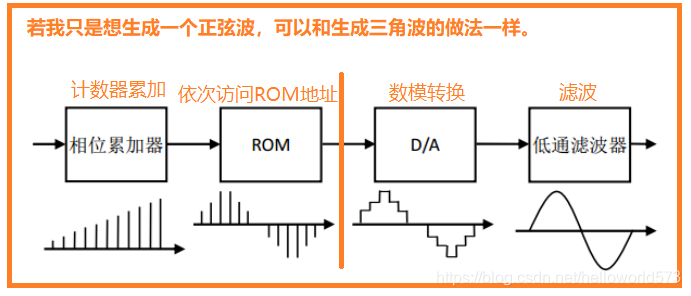

2 频率控制字和相位控制字

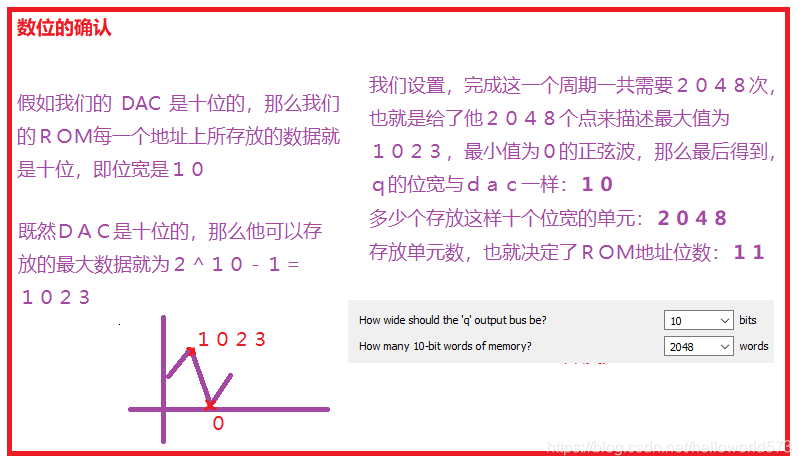

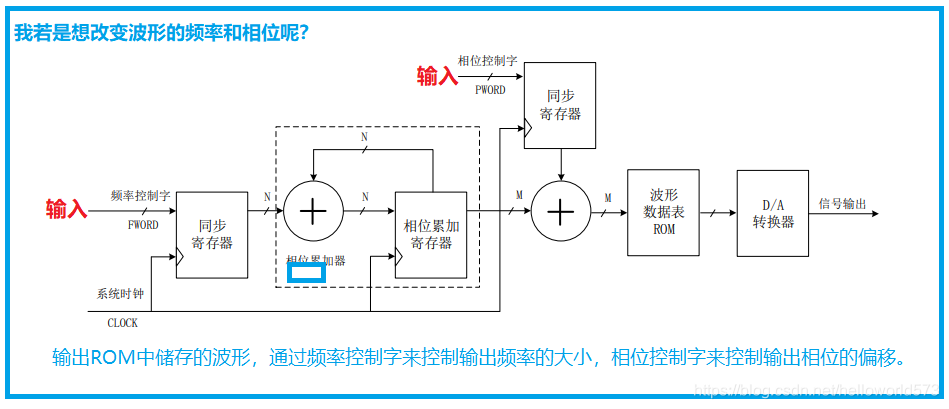

3 数位的确认

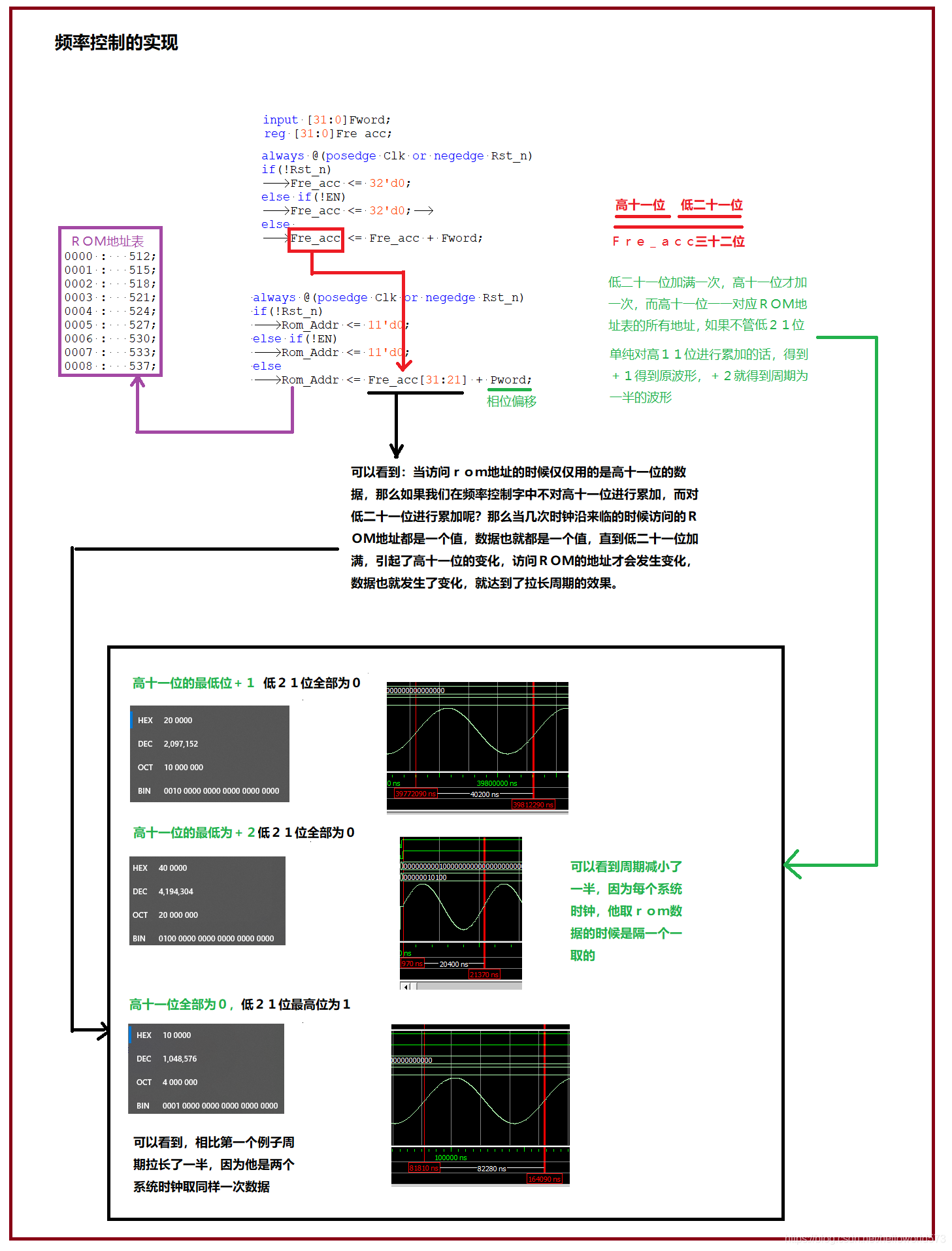

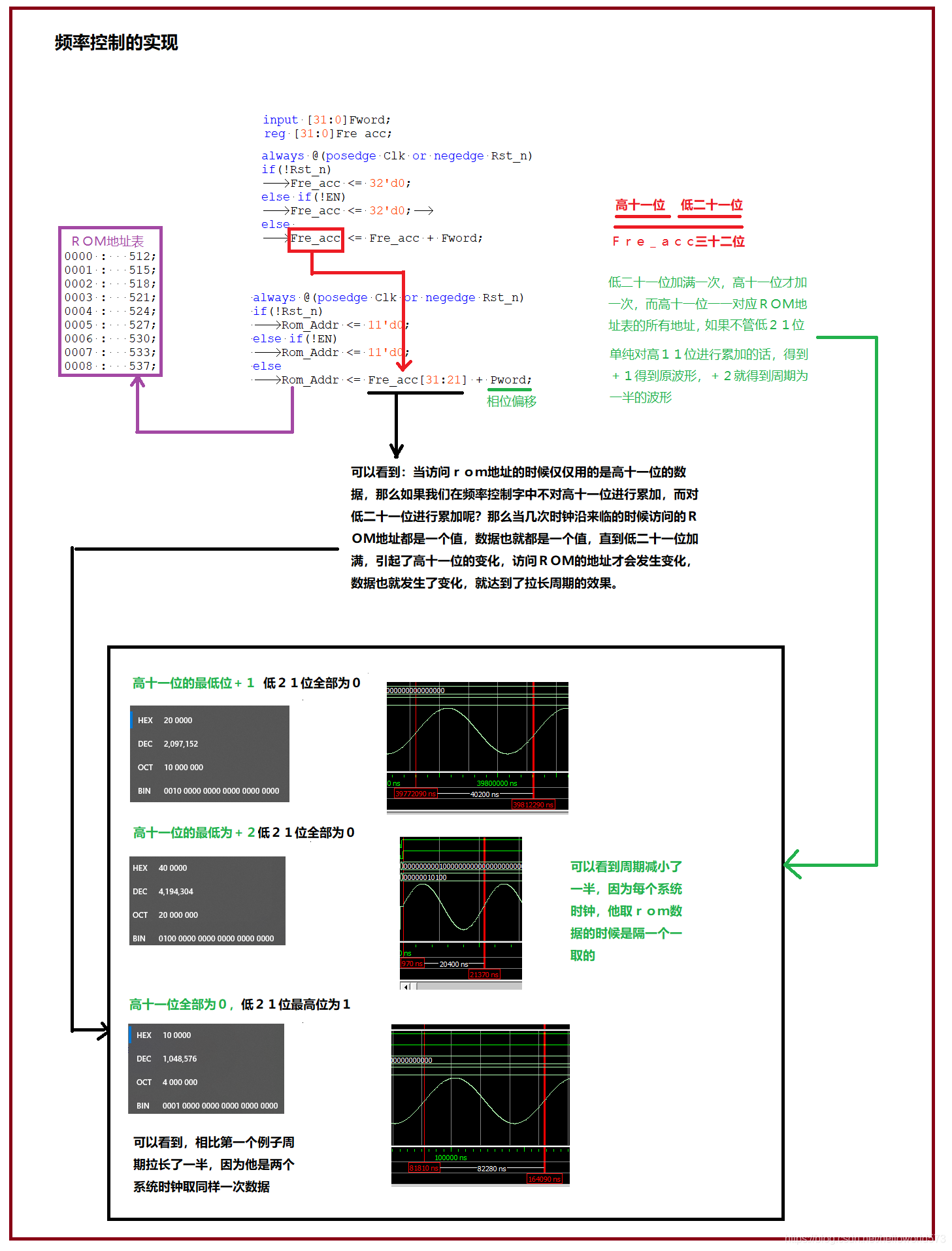

4 频率控制的实现

代码

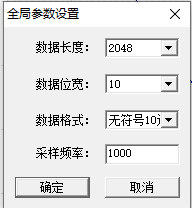

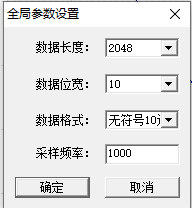

1 获取mif文件

2 DDS

module DDS_Module(

Clk,

Rst_n,

EN,

Fword,

Pword,

DA_Clk,

DA_Data

);

input Clk;

input Rst_n;

input EN;

input [31:0]Fword;

input [10:0]Pword;

output DA_Clk;

output [9:0]DA_Data;

reg [31:0]Fre_acc;

reg [10:0]Rom_Addr;

always @(posedge Clk or negedge Rst_n)

if(!Rst_n)

Fre_acc <= 32'd0;

else if(!EN)

Fre_acc <= 32'd0;

else

Fre_acc <= Fre_acc + Fword;

always @(posedge Clk or negedge Rst_n)

if(!Rst_n)

Rom_Addr <= 11'd0;

else if(!EN)

Rom_Addr <= 11'd0;

else

Rom_Addr <= Fre_acc[31:21] + Pword;

ddsrom ddsrom(

.address(Rom_Addr),

.clock(Clk),

.q(DA_Data)

);

assign DA_Clk = (EN)?Clk:1'b1;

endmodule

3 rom

module ddsrom (

address,

clock,

q);

input [10:0] address;

input clock;

output [9:0] q;

4 testbench

`timescale 1ns/1ns

`define clk_period 20

module DDS_Module_tb;

reg Clk;

reg Rst_n;

reg EN;

reg [31:0]Fword;

reg [10:0]Pword;

wire DA_Clk;

wire[9:0]DA_Data;

DDS_Module f1(

.Clk(Clk),

.Rst_n(Rst_n),

.EN(EN),

.Fword(Fword),

.Pword(Pword),

.DA_Clk(DA_Clk),

.DA_Data(DA_Data)

);

initial Clk = 0;

always #10 Clk = ~Clk;

initial begin

Rst_n = 1'b0;

EN = 1'b0;

Fword = 32'd0;

Pword = 11'd0;

#(`clk_period*20)

Rst_n = 1'b1;

#(`clk_period*20)

EN = 1'b1;

Pword = 11'd20;

Fword = 32'h400000;

#(`clk_period*2000000)

$stop;

end

endmodule