每个BIOS一般都会有自己适配的一套硬件架构,因为不同的硬件资源对于BIOS的要求及操作都会有不同,硬件资源千变万化,BIOS程序不可能考虑到所有的情况。SeaBIOS也不例外。

SeaBIOS所针对的硬件平台是奔腾时代的PC架构,以Intel 440FX PMC(PCI and Memory Controller)为北桥芯片,PIIX(PCI ISA Xcelerator)为南桥芯片构成相应的芯片组。

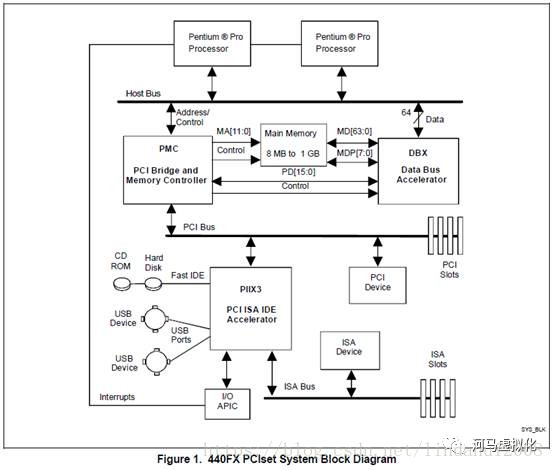

440FX PMC的基本结构图如下所示:

北桥芯片PMC用于连接主板上的高速设备,向上提供了连接处理器的Host总线接口,可以连接多个处理器,向下则主要提供了连接内存DRAM的接口和连接PCI总线系统的PCI总线接口,通过该PCI root port扩展出整个PCI设备树,包括PIIX南桥芯片。

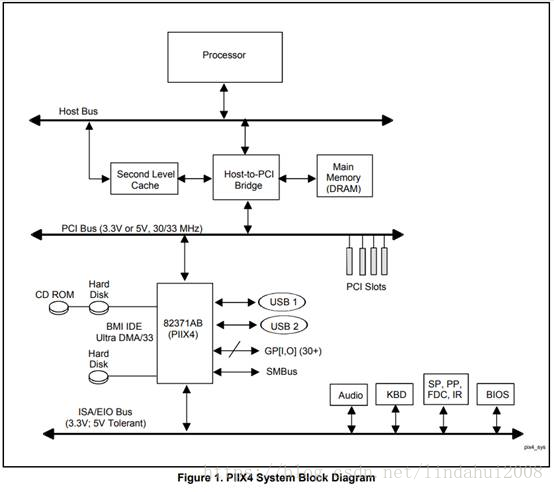

南桥芯片PIIX4的基本结构图如下所示:

PIIX(PCI ISA IDE Xcelerator)南桥芯片则用于连接主板上的低速设备,主要包括IDE控制器、DMA控制器,硬盘,USB控制器,SMBus总线控制器,并且提供ISA总线用于连接更多的低速设备,如键盘、鼠标、BIOS ROM等。

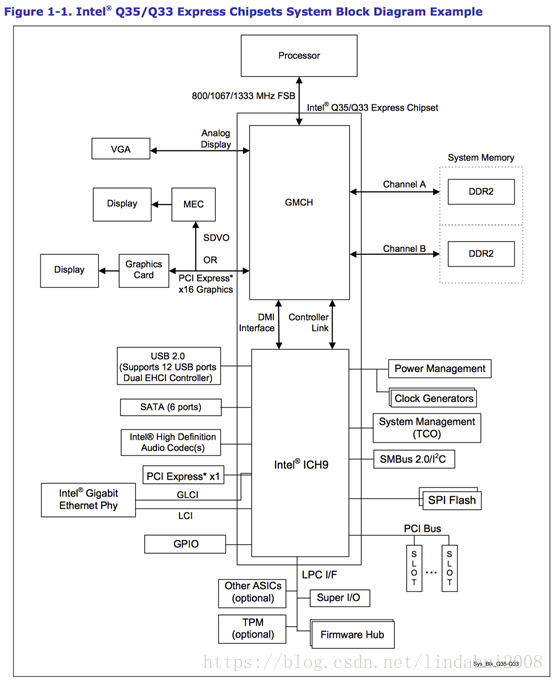

由于支持的硬件平台i440FX + PIIX已经很老(1996年),而Intel不断推出新的芯片组,搞出PCIe、AHCI等新东西,该平台已经无法满足需求。后来SeaBIOS引入了Intel Q35芯片组,并且支持了PCIe。在新的平台上,以Q35 MCH为北桥芯片,以ICH 9位南桥芯片,该硬件平台是Intel 2007年推出的。如下图所示

即使是现在来看Q35MCH + ICH9的架构也已经十多年了,也并不新,PMC + PIIX的架构更是老掉牙,但是目前的很多虚拟机都还在使用这个架构。原因是没有更新的必要,因为Hypervisor模拟硬件的时候,模拟的是硬件的功能,并不模拟硬件的内部机制、架构和物理特性,虽然新的硬件层出不穷,架构更新也挺快的,速度越来越快,但是其功能和对外接口却一直比较稳定,如PCI接口已经N多年了,但是却基本保持不变。如果添加新的架构支持,则SeaBIOS的代码要做很多改动,但是功能却基本保持不变,而且也基本看不到性能的提升,因为其运行的硬件环境都是模拟出来的(不考虑透传的情况)。对其进行硬件架构更新的目的是为了添加对新硬件功能、接口的支持,如Q35MCH + ICH9加入了对PCIe总线的支持。

理解SeaBIOS的硬件架构对于理解SeaBIOS的源码具有重要的作用,因为里面由一些代码是用于配置和操作具体芯片组的,如果不理解其目标硬件架构,根本不知道那些代码在做什么。

同时也欢迎关注同名微信公众号“河马虚拟化”第一时间获取最新文章。