如果需要重读,需要用ram,如果不需要重读的话就用FIFO 双buffer不太好实现错误重传机制!!!!

双buffer作用:

1、跨时钟域

2、完成数据位宽转换

3、完成数据缓冲 双buffer缓冲操作示意图,在操作工程中存在两个clock1 和clock2,但是输入输出的传输带宽不能相差太大,会出现数据覆盖的现象

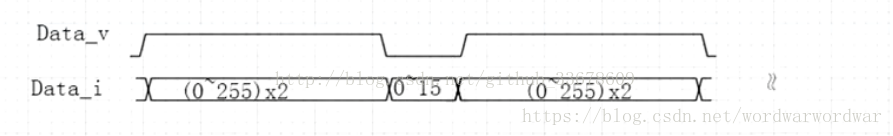

双buffer缓冲操作示意图,在操作工程中存在两个clock1 和clock2,但是输入输出的传输带宽不能相差太大,会出现数据覆盖的现象 。

1、如上图所示,输入端读数据比写数据速度要块,这样的话,在数据写完后让外部来读,这样在写的过程中,空闲的时间,读端,可以进行数据操作等操作(100MHz * 8bit < 75MHz * 16bit)

2、写完一次数据就用选择器选择另外一个ram写,在下降沿时切换,读选择器类似。

3、快时钟域向慢时钟域传输信号时,需要将写入的片选信号data|_v延迟两拍 。

testbeach中产生的数据思路

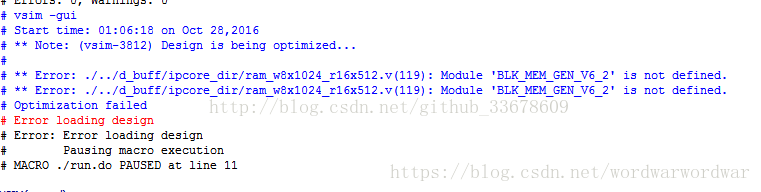

ISE产生的ipcore,不使用ISE自带的simulation仿真,直接用modulesim仿真时出现加入的ipcore找不到相关文件,如图所示

直接到该目录下搜索,然后copy出来到你的工程文件中

源码链接:

http://download.csdn.net/detail/github_33678609/9739924