逻辑运算区别于算术运算的地方在于:逻辑运算每个变量都只有两种状态——0和1(特殊情况下会用到X)。由于这个特点,逻辑运算的基本规则和方法也是另有一套体系。

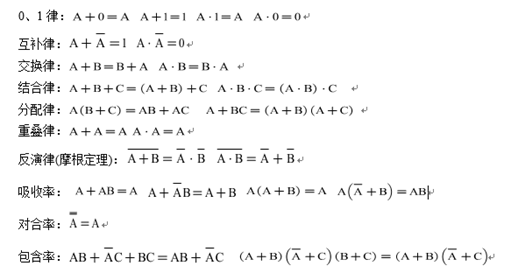

当存在多个输入变量时,逻辑表达式的化简就显得尤为重要。逻辑表达式的化简需要遵循一些基本的规则(运算法则),具体的见下图:

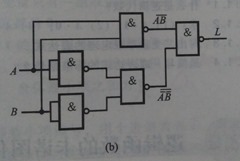

化简的目的是为了得到一些特定形式表达式的组合,比如:最小项、最大项等。常用的是最小项,化简之后的结果也称之为积之和(SOP)。化简之后,我们可以通过门电路画出对应的逻辑图(如下图)。

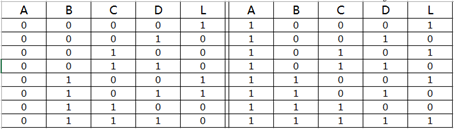

从最开始的需求(实现某某功能,比如译码器、加法器等)出发,我们能得到该功能对应的真值表。从真值表到最小项表达式需要借助卡洛图(数字电路必学)。

下图所示的真值表,

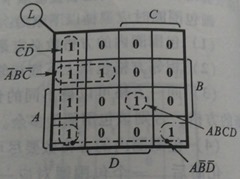

用卡洛图表示为:

经过化简之后可以得到:

。

有一点值得思考:FPGA中每个LUT只支持4输入或者6输入,如果真值表中输入变量有8个,这时应该怎么表示呢?一个8输入相当于两个4输入和一个2输入,从逻辑表达式上应该怎么化简?

这个问题以后有机会再来讨论。