第一步,输出要求。声明由于我的呼吸灯还没有实现,所以按照要求做了修改(老师当时要求的是左流水和右呼吸)

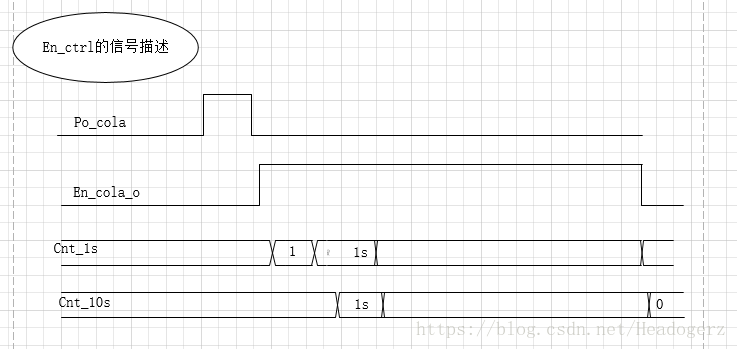

第二步,关键的信号描述EN_ctrl用了2个模块分别计数。之前可乐机状态机的状态也需要输出。按键例化的时候将之前的按键消抖2次就可以完成。

第三步,依然是把关键程序写出来。这里有2个新加了2个模块。实际上是三个模块,出可乐驱动信号,出可乐找钱驱动信号,还有就是led控制模块。

module en_money(

input wire sclk,

input wire rst_n,

input wire po_money_in,

output reg pi_money_o

);

reg [25:0] cnt_60; //计1秒的计数器

reg [3:0] cnt_1m; //计10秒钟计数器

parameter CNT_60=49_9999_99;

parameter CNT_1m=9;

always@(posedge sclk or negedge rst_n) //找钱拉高使能状态

if(!rst_n)

pi_money_o<=1'b0;

else if(cnt_1m==CNT_1m&&cnt_60==CNT_60)

pi_money_o<=1'b0;

else if(po_money_in==1)

pi_money_o<=1'b1;

always@(posedge sclk or negedge rst_n) //计数一秒钟

if(!rst_n)

cnt_60<=26'b0;

else if(pi_money_o==0)

cnt_60<=26'b0;

else if(cnt_60==CNT_60)

cnt_60<=26'b0;

else

cnt_60<=cnt_60+1'b1;

always@(posedge sclk or negedge rst_n) //计数10秒钟

if(rst_n==0)

cnt_1m<=4'b0;

else if (pi_money_o==0)

cnt_1m<=4'b0;

else if(cnt_1m==CNT_1m) //清零条件对比之前程序才发现 没写

cnt_1m<=cnt_1m+1'b1;

endmodule声明,这个模块有点问题。驱动信号一直没有拉低,我在连接到顶层的时候,也没有问题。下载到板卡验证的时候,出现流水灯不停止。我很郁闷。找了好久也没个结果。

module led_ctrl(

input wire sclk,

input wire rst_n,

input wire [3:0]led_in,

input wire [3:0]LED_in,

input wire en_cola_in,

input wire pi_money_in,

input wire [4:0] state,

output reg [3:0] led_o

);

parameter IDLE =5'b00001;

parameter HALF =5'b00010;

parameter ONE =5'b00100;

parameter ONE_HALF =5'b01000;

parameter TWO =5'b10000;

always@(posedge sclk or negedge rst_n)

if(!rst_n)

led_o<=4'b0000;

else if(en_cola_in==1)

led_o<=led_in;

else if(pi_money_in==1)

led_o<=LED_in;

else case (state)

IDLE : led_o<=4'b0000;

HALF : led_o<=4'b0001;

ONE : led_o<=4'b0010;

ONE_HALF : led_o<=4'b0011;

TWO : led_o<=4'b0100;

default : led_o<=4'b0000;

endcase

endmodule 这是led的控制模块,比较简单。

第三步,把上板的图片P出来,不好看。但是勉强看吧。

第四步,写一下学习5天多的感悟跟收获吧。

培训了小一周了,我算是大学接触过硬件。研究生也看了一年。可是来了这边,感觉根本不行,水平太次了。

主要收获如下:

1.代码一定要自己写,实现不了就修改,仿真。

2.良好的编码习惯,我看了学的比我好的人的代码,确实有很大差距。比如,默认10进制,也要写成10'd0;每个always块中都要用begin end语句包含起来。 顶层例化的时候,所有变量都要定义再最前面。

3.测试模块,ise是可以生成的,但初学者一定要自己写,我这周写了也不下20次了,但是仍然每次仿真都报错。好在现在不惧怕了,写多了就知道出错出在哪了。

4.工程实现时,每个信号都要看的清楚,信号拉高在那个位置,拉低是那个。我老犯的错误就是拉低信号不看,只是负责拉高。或者拉低的条件不完整,导致时序错误,希望共勉。

-----------最后一句话,共勉大家。既然选择远方就只顾风雨兼程。第五步,顶层例化跟仿真文件相似。就是把所有模块绑到一个大模块中。