这一章节主要描述S5PV210的clock management unit(CMU),在S5PV210里面,系统控制器(SYSCON)管理CMU和PMU(power management unit 电源管理单元)。

1.1时钟域

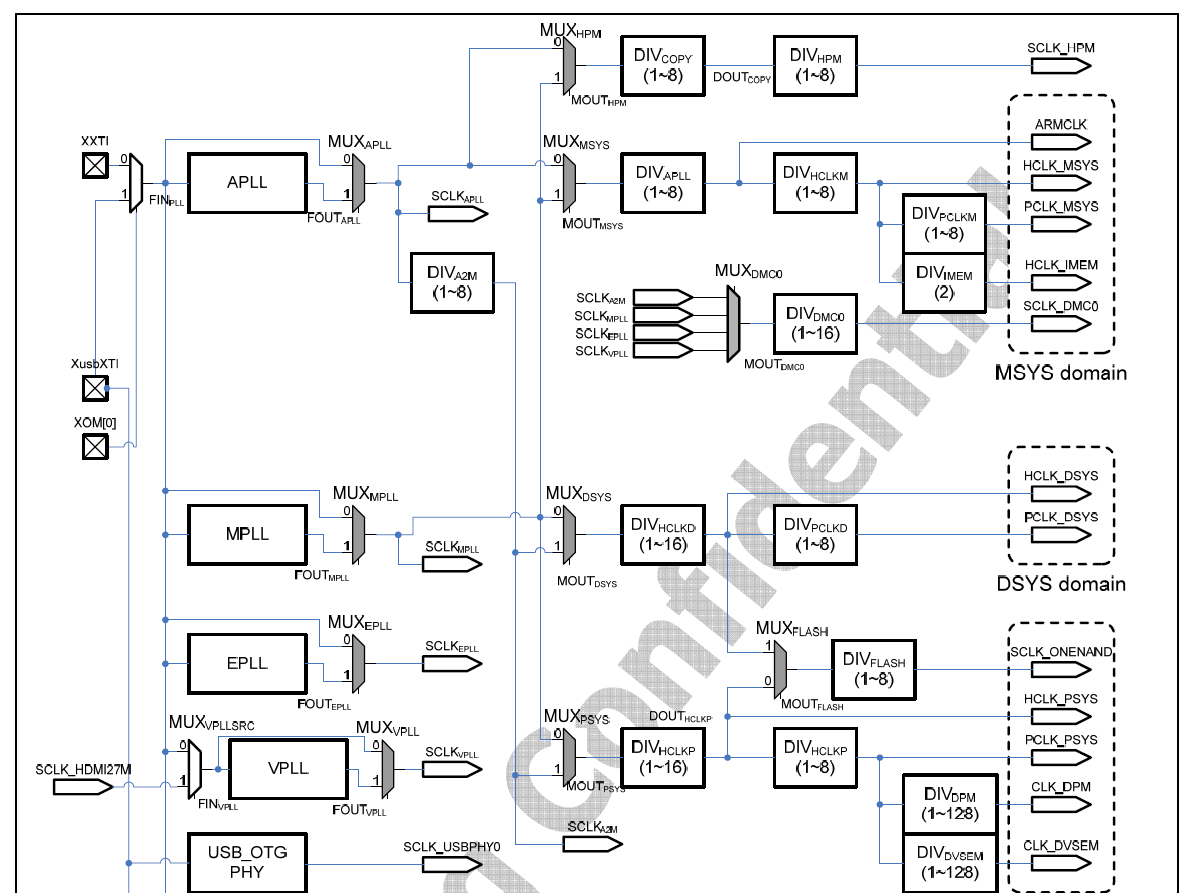

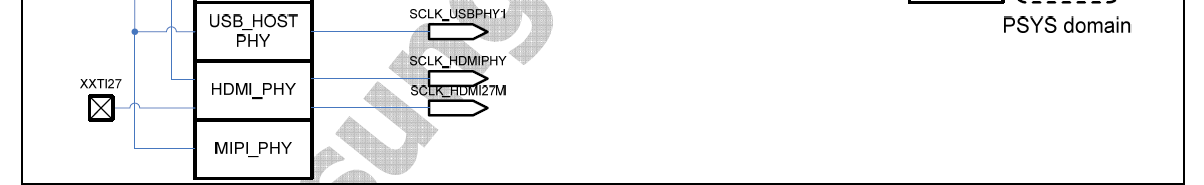

S5PV210包含3个时钟域,即:MSYS(main system)、DSYS(diaplay system)、PSYS(peripheral system),如下图

• MSYS:CPU(Cortex-A8 处理器)、DRAM存储控制器(DMC0和DMC1)、3D、内部SRAM(IRAM和IROM)、INTC、配置接口(SPER)。Cortex A8仅支持同步模式,因此它必须和200MHz AXI 总线同步操作

• DSYS:包含显示相关的模块,有FIMC、FIMD、JPEG、and multimedia IPs (all other IPs mentioned in X, L,and T blocks),如上图所示

• PSYS:内部外设相关(串口、SD、USB、GPIO、IIC、SPI等)

• 每个总线系统分别工作在200 MHz(最大)、166 MHz和133 MHz。在两个不同的域之间存在异步总线桥(BRG)。

1.2时钟源

可以通过四个晶振作为时钟源信号输入,通过MUX开关进行选择,在使用PLL进行倍频。

上图展示了S5PV210的时钟分类,顶级目录的时钟包含:

• Clocks from clock pads,that is,XRTCXTI,XXTI,XUSBXTI,and XHDMIXTI

• Clocks from CMU (for instance,ARMCLK,HCLK,PCLK,and so on)

• Clocks from USB PHY

• Clocks from GPIO pads

1.2.1时钟来自于时钟引脚

下面的时钟有时钟引脚提供,但是你可以禁掉这些引脚:

• XRTCXTI: Specifies (指定)a clock from 32.768 KHz crystal pad with XRTCXTI and XRTCXTO pins. RTC uses this clock as the source of a real-time clock.

• XXTI: Specifies a clock from crystal pad with XXTI and XXTO pins. When USB PHY is not used in commercial set, CMU and PLL use this clock to generate other clocks to modules (APLL, MPLL, VPLL, and EPLL.). The input frequency ranges from 12 ~ 50 MHz. It is recommended to use 24MHz crystal because iROM was designed based on the 24MHz input clock.

• XUSBXTI: Specifies a clock from a crystal pad with XUSBXTI and XUSBXTO pins. This clock is supplied to APLL, MPLL, VPLL, ELL, and USB PHY. For more information on USB PHY clock, refer to Chapter 8.4 ” USB 2.0 HOST Controller ” and 8.5 ” USB2.0 HS OTG “. It is recommended to use 24MHz crystal because iROM was designed based on the 24MHz input clock.

• XHDMIXTI: Specifies a clock from 27MHz crystal pad with XHDMIXTI and XHDMIXTO pins. VPLL or HDMI PHY generates 54MHz clock for TV encoder.

• XXTI and XXTO use wide-range OSC pads.

• XUSBXTI and XUSBXTO use wide range OSC pads.

• XHDMIXTI and XHDMIXTO use wide range OSC pads.

• XRTCXTI and XRTCXTO use OSC pads for RTC.

• ARMCLK specifies clock for Cortex A8 (up to 1GHz).

• HCLK_MSYS specifies AXI clock for MSYS clock domain, as shown in Figure 3-1. The maximum operating frequency is up to 200MHz.

• PCLK_MSYS specifies APB clock for MSYS clock domain, as shown in Figure 3-1. The maximum operating frequency is up to 100MHz.

• HCLK_DSYS specifies AXI/AHB clock for DSYS clock domain, as shown in Figure 3-1. The maximum operating frequency is up to 166MHz.

• PCLK_DSYS specifies APB clock for DSYS clock domain, as shown in Figure 3-1. The maximum operating frequency is up to 83 MHz.

• HCLK_PSYS specifies AXI/AHB clock for PSYS clock domain, as shown in Figure 3-1. The maximum operating frequency is up to 133MHz.

• PCLK_PSYS specifies APB clock for PSYS clock domain, as shown in Figure 3-1. The maximum operating frequency is up to 66 MHz.

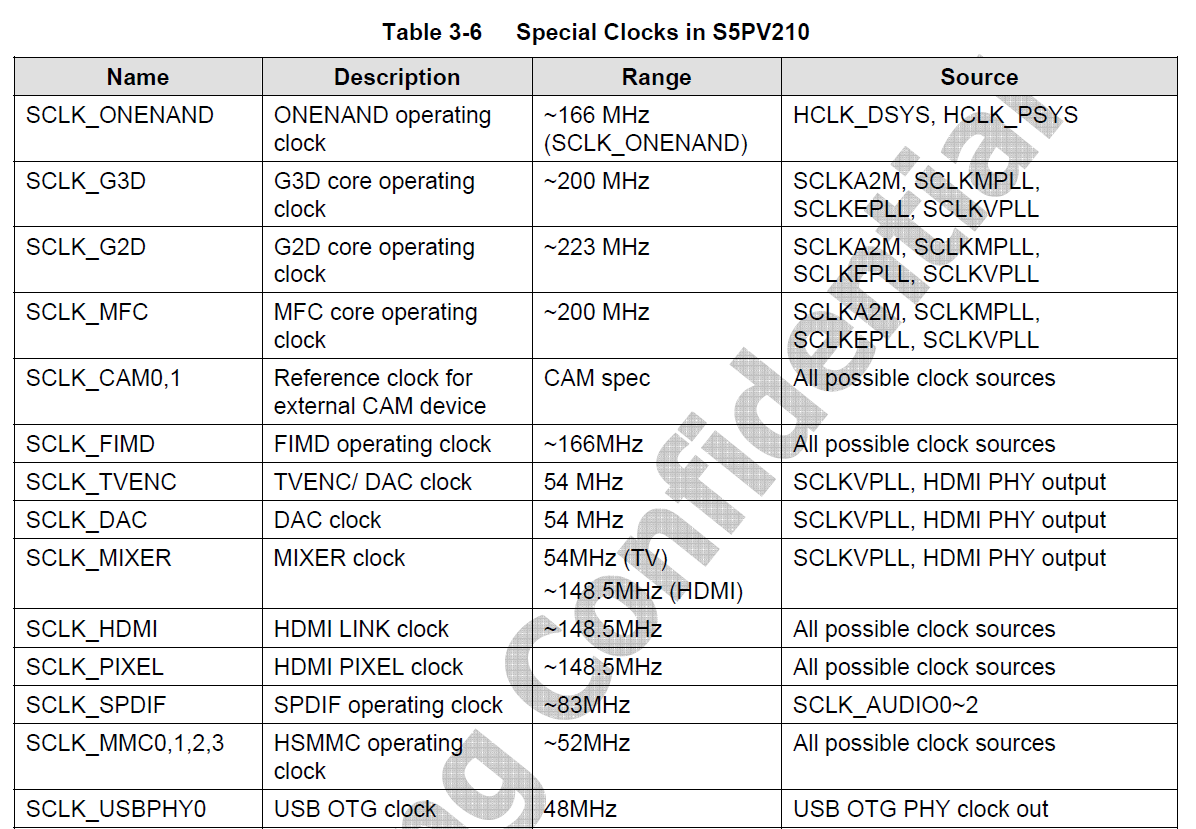

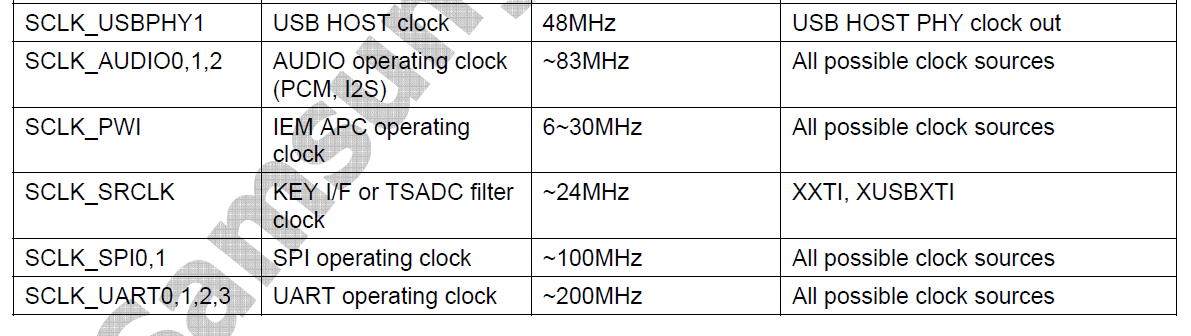

• Special clocks specify all the clocks except bus clock and processor core clock.

1.2.2时钟来自于CMU

CMU 产生中等频率的时钟,时钟源是自于时钟引脚的时钟 (that is, XRTCXTI, XXTI, XUSBXTI, and XHDMIXTI), four PLLs (that is, APLL, MPLL, EPLL, and VPLL), USB PHY and HDMI PHY clock. 这些时钟可以被选择,pre-scaled,提供给相应的模块。

It is recommended to use 24MHz input clock source for APLL, MPLL, EPLL and VPLL.

To generate internal clocks, the following components are used.

• APLL uses FINPLL (refer to Figure 3-1) as input to generate 30MHz ~ 1GHz.

• MPLL uses FINPLL as input to generate 50MHz ~ 2GHz.

• EPLL uses FINPLL as input to generate 10MHz ~ 600MHz.

• VPLL uses FINPLL or SCLK_HDMI27M as input to generate 10MHz ~ 600MHz. This PLL generates 54MHz video clock.

• USB OTG PHY uses XUSBXTI to generate 30MHz and 48MHz

• HDMI PHY uses XUSBXTI or XHDMIXTI to generate 54MHz

In typical S5PV210 applications,

• Cortex A8 and MSYS clock domain uses APLL (that is, ARMCLK, HCLK_MSYS, and PCLK_MSYS).

• DSYS and PSYS clock domain (that is, HCLK_DSYS, HCLK_PSYS, PCLK_DSYS, and PCLK_PSYS) and other peripheral clocks (that is, audio IPs, SPI, and so on) use MPLL and EPLL.

• Video clocks uses VPLL.

Clock controller allows bypassing of PLLs for slow clock. It also connects/ disconnects the clock from each block(clock gating) using software, resulting in power reduction.

1.2.3时钟关系

Clocks have the following relationship:

• MSYS clock domain

− freq(ARMCLK) = freq(MOUT_MSYS) / n, where n = 1 ~ 8

− freq(HCLK_MSYS) = freq(ARMCLK) / n, where n = 1 ~ 8

− freq(PCLK_MSYS) = freq(HCLK_MSYS) / n, where n = 1 ~ 8

− freq(HCLK_IMEM) = freq(HCLK_MSYS) / 2

• DSYS clock domain

− freq(HCLK_DSYS) = freq(MOUT_DSYS) / n, where n = 1 ~ 16

− freq(PCLK_DSYS) = freq(HCLK_DSYS) / n, where n = 1 ~ 8

• PSYS clock domain

− freq(HCLK_PSYS) = freq(MOUT_PSYS) / n, where n = 1 ~ 16

− freq(PCLK_PSYS) = freq(HCLK_PSYS) / n, where n = 1 ~ 8

− freq(SCLK_ONENAND) = freq(HCLK_PSYS) / n, where n = 1 ~ 8

Values for the high-performance operation:

• freq(ARMCLK) = 1000 MHz

• freq(HCLK_MSYS) = 200 MHz

• freq(HCLK_IMEM) = 100 MHz

• freq(PCLK_MSYS) = 100 MHz

• freq(HCLK_DSYS) = 166 MHz

• freq(PCLK_DSYS) = 83 MHz

• freq(HCLK_PSYS) = 133 MHz

• freq(PCLK_PSYS) = 66 MHz

• freq(SCLK_ONENAND) = 133 MHz, 166 MHz

• PLL

− APLL can drive MSYS domain and DSYS domain. It can generate up to 1 GHz, 49:51 duty ratio.

− MPLL can drive MSYS domain and DSYS domain. It supplies clock, up to 2 GHz and 40:60 duty ratio.

− EPLL is mainly used to generate audio clock.

− VPLL is mainly used to generate video system operating clock, 54 MHz.

− Typically, APLL drives MSYS domain and MPLL drives DSYS domain.

NOTE: Although there is the equation for choosing PLL value, we strongly recommend only the values in the PLL value recommendation table. If you have to use other values, please contact us.

1.3.1 APLL推荐的PLL值

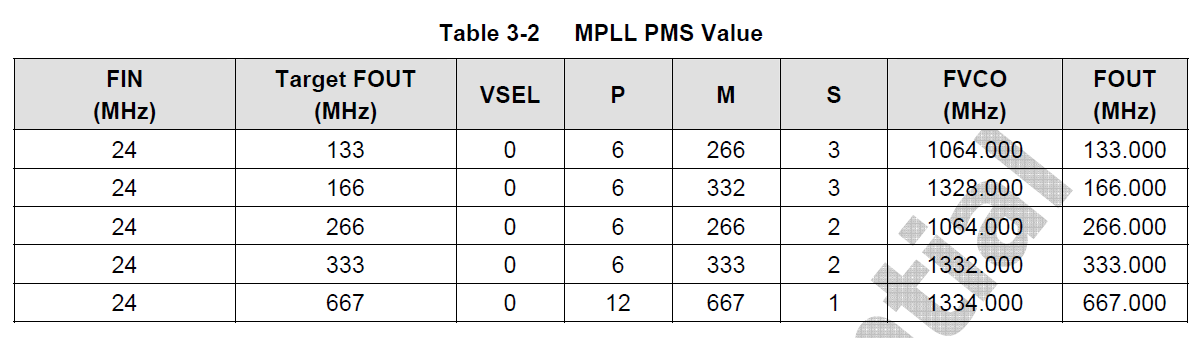

1.3.2 MPLL推荐的PLL值

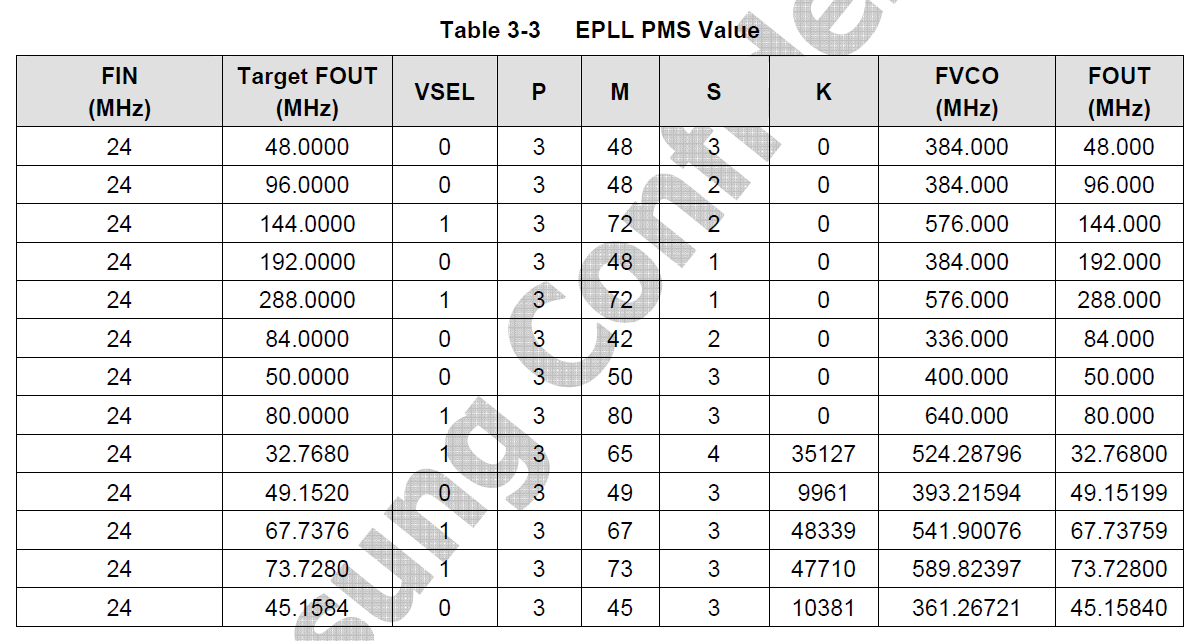

1.3.3 EPLL推荐的PLL值

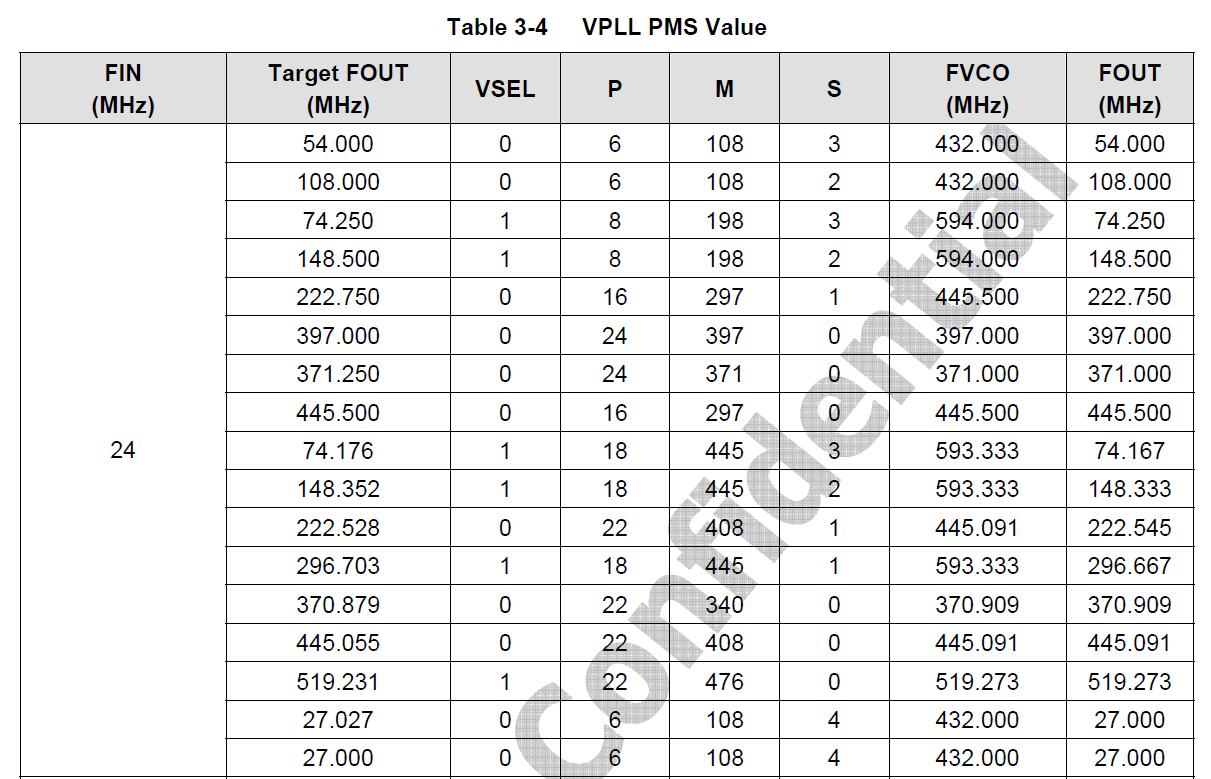

1.3.4 VPLL推荐的PLL值

1.4 时钟描述

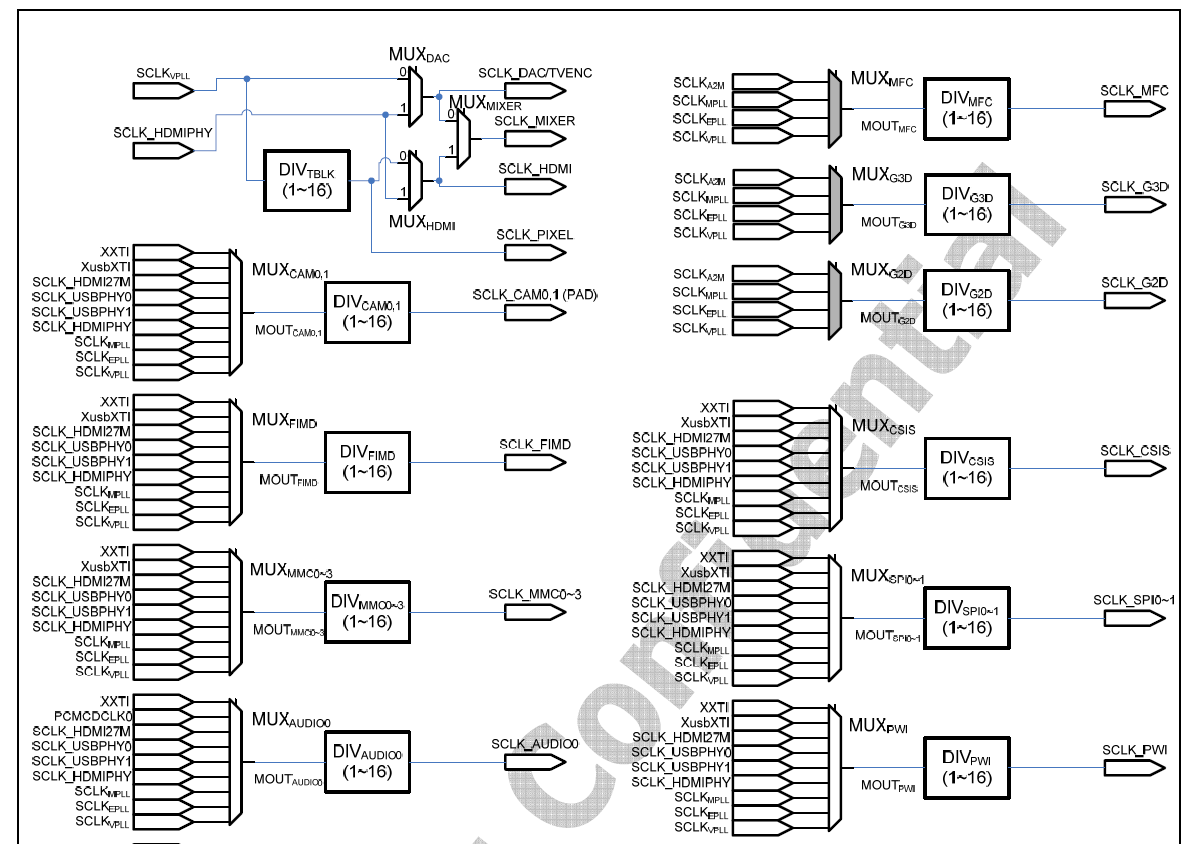

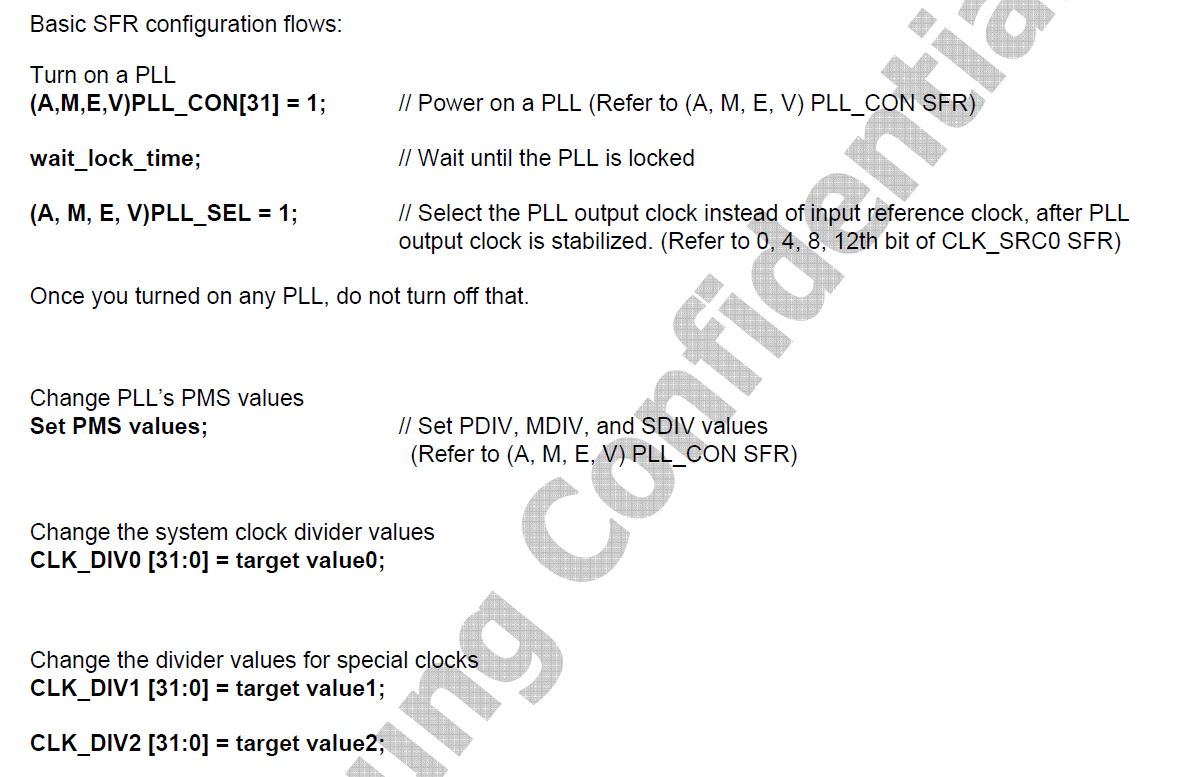

下图描述了时钟产生逻辑的框图,外部的晶振时钟被连接到震荡放大器。PLL将低输入时钟频率转化为S5PV210需要的高的时钟频率。时钟发生器也包含一个内置的逻辑电路来稳定每一次系统复位之后的时钟频率,因为时钟需要一段时间来稳定。

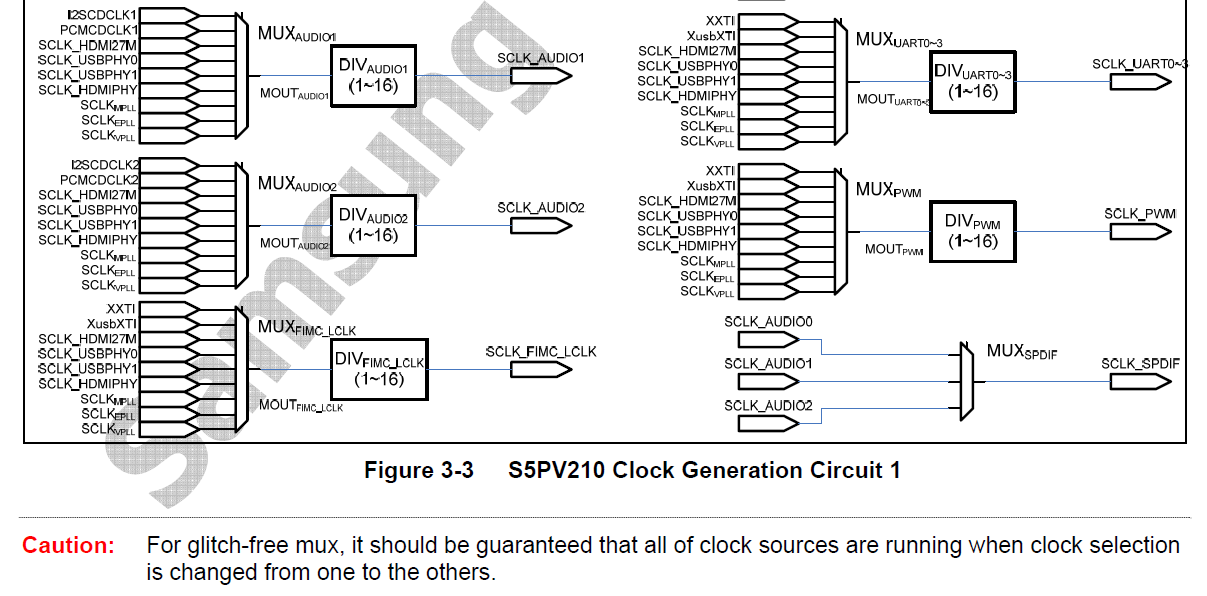

下图描述了两种类型的时钟复用器,灰色的时钟复用器代表免受故障的时钟复用器,如果时钟选择发生改变它是免受故障的。白色的时钟复用器代表非免受故障的时钟复用器,当时钟选择变化时,它会遭受故障。所以再使用每个时钟复用器的时候一定要小心。对于免受故障的时钟复用器,必须保证在时钟选择从一个切换到另一个的时候两个时钟源都是工作的。如果不是那个样子,时钟改变不会完全的结束,从而造成时钟输出的结果是未知的状态。对于非免受故障的时钟复用器,当时钟选择改变的时候它可能会发生故障。为了避免故障的产生,推荐在尝试改变时钟源之前,禁用掉非免受故障时钟复用器的输出。等时钟改变完成之后,用户在使能非免受故障时钟复用器的输出,以至于时钟改变不会造成非免受故障复用器发生故障。屏蔽非免受故障时钟复用器的输出通过设置时钟源控制寄存器来操作。

时钟分频器图示标明可能的分频系数(括号里),这些分频系数在运行时由时钟分频寄存器决定。有些时钟分频器只能有一个值,用户不能够改变它们,寄存器里面也没有它们对应的字段。

- 1

- 2

- 3

- 4

1.5 时钟描述

当时钟改变时遵守以下规则:

• 所有免受故障复用器必须是运行的.

•当一个锁相环是关闭的,你就不应该选择它的输出.

1.51 门控时钟

如果时钟不再需要,S5PV210可以关闭这些时钟,从而减少动态功耗。