关于为何需要设置虚拟时钟,可以参考下面这篇文章:

在接口时序约束中为什么设置虚拟时钟(virtual clock)?

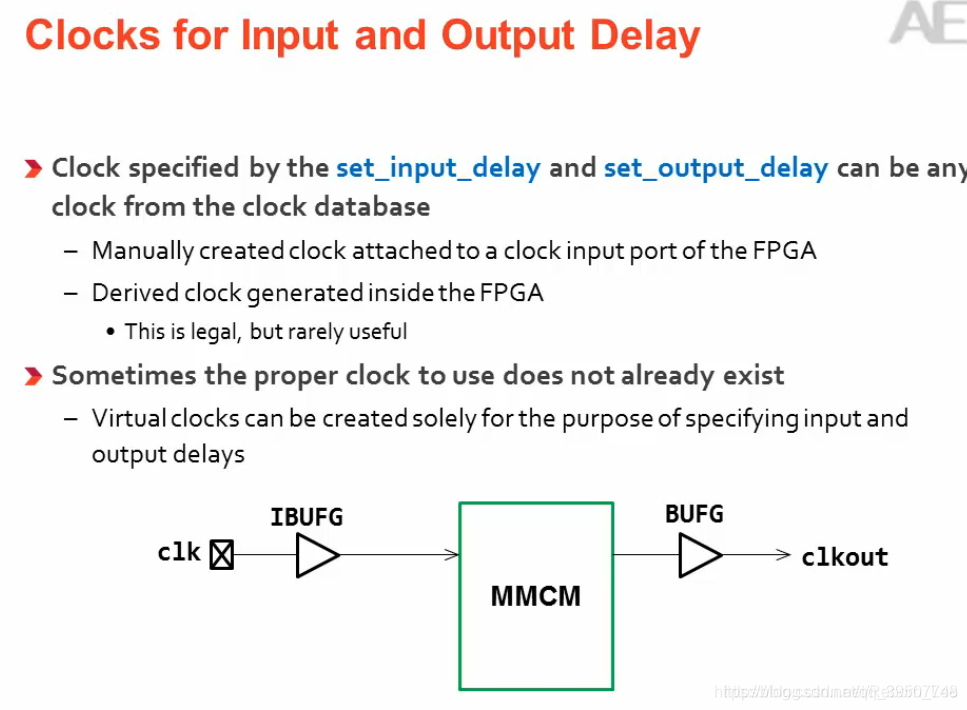

1、用于输入延迟和输出延迟的时钟

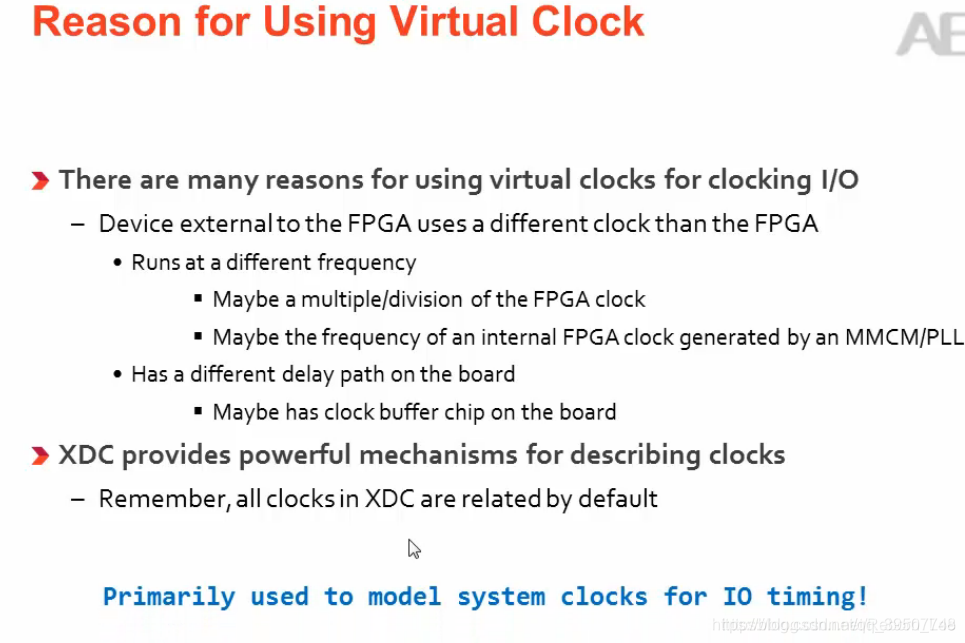

2、使用虚拟时钟的原因

总结一下就是,如果不设置虚拟时钟,那么在设置输入延迟和输出延迟的时候,参考时钟都是同一个时钟;但是该时钟在输入路径和输出路径中所处的情况并不一定是相同的,比如时钟频率不同或者latency不同(分别对应下面的两个example)。

那么这个时候就应该分别考虑各自的实际情况来选择设置输入输出延迟的参考时钟,显然此时共用一个时钟是不行的,因为如果给参考时钟添加latency,势必会对两者都产生影响。那么就需要新建一个虚拟时钟作为参考时钟,然后根据自己路径上的实际情况给虚拟时钟添加latency或做一些其他的设置。

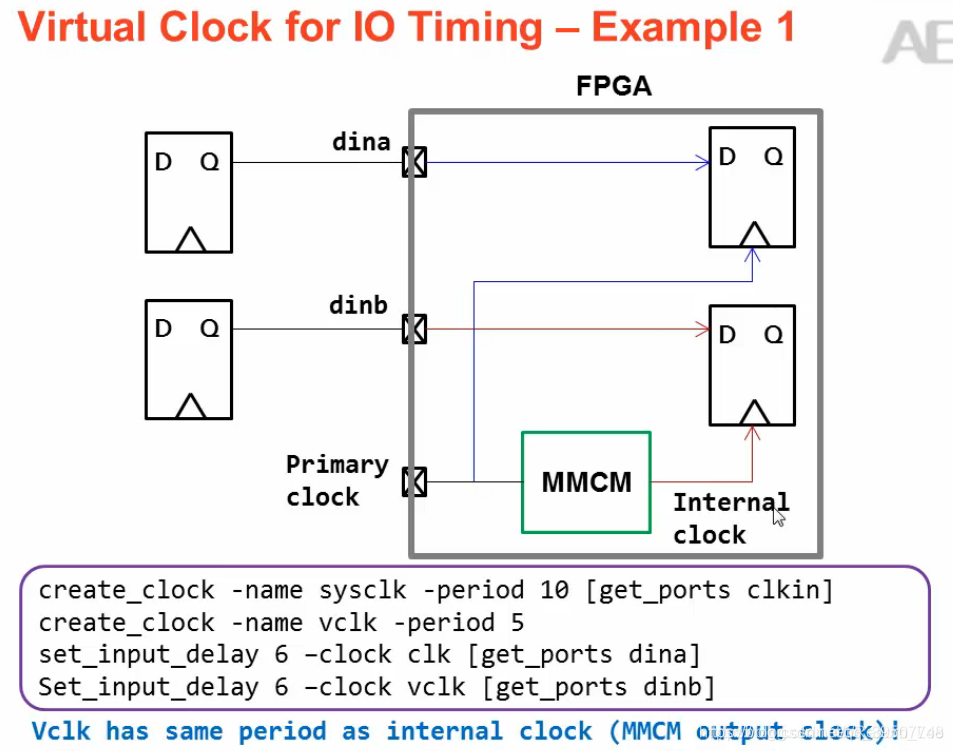

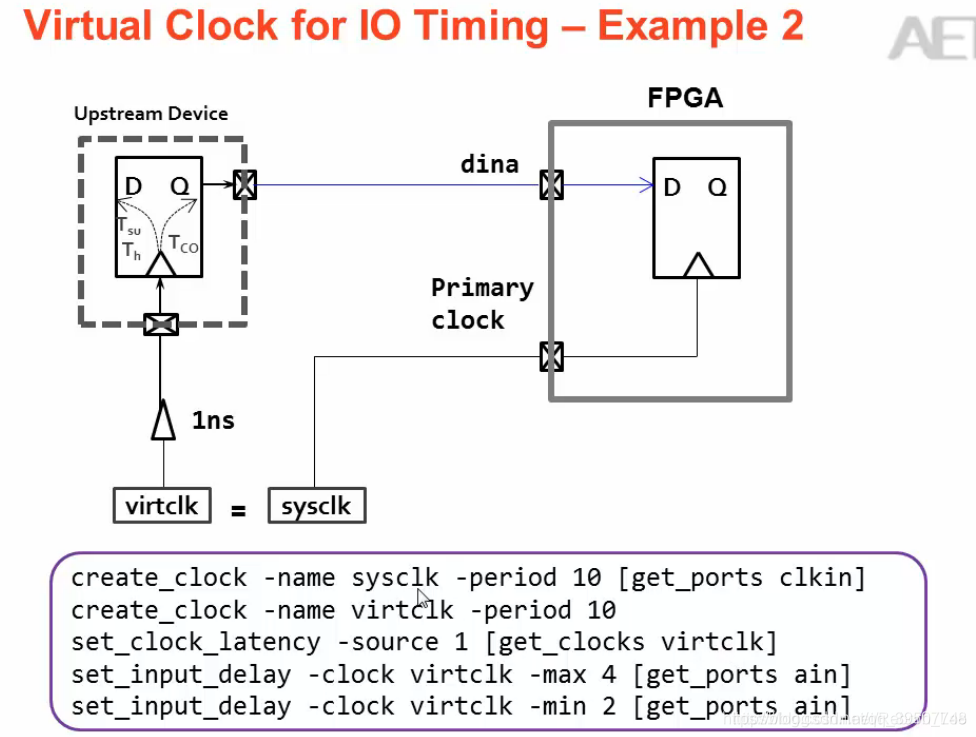

3、IO时序对应的虚拟时钟举例

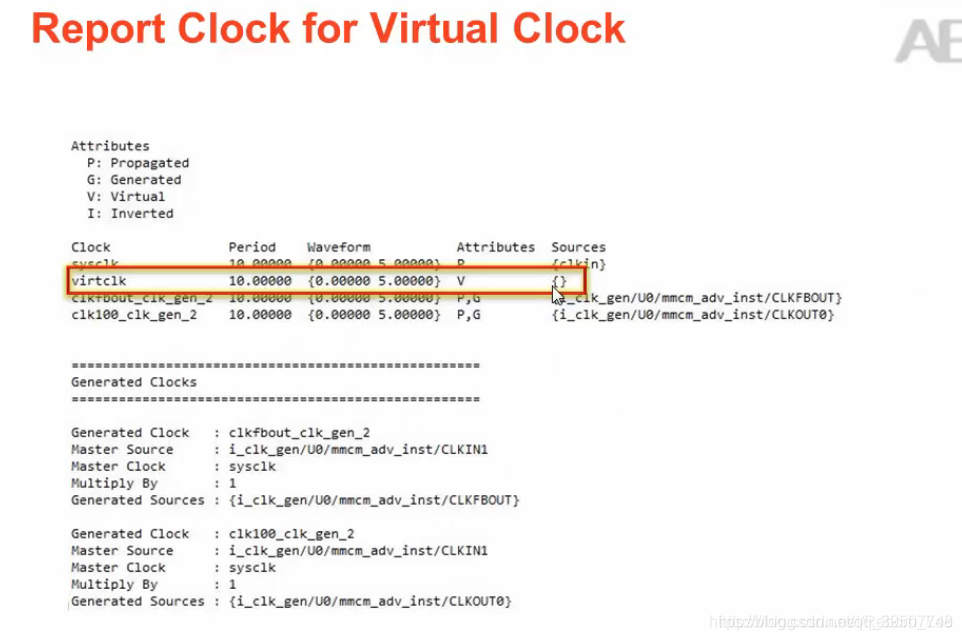

4、创建虚拟时钟

需要注意的是,创建虚拟时钟不需要绑定任何端口,这也是其区别于普通时钟的地方!!!

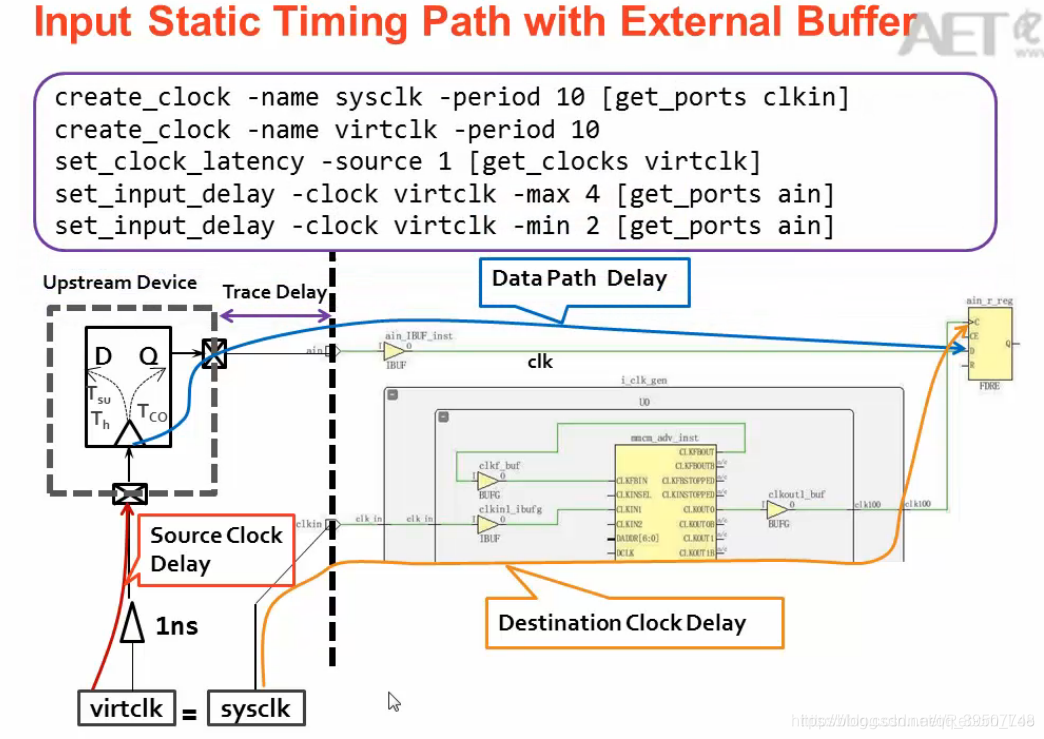

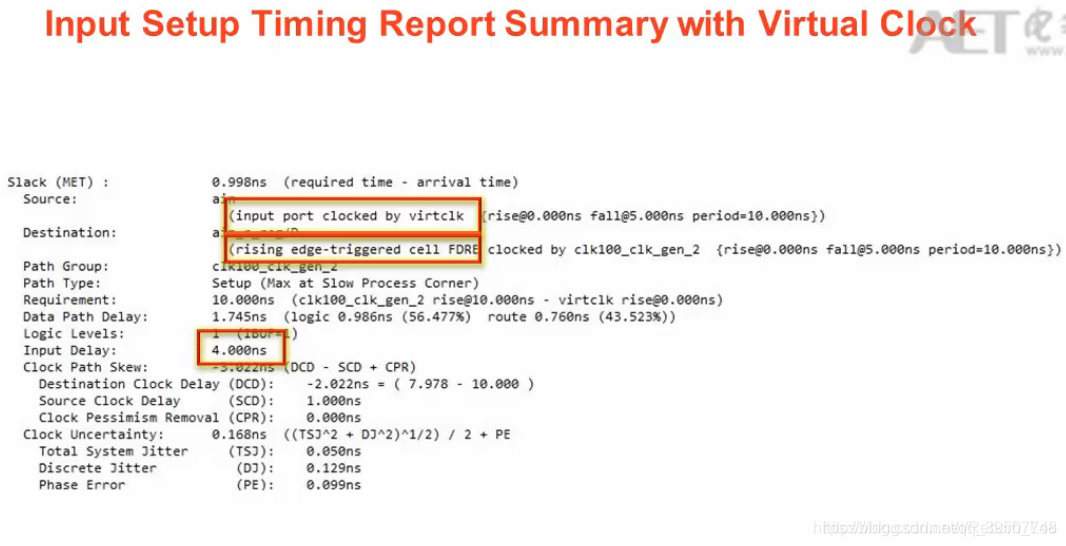

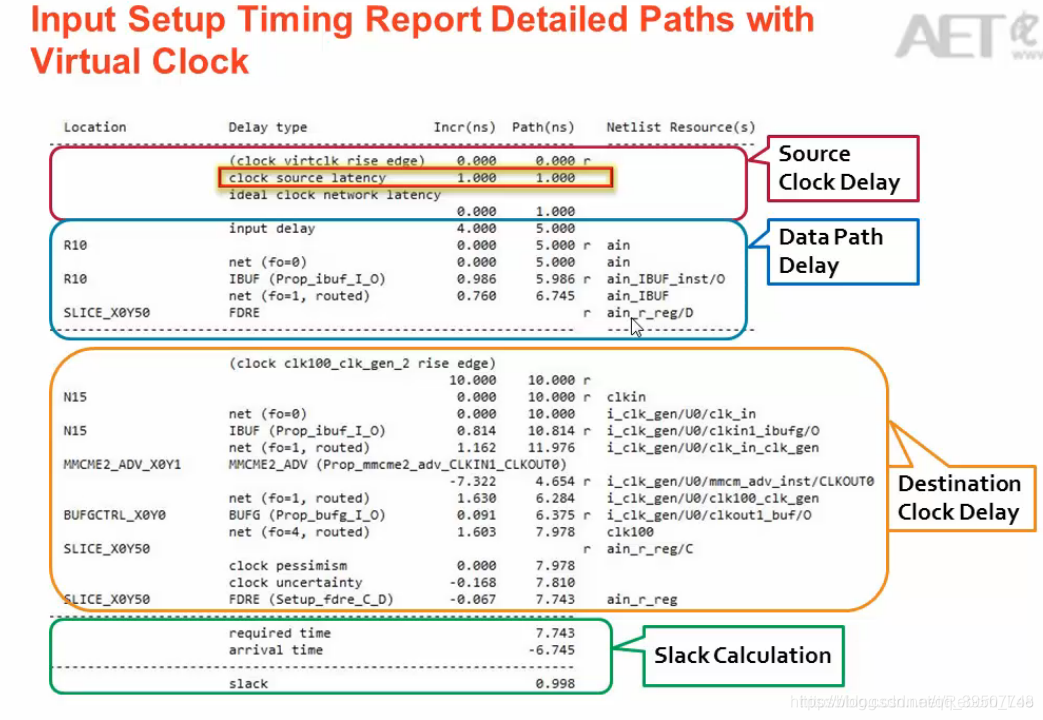

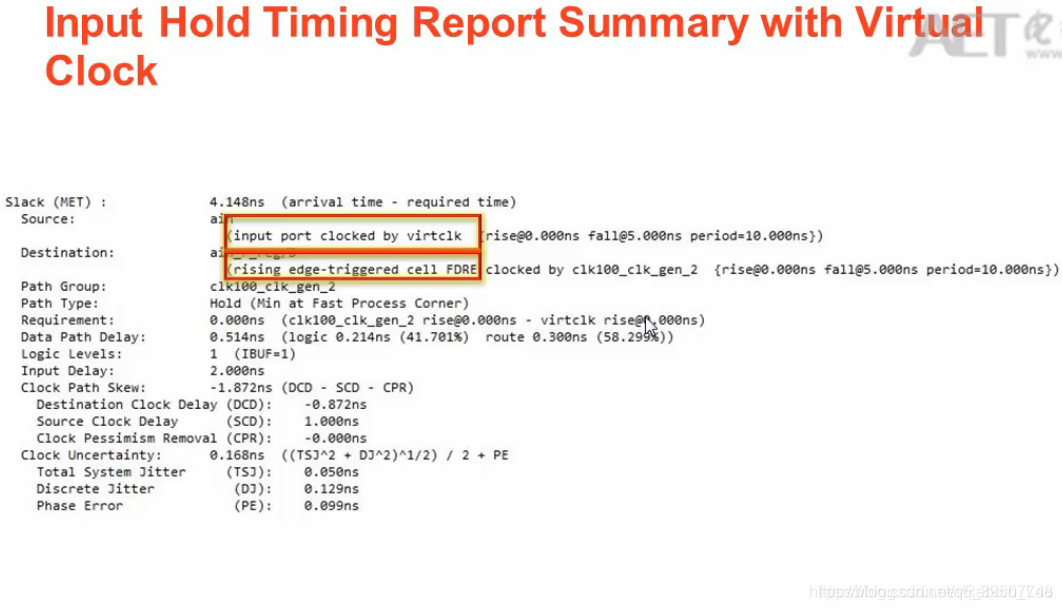

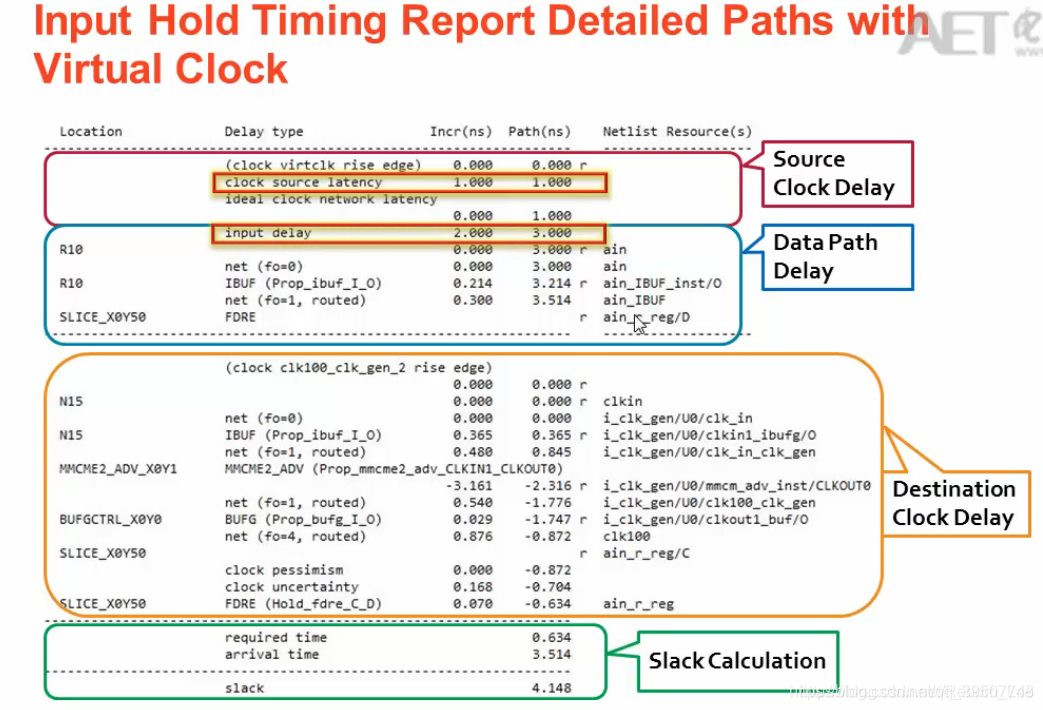

5、含外部buffer的输入静态时序路径及其时序报告

可以看到,和一般情况相比,只是在source clock delay中多了一个clock source latency!!!