主要关于学堂在线的数字电子技术基础(自主模式)的第五章。。。

重点(贫僧在看视频之前会去翻一下配套的书籍,看看要学的章节的习题是什么,这样就大概知道哪里是重点了。。。):

1. 存储器对应的特性表

2. 存储器的数据在什么时候更新(例如是边沿更新还是电平更新)

3. 存储器的基本结构(不用全记,但是要知道去除/增加某个门之后带来的影响,例如D触发器在C1口接上个非门会让数据变成在下降沿的时候更新)

4. 会看波形图,能根据输入的波形来确定输出的波形

5. 会画对应的波形图(画起来麻烦得要死,贫僧选择在电脑上画。。。方便又快捷)

下面这些都是一些笔记,都是概念的东东,如果不理解的话贫僧建议先看下书上对应的例题(顺手做啊,别只是看)并记住对应的特性表(最好还是从定义自己推出来,这样的话就算是不记得特性表了还可以重新推导一遍)。

触发器的由来

为什么需要触发器?

因为现实中有时需要处理这样的问题:

1. 与状态有关,即电路具有记忆功能

2. 输出会直接被输入事件(例如按下按钮)改变,而不是输入的值

例子:需要设计一款电路,能够在按钮按下的时候改变灯的亮灭,如果灯原来是亮的那么按钮按下之后灯应该灭,反之亦然。

组合电路无法直接完成上面的事情,所以需要一个具有记忆功能的器件。

这种具有记忆功能器件的用处:能够存储0和1。(例如Flip Flop就可以存储1位0/1)

话说回来flip flop直译就是人字拖,自己体验一下:

图片来自网络的说。

其实贫僧更加喜欢把它脑补成噬尾蛇,因为理想状态下只要状态没有更新,存储在触发器里面的数据是永远不变的:

(其实只是觉得数字电路有点像炼金术阵/魔法阵/玄学)

门电路与触发器的关系

用来1位二进制信号的期间的特点:

1. 有两个能自行保持的状态

2. 根据输入信号可以置成0/1

分类方式:

1. 按触发方式分(电平、脉冲、边沿)

2. 按逻辑功能(RS、JK、D、T)

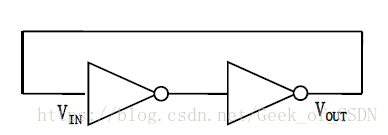

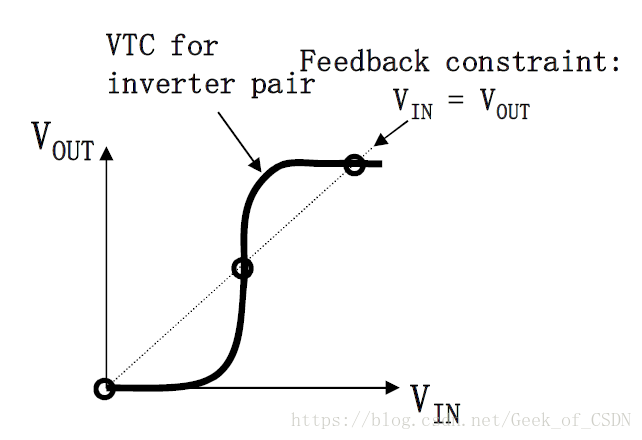

一种最简单的触发器就是用两个非门搭起来的。

纯粹门电路组成的组合电路实现记忆功能的方式:正反馈。

上面是对应的可能出现的电压,其实就是反相器的电压,具体看第三章。

这样的电路其实比较稳定,因为如果取到了中间那个点,因为正反馈的存在电压要么向上要么向下走。例如可能会有一个正扰动,让输入电压稍微升高,那么输出会降低,下一级的反相器输出会增高,叠加到输入里,这样就会直接让电压提升到高电平状态。所以高低两种电平的地方会比较稳定,而如果取值在中间反而会不稳定,这样就为这个电路的记忆功能(确保记忆的是0/1,而且不需要外界输入来保证状态不变)提供了保障。

基本SR锁存器

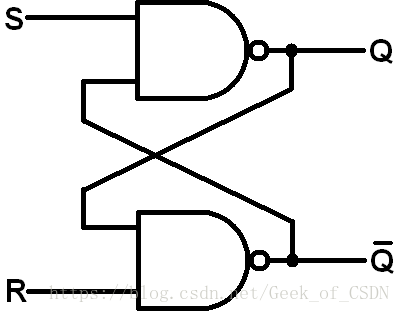

这个电路由两个或非门构成:

优点是引入了两个输入接口

,如果这两个输入接口输入的是0,那么就变回上面的反相器。

把上面的电路换种画风就可以变成:

那两个输入接口变成了

和

,存储的数据是Q,相反的就是Q’。

是0的时候Q直接变成0,所以这个接口叫Reset Direct(直接复位)(这时

应该=0)。

=1的时候

应该=0,这样可以直接让Q=1。

就是说通过

可以置0,

可以置1。

置完之后两个输入接口变回0,相当于最上面那两个反相器连起来的电路(就是

和

都是0的时候保持过去状态)。不存在两个输入同为1的情况。。。

Q*就是更新后的输出。

约束条件:

。

注意:在

都是1的情况下输出

,这个是定义出来的的,实际情况其实是不确定的(但是做题都是按照这个定义来做的,这个地方在做配套书后面的练习的时候,要画波形图的时候会用到)。

动作特点:任何时刻输入都可以直接改变输入出状态。

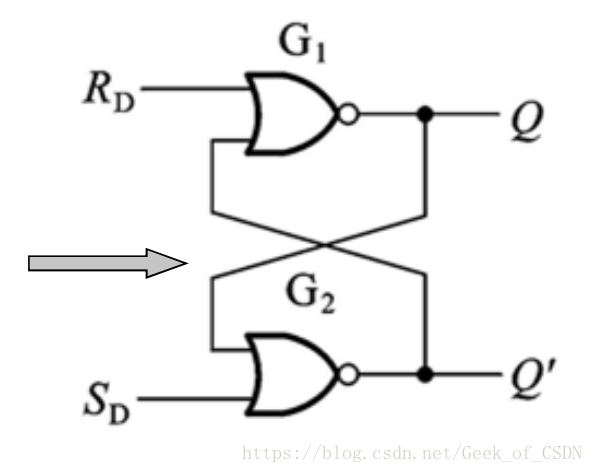

除了用或非门还可以用与非门来搭这个电路。

和上面的类似,只是这次

=0才是对应的置1,置0也是差不多。注意不要让两个输入同时为0。其实看上面的波形图可以看到输入同时为0的时候也不是不能确定输出的值,只是会出现矛盾。

小技巧:

其实通常贫僧都是记这个锁存器的名字的:Set-Reset Latch,重点是Set-Reset,set脚高电平reset脚低电平那就输出置1,reset脚高电平set脚低电平就置0,都是0就保持输出不变,都是1就

都输出0(这个是定义,如果是在S和R脚加了反相器或者SR触发器是用与非门搭起来的话要注意反过来,而且在

都是低电平的时候输出是

是高电平)。

动作特点:

任何时刻输入都可以直接改变输出。

因为上面的那个SR触发器太敏感了,所以做了点改进,引入了触发信号/时钟信号CLK。改装之后的触发器只有在触发信号来的时候才能够改变状态(通常有三种触发:电平、边沿、脉冲触发)。

电平触发的触发器

电平触发的RS触发器

结构:

脑补成SR锁存器左边加上一个输入控制电路,CLK=0的时候左边的控制电路输出一直是1,所以会让输出保持原来的状态(看SR那里的特性表就可以理解了)。

动作特点:在CLK=1的时间里输入改变输出状态。

贫僧是直接把这种触发器和前面的SR触发器结合在一起记忆的,因为只是输出状态变化的时间段变了,逻辑还是一样的。

缺点:

可能会因为在CLK变回低电平前的一瞬间收到干扰导致输出状态改变(下图的S):

加上异步置位、复位的电平触发SR触发器

大概长上面这样。

其实只是加了个在

或

加入低电平就可以立刻把输出(

)调整到1或者0的功能,而且不受时钟信号控制(异步)。平时正常工作的时候应该给这两个脚高电平。

电平触发的D触发器

上面那种触发器是双端的,但是有时客户会会提出要用单端的触发器,于是就有了D触发器(其实就是拿SR来加个反相器):

上面虚线框中的就是新加上的反相器。

D触发器的特性表

| CLK | D | Q | Q* |

|---|---|---|---|

| 0 | x | 0 | 0 |

| 0 | x | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

就是D输入0就让输出置0,D输入1就让输出置1。

为了进一步提升抗干扰能力,就又改进了一下,变成了边沿触发的触发器

边沿触发的触发器

用两个电平触发的D触发器合成边沿触发器!

其实最关键的就是跳⭐变的一瞬间,在跳变前CLK是低电平,所以

是高电平,

,

保持原来的状态不变。然后在跳⭐变的一瞬间

就会变成0,

的输出定在了跳变时的状态,

变成1,所以

会变成和

一样的状态。

抽象上面一段话,就可以浓缩成这样一句话:

新合成的边沿触发器的输出信号状态会更新成CLK上升沿出现时的输入信号状态。

所以边沿触发器的特性表就是:

X代表任意状态,就是可以是0也可以是1。

然后就是一个小特点:如果把上面a图里面的CLK输入端的一个反相器去掉触发器就会变成下降沿触发,这样的话要在CLK输入端画个小圆圈(特性表里面CLK信号用↓来表示,因为变成了下降沿触发)。

内部的电路图

添加异步功能

如果要添加的话就要把上面图里面的反相器改成或非门(因为

和

是以高电平作为置1和置0的输入信号的)(平时这两个脚置低电平,因为原来的输入输出要有0和1变化,所以可以直接对照或非门的真值表看出这两个脚平时要高还是低电平)。

动作特点:

输出只取决于在信号线信号跳变(触发分上升沿触发和下降沿触发)的那一瞬间的输入信号状态。

脉冲触发的触发器

脉冲触发的SR触发器

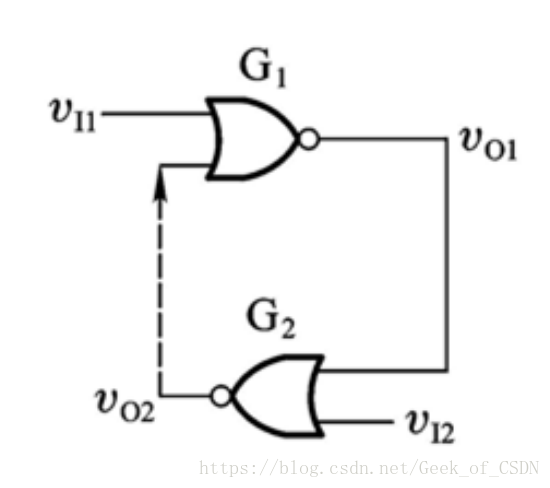

把两个电平触发D触发器换成电平触发的SR触发器,就会变成:

这种触发器的特点是输出端的状态之改变一次,而且发生在CLK的下降沿,但是不能治看下降沿那一瞬间的状态,因为在CLK高电平的期间

是被S和R控制的,所以要看整个高电平期间的SR状态来看最终的Q状态(下降沿来的时候Q会变成和

一样的状态,所以只要分析高电平期间的S、R状态对应的输出就可以了,还是SR锁存器那套,S1R0Q1,S0R1Q0,SR=0)。

上面这种特性表对应的脉冲触发的SR触发器的图标是这样的:

注意:

框里面的

代表高电平为有效点评(CLK高电平时接受输入信号),输出端状态的变化发生在下降沿。

上面的电路还是要保证SR=0,因为在S=R=1时,没有办法再CLK的有效电平消失或者SR的高电平同时回到低电平时确定触发器的状态。但是如果能够在S=R=1的时候把Q和Q’接回去到输入端用Q‘代替S输入信号,Q代替R输入信号,就可以允许S=R=1(不懂的话看图)。

上面的图有点不清楚,其实黑色的地方写了S和R。

再来一张图:

J和Q’和CLK其实是连在一个与非门上的,所以只需要其中一个线是0那么与非门输出就会变成1,K和Q和CLK也差不多,这样在J = K = 1的时候只会出现下面两种情况:

1. Q = 0,

被Q的低电平封锁(与非门的情况就是只要输入存在0的时候输出1),只有

输出0,所以主触发器(就是左边那个触发器,整个JK触发器可以看成两个SR触发器组成的)置1,CLK=0之后从触发器(就是右边那个触发器)输出状态变成主触发器的状态(就是状态从左边传递到了右边的触发器),因此输出的新状态Q*=1

2. Q = 1,那么

被Q’的低电平封锁,输出1,只有

能够输出0,所以主触发器被置0,CLK=0后从触发器状态更新成主触发器的状态(主触发器状态传递给了从触发器),所以Q*=0

(如果不清楚为什么

输出0,主触发器就被设置成了1的话就看下面的补充部分)

JK触发器的特性表:

补充:

用与非门合成的SR触发器

其实是怕读者看完了上面又不记得了才补充在这里的。。。其实上面都有写,这里只是重新复制下来。

与非门合成的SR触发器的特性表:

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | |

| 0 | 0 | 1 |

①当输入 和 的0状态同时消失之后状态就会开始不确定,其实不是前面普遍定义好了的1状态