这一章主要内容是时序逻辑电路基础知识,介绍它的组成,分析设计和冒险,以及其中的两个最常用的存储部件:锁存器和触发器。

由于这一章内容较多且很重要,所以分为两讲来总结。

今天这一讲主要来总结基础知识、锁存器和触发器。

如有错误,欢迎指正,我会及时地更正错误。

废话不多说,现在开始

时序电路

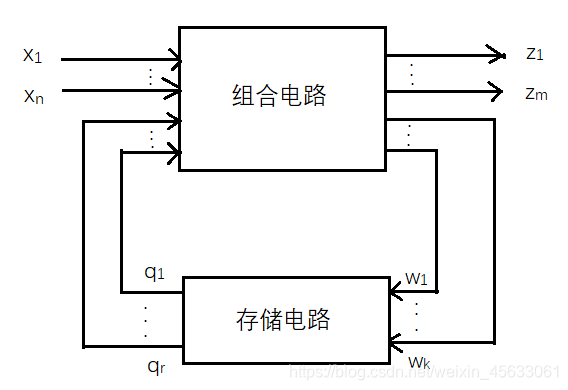

结构模型

外部输入信号:x1…xn

外部输出信号:z1…zm

驱动信号(存储电路的输入信号:即组合电路的部分输出信号):w1…wm

状态变量(存储电路的输出信号反馈到组合电路的输入端):q1…qr

时序电路结构特点:

1. 具有存储电路

2. 具有反馈支路

时序电路与组合电路不同点:

时序电路在组合电路的基础上多了存储电路。

存储电路由存储器件组成,能存储一位二值信号的器件成为存储电源电路。

常用的是:锁存器、触发器

描述方法

逻辑方程

在时序电路中,所有的输入和输出都是时间的函数(时间是离散的时间)

所以有了一下三组方程:

1. 输出方程:Z(tn)=F[X(tn),Q(tn)]

2. 驱动方程:W(tn)=G[X(tn),Q(tn)]

3. 状态方程:Q(tn+1)=H[W(tn),Q(tn)]

!在这里插入图片描述

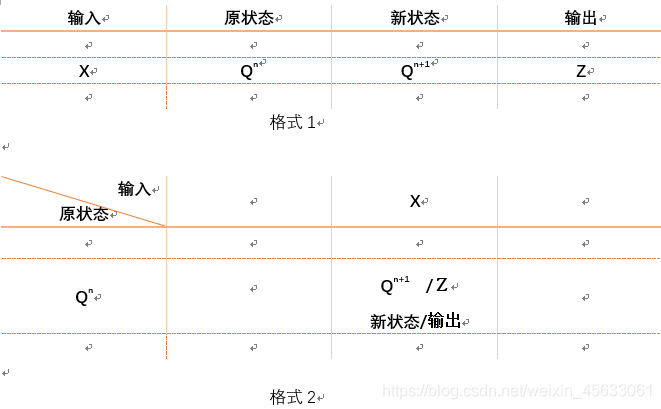

状态表

是个表格,常见两种格式

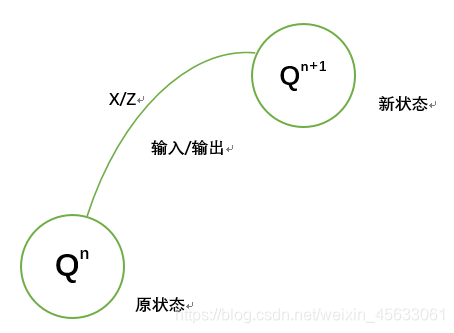

状态图

时序图

波形图

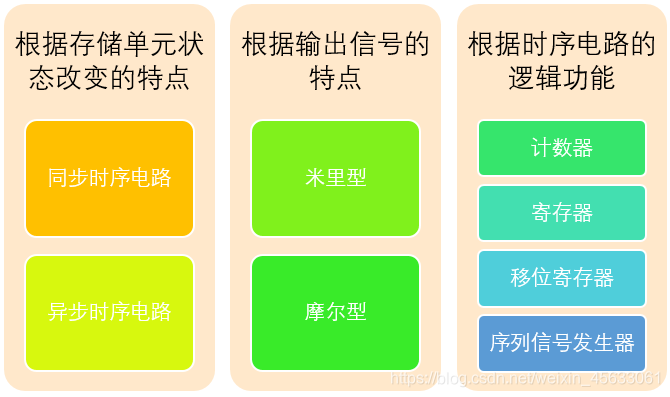

分类

锁存器

一种由激励信号(组合电路的内部输出信号)控制电路状态的存储单元。

普通锁存器

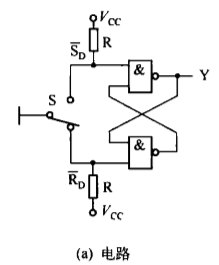

以RS锁存器(Reset-Set锁存器,复位-置位锁存器)来介绍,它是一个最基本的单元。

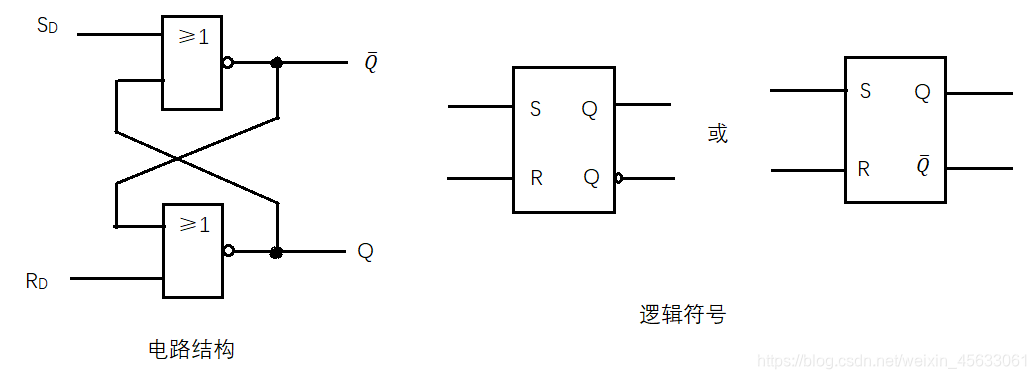

电路结构及逻辑符号

可以用交叉耦合的**或非门(或者与非门)**组成。

(耦合在此就理解为连接吧,输入输出相互联系,相互影响)

SD:置位端(置1端)

RD:复位端(置0端)

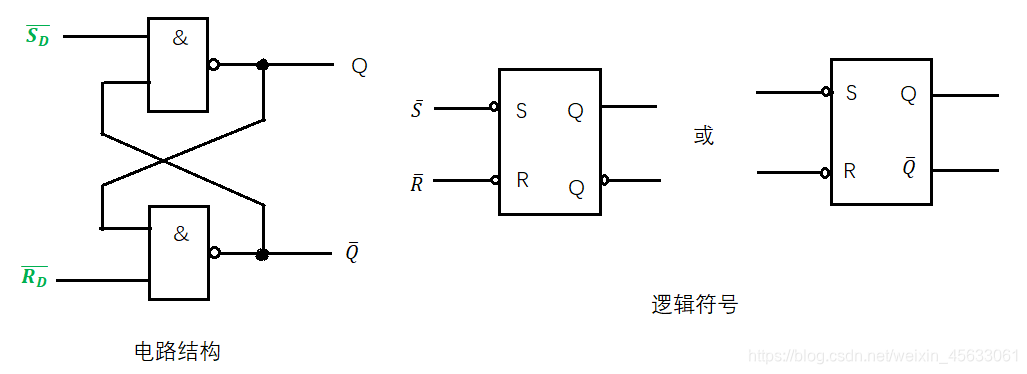

或非门RS锁存器

与非门RS锁存器

与非和或非可以相互转化

对于与非门:由其逻辑表达式可以看出,只要输入端由1(即高电平)就能使其输出为0

对于其两个输出端:

锁存器(或触发器)总是用Q的值来命名:

Q=0:锁存器(或触发器)为0状态(或复位状态)

Q=1:锁存器(或触发器)为1状态(或置位状态)

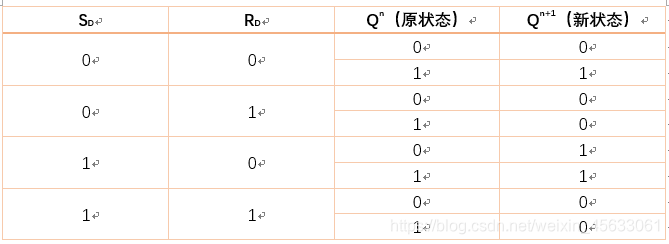

逻辑功能分析

或非RS锁存器

高电平为激励信号,值为1

SD=RD=1时,锁存器处于不正常工作状态,应该禁止使用,即应满足SDRD=0这个约束条件

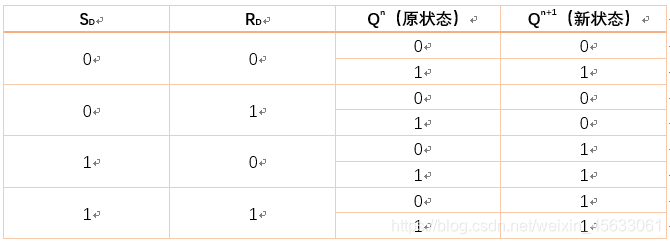

与非RS锁存器

低电平为激励信号,值为1,不过在运用时总是用其反变量,所以反变量为0表示有激励信号

SD=RD=1时,锁存器处于不正常工作状态,应该禁止使用,即应满足SDRD=0这个约束条件

注意在判断新状态时,要先看你能确定下来的那个值,再根据这个去判断其他

所以不论是或非门锁存器还是与非门锁存器,都应满足SDRD=0这个约束条件

逻辑功能描述

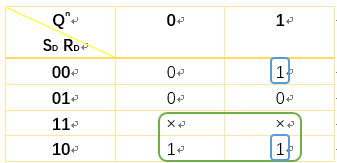

- 特性表

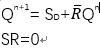

- 特性方程

由卡诺图和约束条件可得:

特性方程为:

- 状态图

门控锁存器

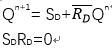

门控RS锁存器

在RS锁存器的基础上,有一个特定的控制信号去控制锁存器状态转换的时间。

当输入信号发生改变时,即信号不稳定时,禁止锁存器状态转换;

当输入信号稳定以后,锁存器开始做出响应。

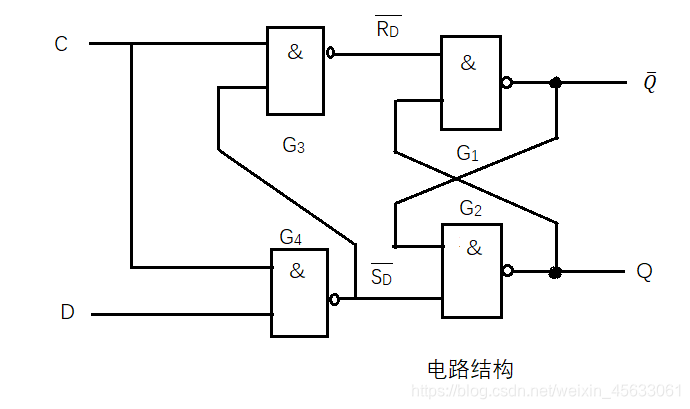

电路结构及逻辑符号

电路分为两部分:1. G1、G2构成的RS锁存器;2. G3、G4构成的输入控制门电路

C:控制信号

逻辑功能分析

RD=RC, SD=SC

当C=0时,RD=SD=0, 锁存器状态Q不变

当C=1时,RD=R,SD=S, 等效为一个输入信号分别为R和S的RS锁存器

逻辑功能描述

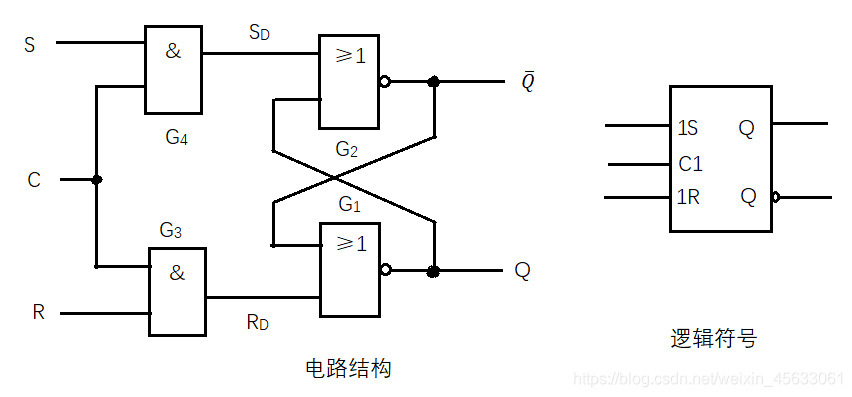

- 特性表

- 特性方程

当C=1时,特性方程:

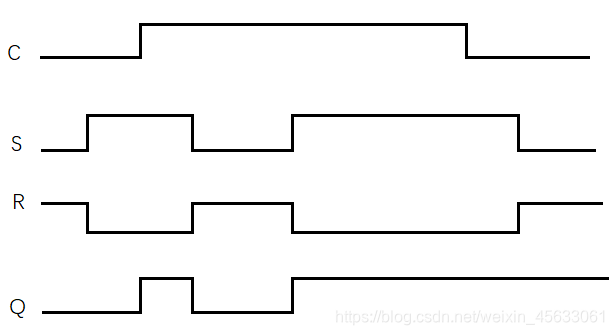

- 工作波形

门控D锁存器(双稳态锁存器)

一种能够存储数据的器件

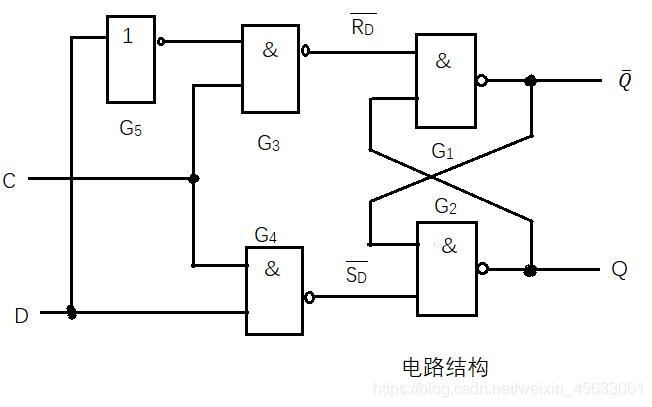

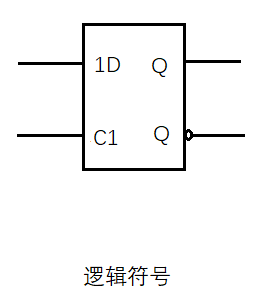

电路结构及逻辑符号

简化后的电路图

逻辑符号

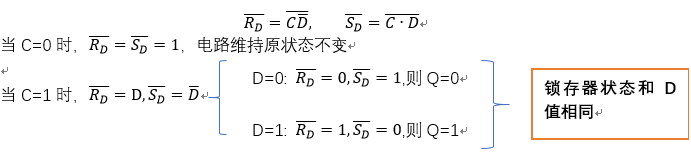

逻辑功能分析

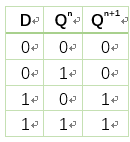

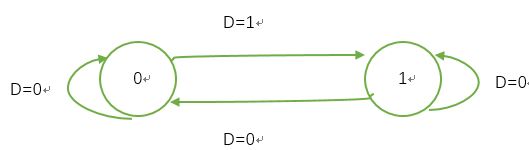

逻辑功能描述

- 特性表

- 特性方程

Qn+1=D

- 状态图

触发器

锁存器的空翻:输入信号若发生多次变化,输出状态也可能发生多次变化

主从触发器

主从RS触发器

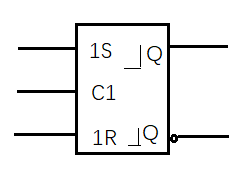

- 逻辑图及逻辑符号

逻辑图

CLK:时钟信号

逻辑符号

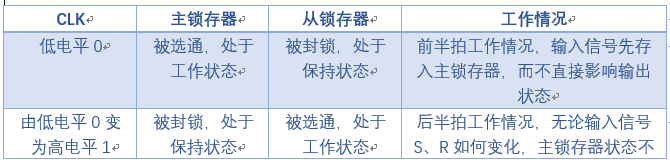

2. 工作原理

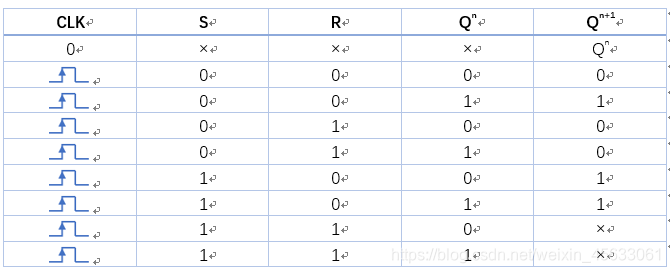

- 逻辑功能描述

①特性表

②特性方程

与RS锁存器相同

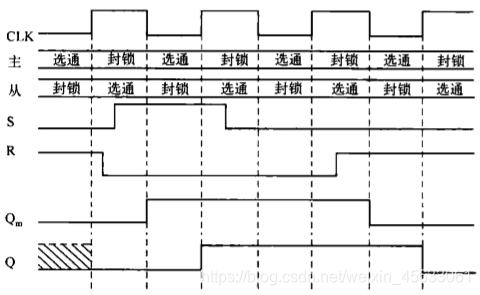

③波形图

主从D触发器

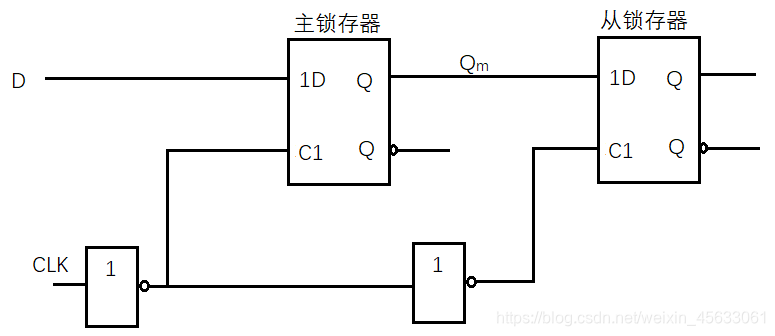

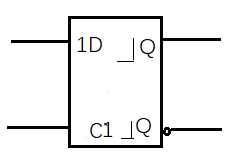

①电路图及逻辑符号

电路图

逻辑符号

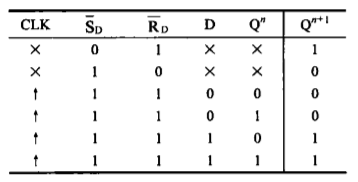

②工作原理

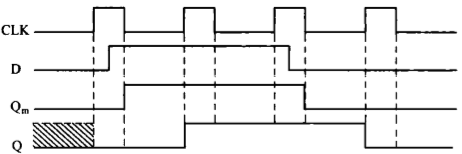

CLK=0时,主锁存器被选通,Qm=D,从锁存器保持原状态不变

CLK由0变1时,主锁存器被封锁,从锁存器被选通,从锁存器按照与主锁存器相同的输出状态输出

③逻辑功能描述

特性方程:Qn+1=D

波形图:

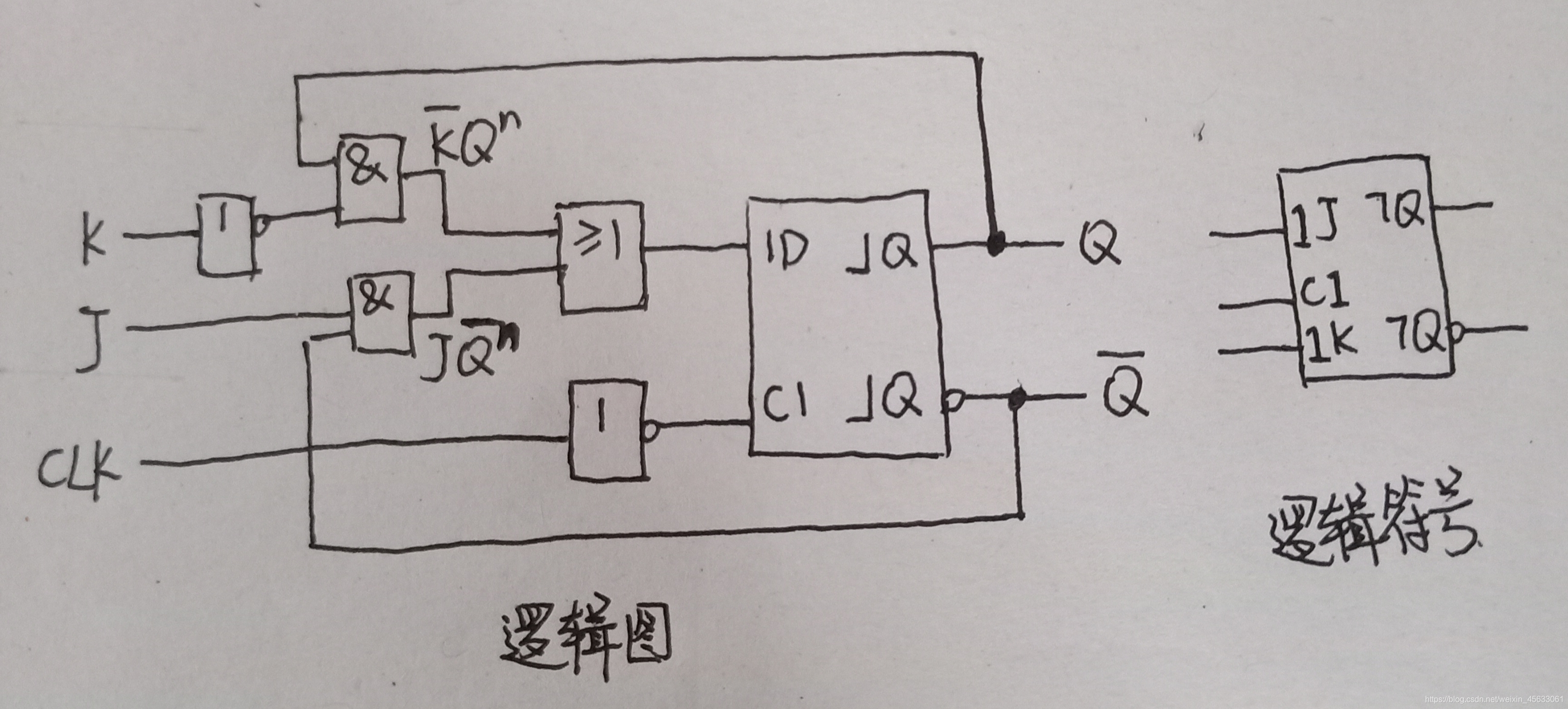

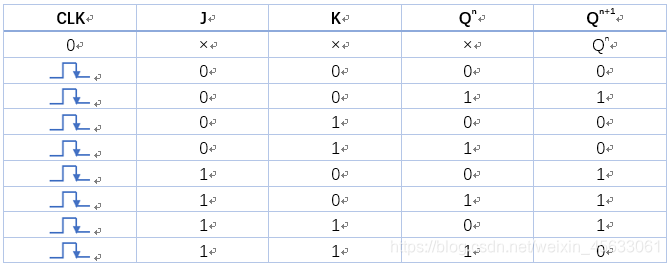

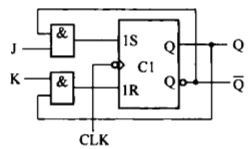

主从JK触发器

克服主从RS触发器CLK=0时,输入信号必须遵循SR=0这一约束条件

- 逻辑图及逻辑符号

- 工作原理

再J=K=1时,CLK由1变为0时,输出状态翻转一次(即0变1,1变0),这样就去除了RS触发器中存在的约束条件

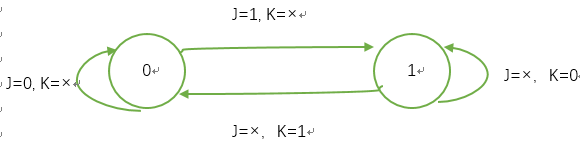

- 逻辑功能描述

①特性图

②特性方程

③状态图

主从触发器缺陷

输入数据必须保持恒定,如果有干扰,将会导致状态的错误转换

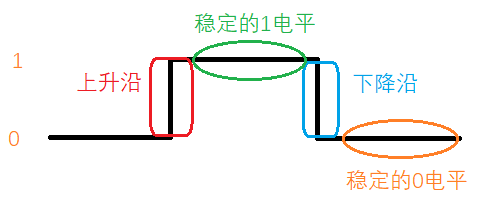

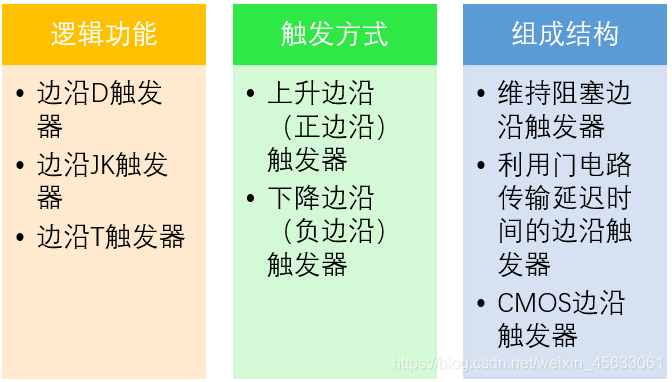

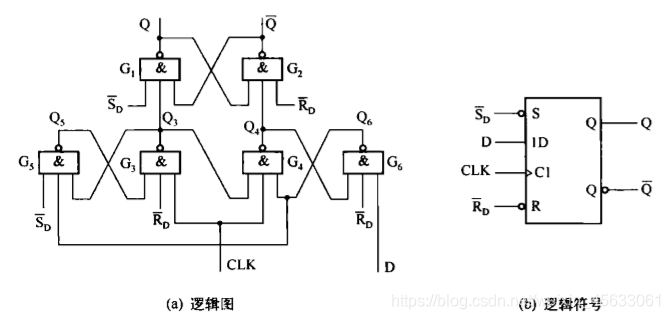

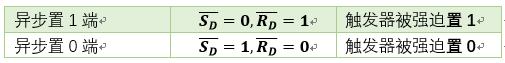

边沿触发器

边沿触发器:

只在上升沿或下降沿及跳变前后极短的一段时间内,触发器才能接受数据,并使输出状态转换。

而在稳定的1或0电平期间,输入数据都不能进入触发器,影响不了输出。

特点:只要求在极短的时间内输入数据保持稳定,提高了触发器的抗干扰能力

分类

维持阻塞边沿触发器

- 电路结构及逻辑符号

上升边沿触发的维持阻塞边沿D触发器(正边沿触发器)

2. 工作原理

3. 逻辑功能描述

①特性表

②工作波形

CMOS边沿触发器

介绍CMOS上升沿D触发器

- 电路结构

触发器使用中的几个问题

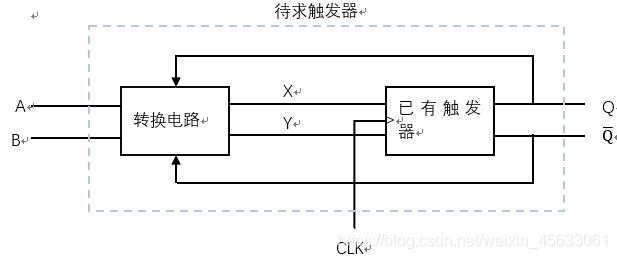

触发器逻辑功能的转换

有时需要将已有触发器转换为待求触发器:即在已有触发器的输入端加上一定的转换逻辑电路

转换的关键:求转换电路

驱动方程:

X=f1(A,B,Qn)

Y=f2(A,B,Qn)

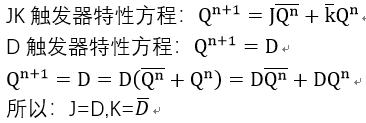

代数法

通过比较已有触发器和待求触发器的特性方程,求出驱动方程

举个例子:将JK触发器转化为D触发器

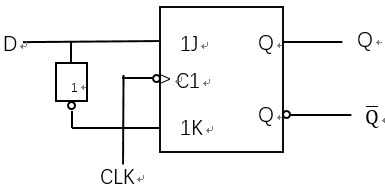

图表法

步骤:

- 列出待求触发器的特性表

- 逐行列出已有触发器所需的驱动信号

- 根据驱动信号画出逻辑图

还是来看个例子:把RS触发器转换为JK触发器

4. 特性表

5. 由卡诺图得到驱动方程

注意:还要满足约束条件SR=0

6. 画逻辑图

触发器的脉冲工作特性

以下无需计算,查相应器件手册可得。

1. 建立时间(tset)

为了使触发器做好触发准备,要求输入信号在时钟脉冲的边沿到来之前,提前一段时间到来。

提前的这段时间叫做建立时间,用tset表示

2. 保持时间(th)

为保证触发器可靠翻转(0变1,1变0),在时钟脉冲到达后,输入信号必须保持一段时间不变。

这段时间成为保持时间,用th表示

3. 传输延迟时间(tPHL tPLH)

从时钟脉冲边沿到达到触发器的新状态稳定建立起来所需要的时间。

tPHL:输出端由高电平变为低电平的传输延迟时间

tPLH:输出端由低电平变为高电平的传输延迟时间

一般情况下,tPHL≠tPLH

4. 最高时钟频率(fmax)

在保证触发器可靠翻转的条件下,所允许的时钟频率的一个上限值。

5. 脉冲宽度

为保证时序逻辑电路能够正常稳定地工作,要求输入信号的脉冲宽度大于最小脉冲宽度

最小脉冲宽度由它的最小高电压时间和最小低电压时间来决定

6. 功耗:总功率消耗

根据该参数可确定所需直流电源的输出容量

触发器应用举例

-

消颤开关

-

异步脉冲的同步化

-

单脉冲发生器

可能有的地方写的不够详尽,还请多多见谅,我还会不定期地进行更新补充。