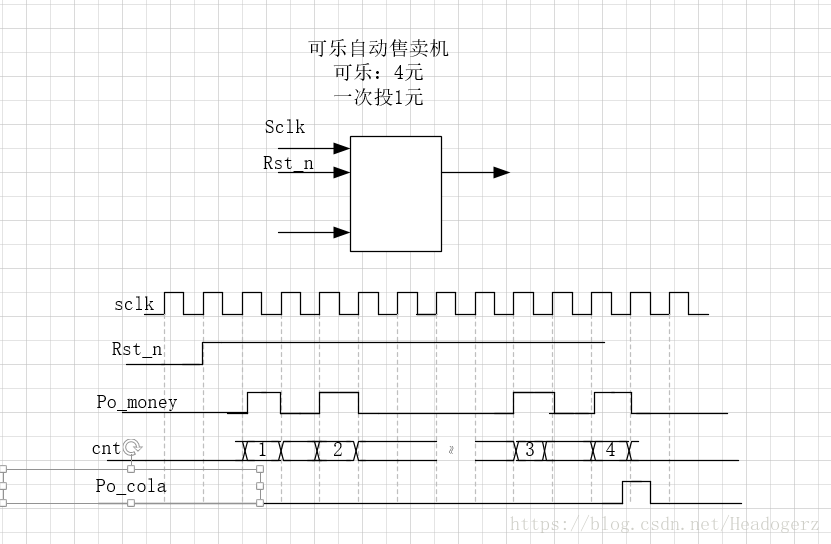

第一步,先将要求原理画出来。

第二步,将以上原理用硬件语言描述出来。

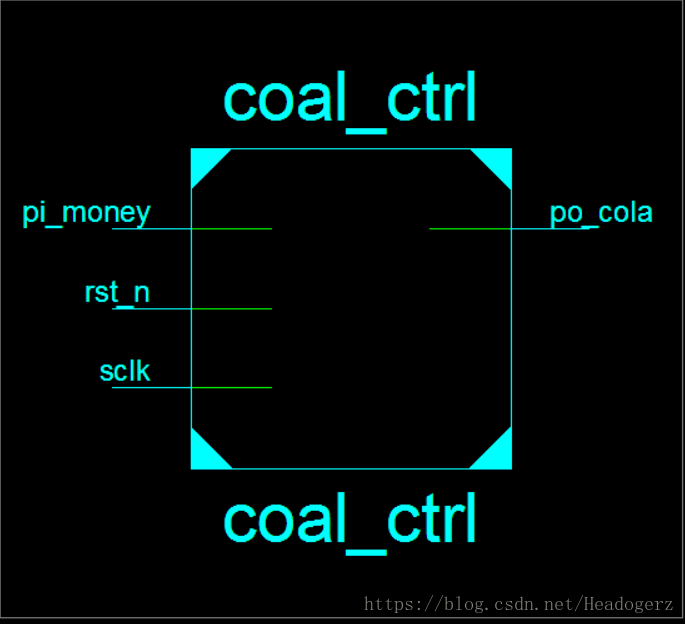

module coal_ctrl(

input wire sclk,

input wire rst_n,

input wire pi_money,

output reg po_cola

);

reg [1:0] cnt;

always@(posedge sclk or negedge rst_n)

if(!rst_n)

cnt<=1'b0;

else if(pi_money==1'b1)

cnt<=cnt+1'b1;

else if(cnt==2'b11&&pi_money==1'b1)

cnt<=cnt;

always@(posedge sclk or negedge rst_n)

if(!rst_n)

po_cola<=1'b0;

else if (cnt==2'b11&&pi_money==1'b1)

po_cola<=1'b1;

else

po_cola<=1'b0;

endmodule需要说明的是,本人在第一次写模块的时候。由于基础薄弱,以为模块的if条件不能用输入信号,导致牛角尖。导致最后只能对时钟信号计数。所以触发条件是可以用输入信号的。

第三步,写测试模块。

`timescale 1ns/1ns

module tb_cola_ctrl();

reg sclk;

reg rst_n;

reg pi_money;

wire po_cola;

initial

begin

sclk=0;

rst_n=0;

pi_money=0;

#20

rst_n=1;

end

always #20 sclk=~sclk;

always #50 pi_money=$random; //说明随机产生的数据,可能大于1由于定义pi_money是一个位宽,所以截留末位0或者1

coal_ctrl cola_ctrl_inst(

.sclk (sclk ),

.rst_n (rst_n ),

.pi_money (pi_money ),

.po_cola (po_cola )

);

endmodule

代码一定要多敲,测试文件也要手写。上面的代码虽然没问题,但在本人调试的时候,module都拼写错误,导致simulation测试的时候,测试模块与功能模块并行。而且在例化的时候,复制错名字。

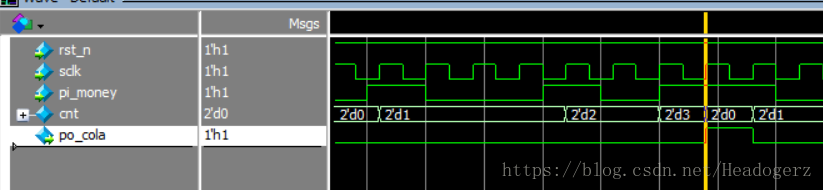

第四步,将测试结果和功能模块P出来。