这几天事情有点多,参加了数学建模选的B题,然后没有更新。

下边是之前那个vhdl计数器,之前没做起来,led总是不跳变,现在发现原因了,用两个if写就行了

下面这个程序功能:

对clk进行计数,10个clk的跳变,一次led的跳变,为了看的更加清晰,加入了cout,用以看cnt的变化。所以加入了arith和usigned。

--ujs-lili

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_arith.ALL;

use IEEE.STD_LOGIC_unsigned.all;

entity counter1 is

port(clk,rst:in std_logic;

led:out std_logic;

cout:out std_logic_vector(3 downto 0));--端口声明

end counter1;

architecture Behavioral of counter1 is

begin

process(clk,rst)

variable cnt:integer;--其实一个就够了

variable cqi:std_logic_vector(3 downto 0);

begin

if rst='1' then--rst为1是复位,led给1,cnt和cqi给0

cnt:=0;

led<='1';

cqi:=(others=>'0');

else

if cnt<9 then--在rst为0的条件下,看cnt或cqi是不是小于9,小于9就自加

cnt:=cnt+1;

cqi:=cqi+1;

else --在rst为0的条件下,看cnt或cqi是不是小于9,小于9就自加

cnt:=0;

cqi:=(others=>'0');

end if;

end if;

if cnt=9 then --单独的if用来启动led,其实就是一个进位标值

led<='1';

else

led<='0';

end if;

cout<=cqi;--显示cqi的值,也就是cnt的值

end process;

end Behavioral;

下面给出仿真代码:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY counter1_tb IS

END counter1_tb;

ARCHITECTURE behavior OF counter1_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT counter1

PORT(

clk : IN std_logic;

rst : IN std_logic;

cout:out std_logic_vector(3 downto 0);

led : OUT std_logic

);

END COMPONENT;

--Inputs

signal clk : std_logic := '0';

signal rst : std_logic := '0';

--Outputs

signal led : std_logic;

signal cout: std_logic_vector(3 downto 0);

-- Clock period definitions

constant clk_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: counter1 PORT MAP (

clk => clk,

rst => rst,

cout=> cout,

led => led

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

rst<='1';

wait for 100 ns;

rst<='0';

-- insert stimulus here

wait;

end process;

END;

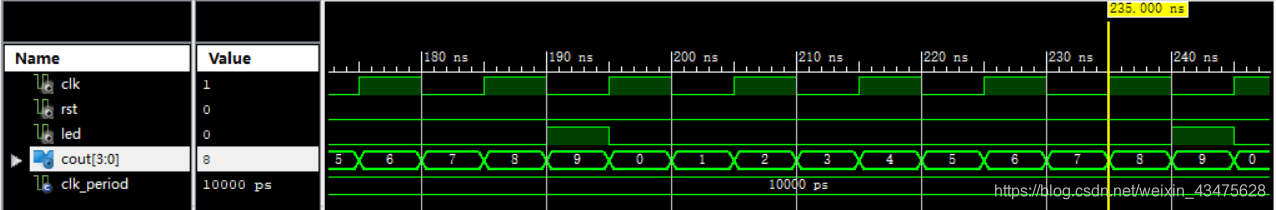

下面给出仿真波形:

前边一段波形rst为1,led没有输出,后边计数10个clk的正负跳变,led为1.

与设计思路一致。