2.3.3 SPI

SPI(Serial Peripheral Interface,串行外设接口)总线系统是一种同步串行外设接口,它可以使CPU与各种外围设备以串行方式进行通信以交换信息。一般主控SoC作为SPI的“主”,而外设作为SPI的“从”。

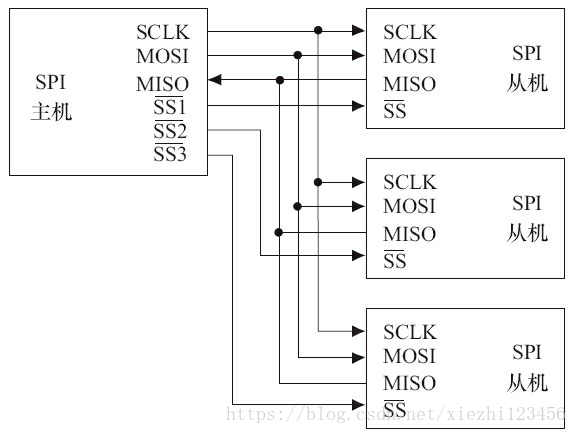

SPI接口一般使用4条线:CS(片选信号)、串行时钟线(SCLK)、主机输入/从机输出数据线MISO和主机输出/从机输入数据线MOSI。图2.12演示了1个主机(主设备)连接3个SPI外设(从设备)的硬件连接图。

图2.12 SPI主、从硬件连接图

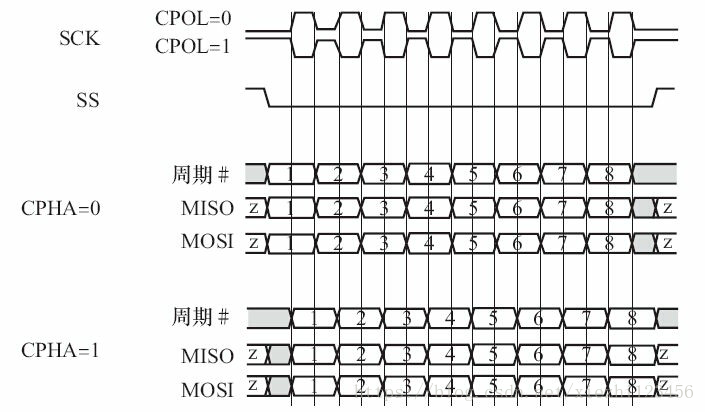

如图2.13所示,SPI总线时序。

图2.13 SPI总线的时序

在SPI总线的传输中,CS信号是低电平有效的,当我们要与某外设通信的时候,需要将该外设上的CS线置低。此外,特别要注意SPI从设备支持的SPI总线最高时钟频率(决定了SCK的频率)以及外设的CPHA(时钟相位)、CPOL(时钟极性)模式。这决定了数据与时钟之间的偏移、采样的时刻以及触发的边沿是上升沿还是下降沿。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性(CPOL)和相位(CPHA)可以进行配置。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

扫描二维码关注公众号,回复:

195216 查看本文章

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。