Linux 驱动设计之硬件基础

0、开篇说明

本片内容主要来源于宋宝华老师《Linux设备驱动开发》

1、处理器

目前主流的通用处理器(GPP)多采用SoC(片上系统)的芯片设计方法,集成各种功能模块. ARM内核的设计技术被授权给数百家半导体厂商,做成不同的SoC芯片。ARM的功耗很低,在当今最活跃的无线局域网、3G、手机终端、手持设备、有线网络通信设备等中应用非常广泛。很多ARM主控芯片的集成度非常高,除了集成多核ARM以外,还可能集成图形处理器、视频编解码器、浮点协处理器、GPS、WiFi、蓝牙、基带、Camera等一系列功能.

主流供应商如下:

- 高通(Qualcomm)

- 三星(Samsung)

- 英伟达(Nvidia)

- 美满(Marvell)

- 联发科(MTK)

- 海思(HiSilicon)

- 展讯(Spreadtrum)

- 德州仪器(TI)

- 博通(Broadcom)

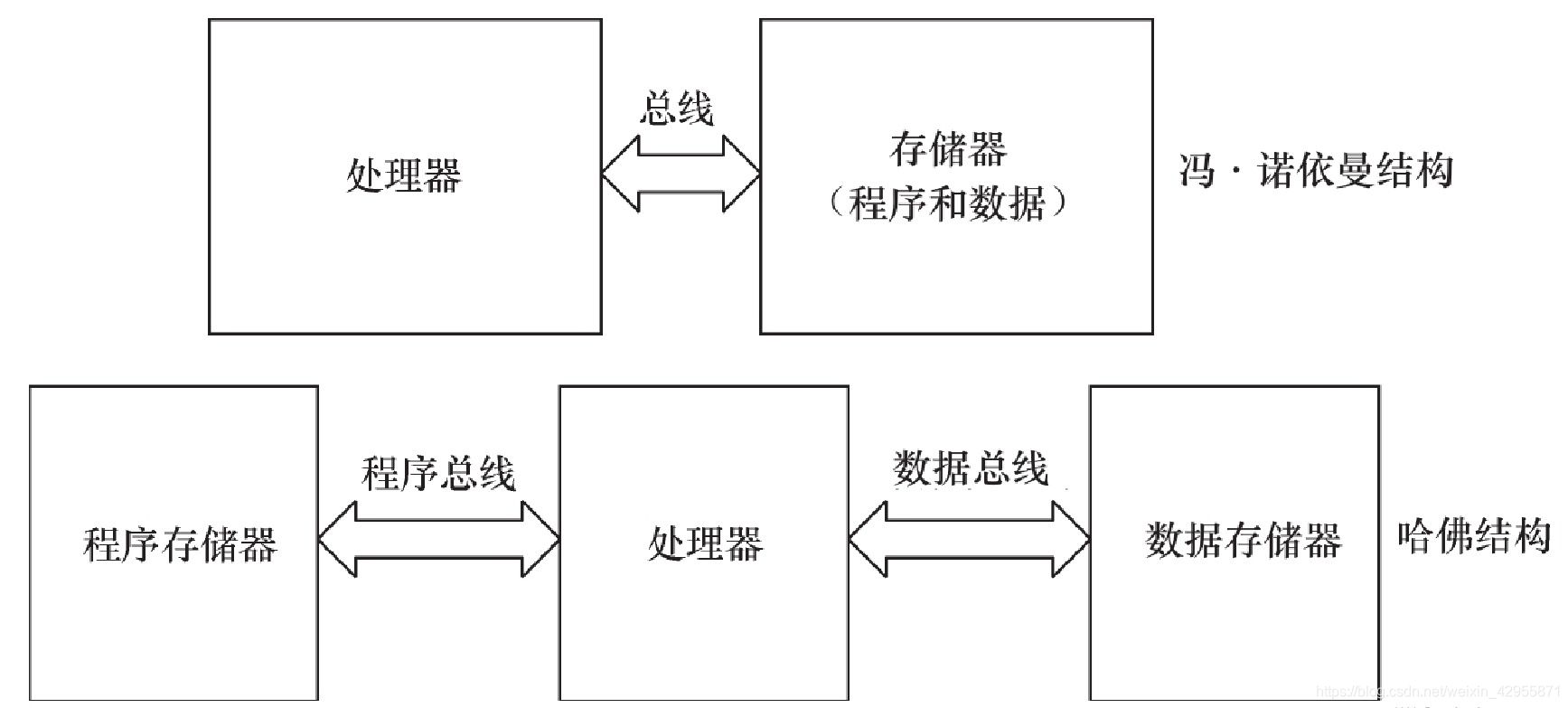

中央处理器的体系结构

- 冯诺依曼 (程序指令存储器和数据存储器在一起)

- 哈佛结构 (程序和数据分开存储)

如下图所示:

指令集

- RISC

- CICS

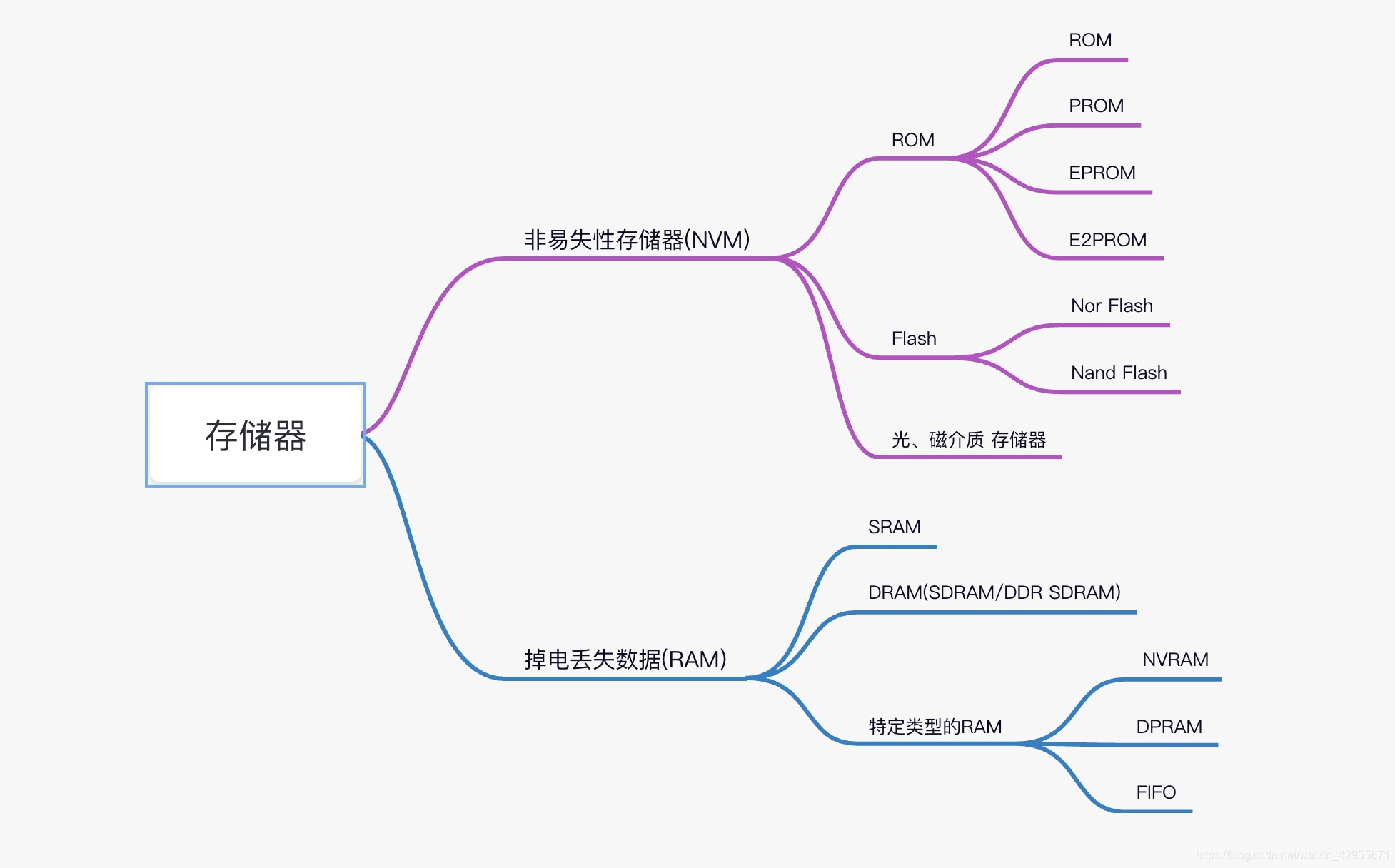

2、存储器

存储器分类如下图所示:

2.1 Flash读取接口

NOR Flash读写接口(SRAM): 公共闪存接口(Common Flash Interface,CFI)是一个从NOR Flash器件中读取数据的公开、标准接口。

NAND Flash接口:

- I/O总线:地址、指令和数据通过这组总线传输,一般为8位或16位。

·芯片启动(Chip Enable,CE#):如果没有检测到CE信号,NAND器件就保持待机模式,不对任何控制信号做出响应。 - 写使能(Write Enable,WE#):WE#负责将数据、地址或指令写入NAND之中。

- 读使能(Read Enable,RE#):RE#允许数据输出。

- 指令锁存使能(Command Latch Enable,CLE):当CLE为高电平时,在WE#信号的上升沿,指令将被锁存到NAND指令寄存器中。

- 地址锁存使能(Address Latch Enable,ALE):当ALE为高电平时,在WE#信号的上升沿,地址将被锁存到NAND地址寄存器中。

- 就绪/忙(Ready/Busy,R/B#):如果NAND器件忙,R/B#信号将变为低电平。该信号是漏极开路,需要采用上拉电阻。

2.2 Flash 优缺点对比

| 型号 | 价格 | 容量 | 擦写次数 | 速度 |

|---|---|---|---|---|

| NOR | 高 | 小 | 10万 | 慢 |

| NAND | 低 | 大 | 100万 | 快 |

2.3 RAM 介绍

-

DRAM:

DRAM以电荷形式进行存储,数据存储在电容器中。由于电容器会因漏电而出现电荷丢失,所以DRAM器件需要定期刷新 -

SRAM:

SRAM是静态的,只要供电它就会保持一个值,SRAM没有刷新周期 -

DPRAM:

具有两套完全独立的数据总线、地址总线和读写控制线,可以端口同时访问扫描二维码关注公众号,回复: 12173223 查看本文章

-

CAM

内容寻址的存储器。用于数据查询 -

FIFO

用于数据缓存

3、接口与总线

3.1 串口

- RS-232

- RS-422

- RS-485

以上均由EIA制定发布.

RS-232C标准接口有25条线,9根常用线:

- RTS:用来表示DTE请求DCE发送数据,当终端要发送数据时,使该信号有效。

- CTS:用来表示DCE准备好接收DTE发来的数据,是对RTS的响应信号。

- RxD:DTE通过RxD接收从DCE发来的串行数据。

- TxD:DTE通过TxD将串行数据

- DSR:有效(ON状态)表明DCE可以使用。

- DTR:有效(ON状态)表明DTE可以使用。

- DCD:当本地DCE设备收到对方DCE设备送来的载波信号时,使DCD有效,通知DTE准备接收,并且由DCE将接收到的载波信号解调为数字信号,经RxD线送给DTE。

- Ringing-RI:当调制解调器收到交换台送来的振铃呼叫信号时,使该信号有效(ON状态),通知终端,已被呼叫。

- SG: 地信号

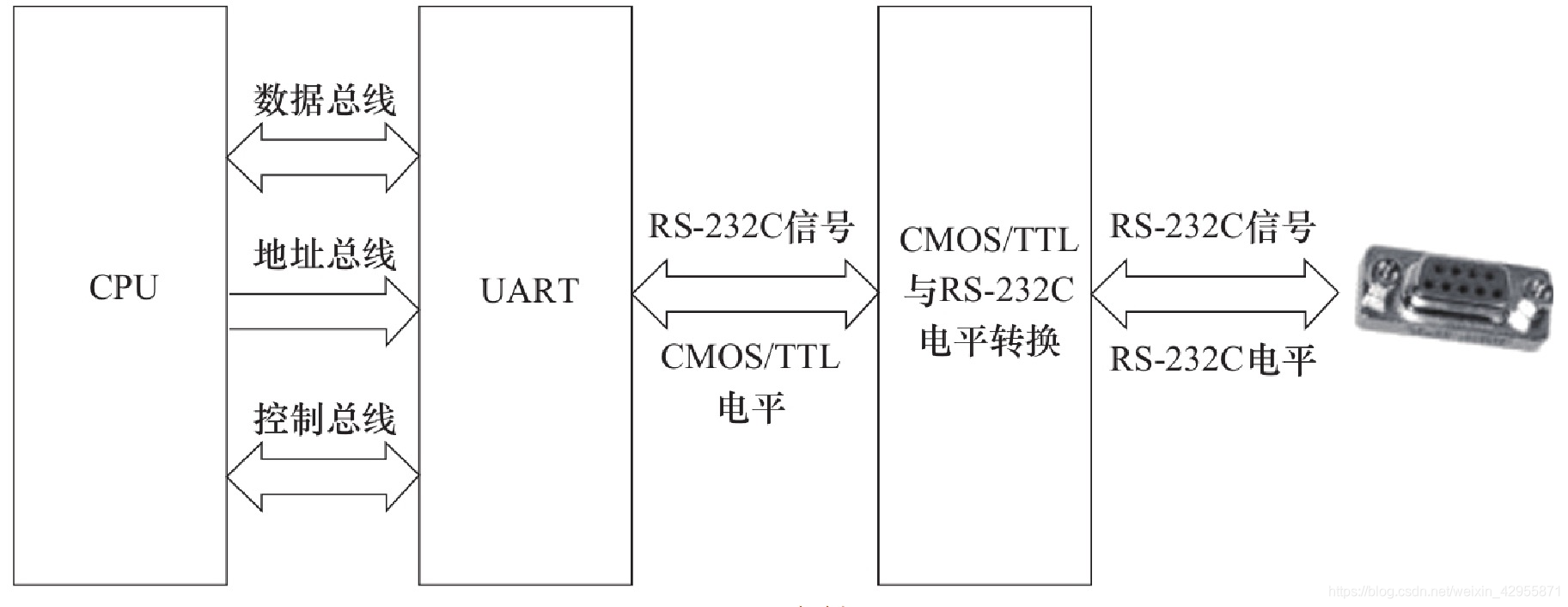

最简单的RS-232C串口只需要连接RxD、TxD、SG这3个信号,并使用XON/XOFF软件流控。连接如下图所示

3.2 I2C

总线有两条:

- SDA:数据总线

- SDL:时钟总线

“线与”逻辑

要求:

1) 设备连接到总线的输出端必须是开漏极输出或是集电极开路输出

2)空闲时,上拉电阻保证两根线 均为高电平

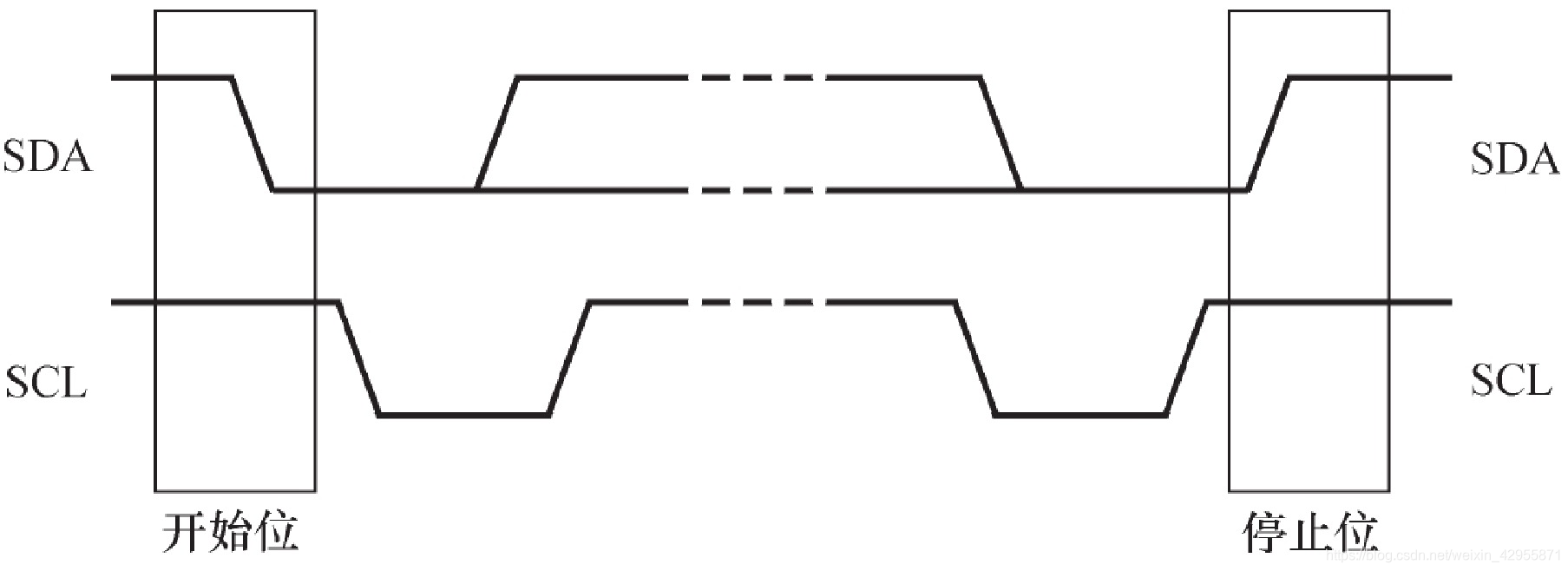

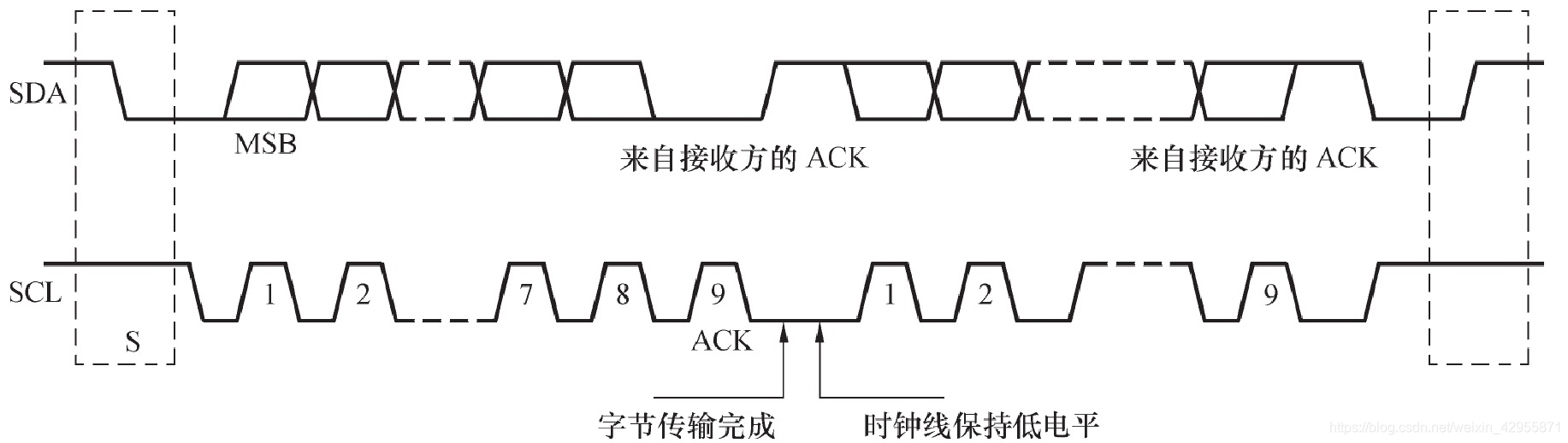

I2C设备上的串行数据线SDA接口电路是双向的,输出电路用于向总线上发送数据,输入电路用于接收总线上的数据。同样地,串行时钟线SCL也是双向的,作为控制总线数据传送的主机要通过SCL输出电路发送时钟信号,并检测总线上SCL上的电平以决定什么时候发下一个时钟脉冲电平;作为接收主机命令的从设备需按总线上SCL的信号发送或接收SDA上的信号,它也可以向SCL线发出低电平信号以延长总线时钟信号周期。当SCL稳定在高电平时,SDA由高到低的变化将产生一个开始位,而由低到高的变化则产生一个停止位,如图2.10所示。开始位和停止位都由I2C主设备产生。在选择从设备时,如果从设备采用7位地址,则主设备在发起传输过程前,需先发送1字节的地址信息,前7位为设备地址,最后1位为读写标志。之后,每次传输的数据也是1字节,从MSB开始传输。每个字节传完后,在SCL的第9个上升沿到来之前,接收方应该发出1个ACK位。SCL上的时钟脉冲由I2C主控方发出,在第8个时钟周期之后,主控方应该释放SDA

开始位和停止位图:

I2C时序图:

3.3 SPI

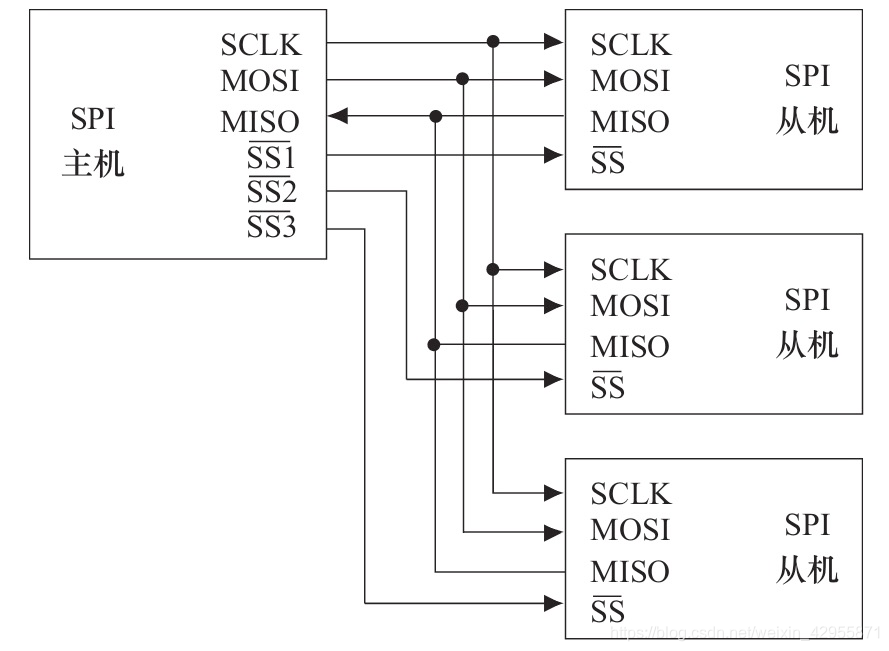

SPI(Serial Peripheral Interface,串行外设接口)总线系统是一种同步串行外设接口,它可以使CPU与各种外围设备以串行方式进行通信以交换信息。一般主控SoC作为SPI的“主”,而外设作为SPI的“从”.

SPI四条线:

- 串行时钟线 SCLK

- 主机输入/从机输出数据线 MISO

- 主机输出/从机输入数据线 MOSI

- 低电平有效从机选择线 SS

主从机硬件连接图:

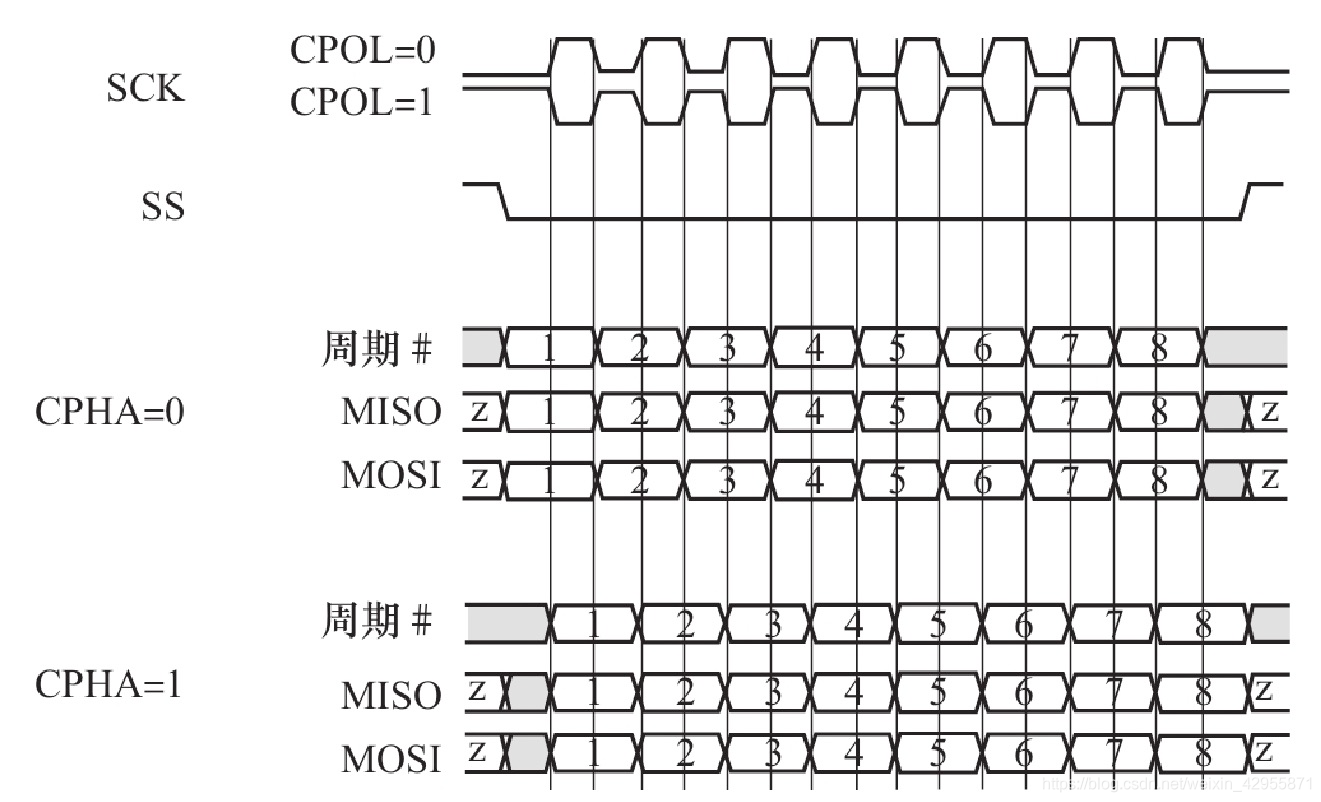

在SPI总线的传输中,SS信号是低电平有效的,当我们要与某外设通信的时候,需要将该外设上的SS线置低。此外,特别要注意SPI从设备支持的SPI总线最高时钟频率(决定了SCK的频率)以及外设的CPHA、CPOL模式,

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性(CPOL)和相位(CPHA)可以进行配置。如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

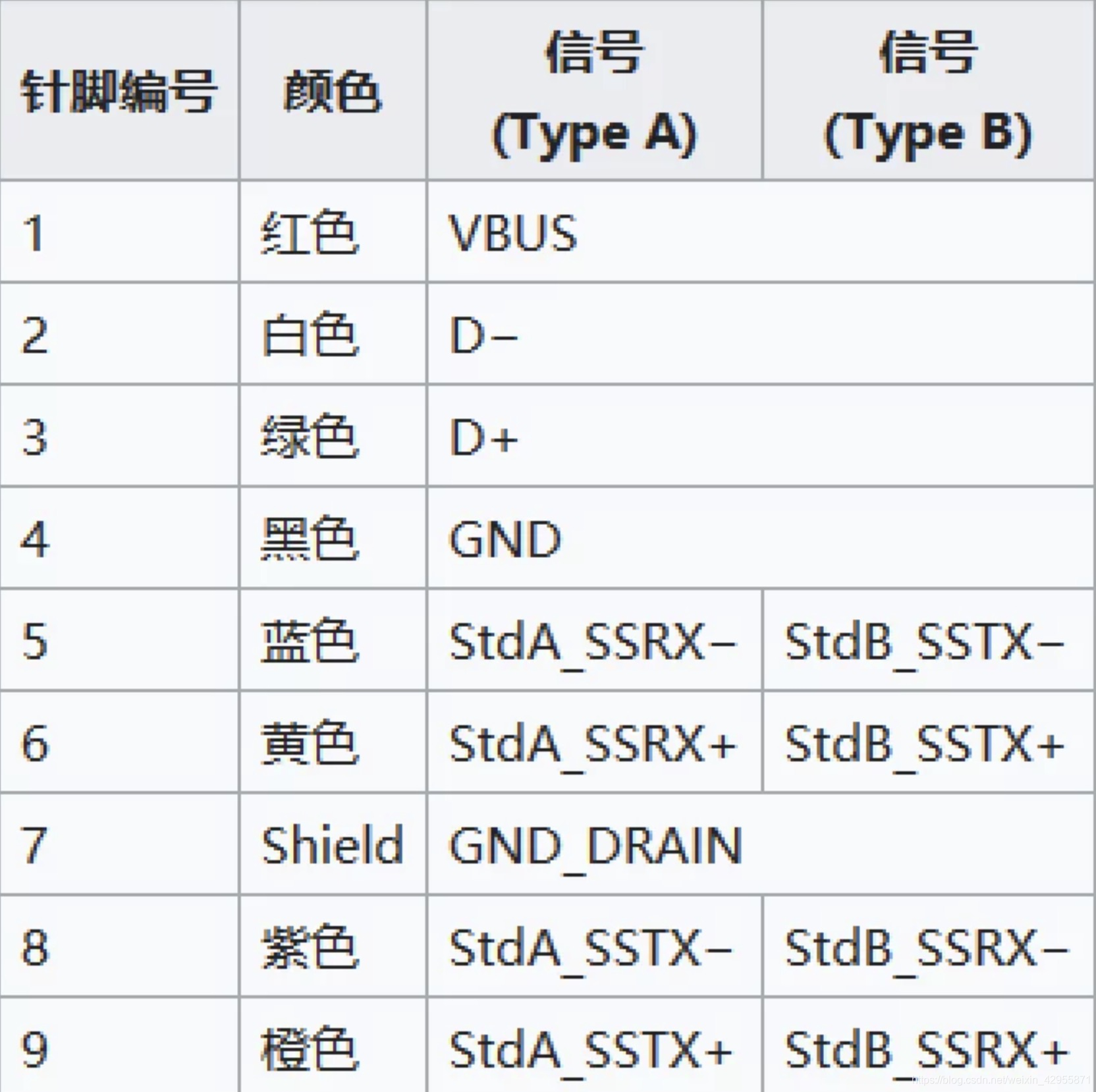

3.4 USB

USB2.0:

- 480Mbit/s,半双工

- 四根线

USB3.0:

- 5.0Gbit/s,全双工

- 九根线

USB3.0兼容USB2.0.

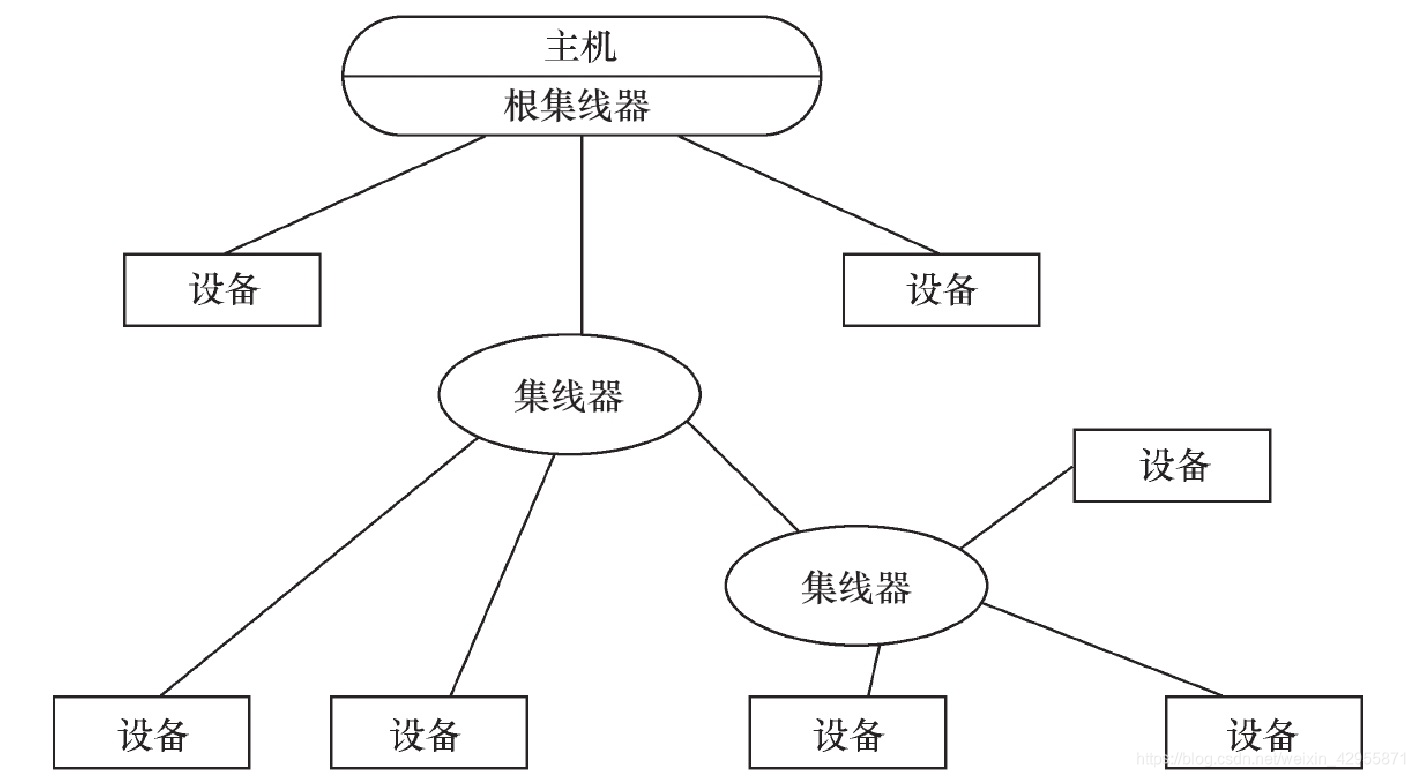

USB主机、设备及HUB的物理拓扑结构:

USB端点的四种传输模式:

- 控制

- 同步

- 中断

- 批量

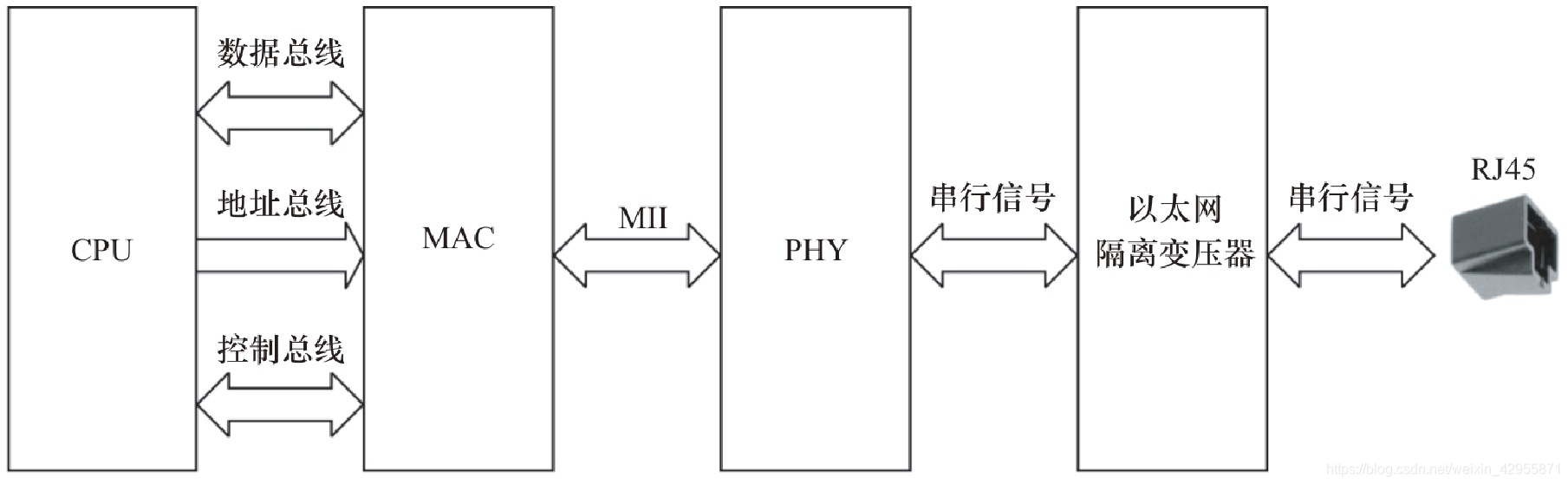

3.5 以太网

组成:

- MAC : 以太网媒体接入控制器

- PHY: 物理接口收发器

硬件电路原理:

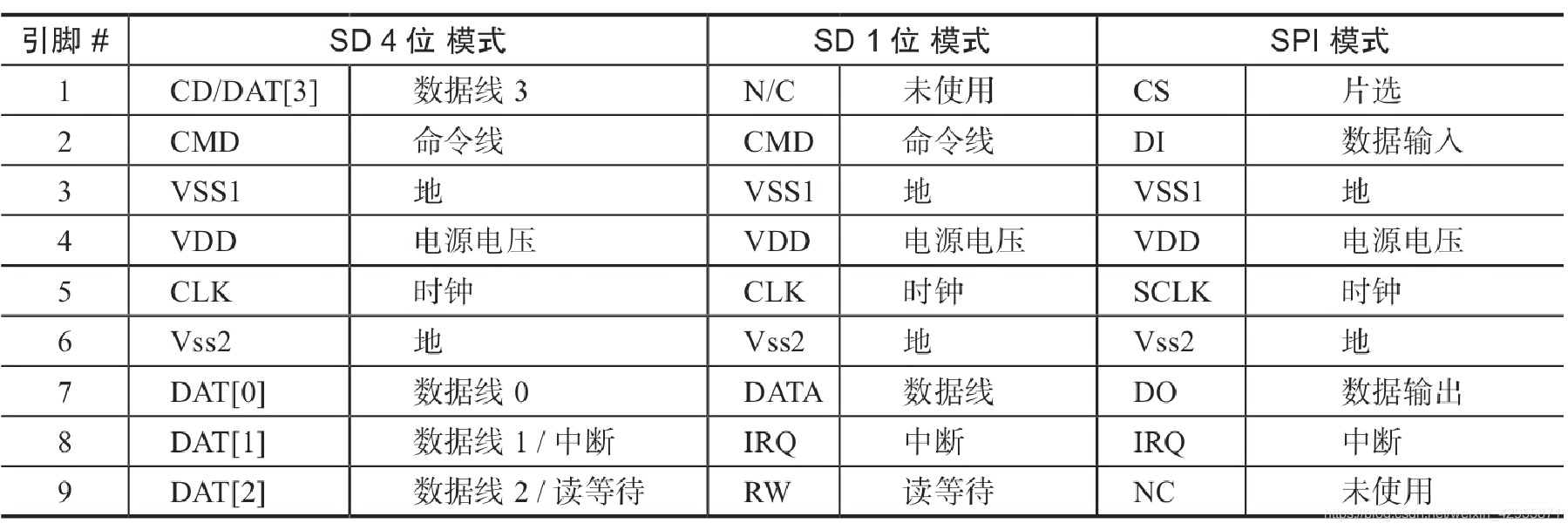

3.6 SD/SDIO

SD(Secure Digital)是一种关于Flash存储卡的标准,也就是一般常见的SD记忆卡,在设计上与MMC(Multi-Media Card)保持了兼容。SDHC(SD High Capacity)是大容量SD卡,支持的最大容量为32GB。2009年发布的SDXC(SD eXtended Capacity)则支持最大2TB大小的容量。SDIO(Secure Digital Input and Output Card,安全数字输入输出卡)在SD标准的基础上,定义了除存储卡以外的外设接口。现在已经有非常多的手机或者手持装置都支持SDIO的功能,以连接WiFi、蓝牙、GPS等模块。

SD/SDIO的传输模式:

- SPI

- 1位模式

- 4位模式

3.7 原理图

略

3.8 硬件时序

略

3.9 Datasheet

- Memory Map

3.10 仪器仪表的使用

- 万用表

- 示波器

- 逻辑分析仪