简介

高速、全双工串行总线,使用四根线完成通信。数据一位一位的传输,高位先行。

有点:连线少

缺点:没有应答机制

连线

一共四根线

SSEL:片选信号。低电平选中,可以用多个GPIO代替这个信号实现多从机通信。

SCLK:时钟信号,由主机产生。

MOSI:主机给从机发送指令或者数据的通道。

MISO:主机读取从机的状态或者数据的通道。

传输协议

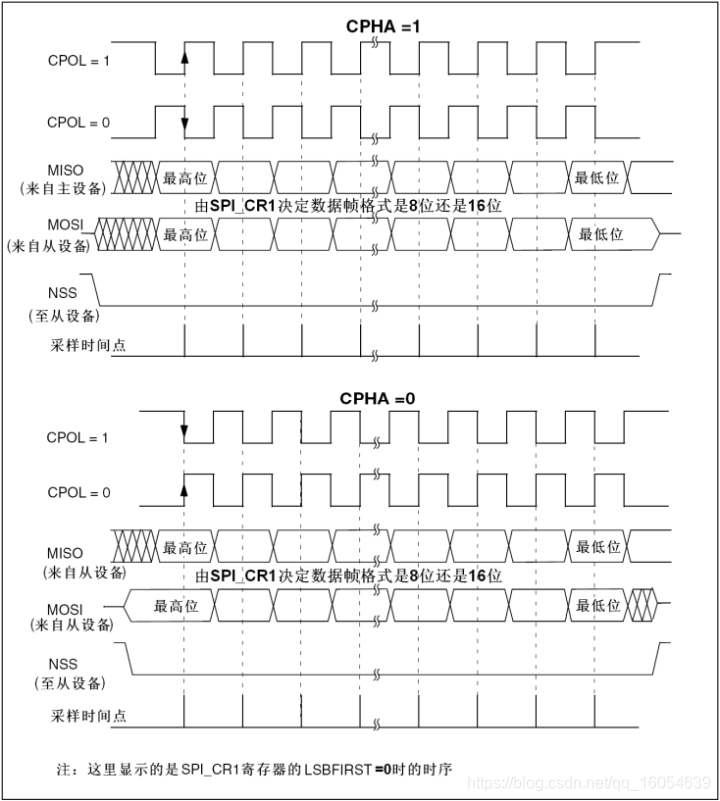

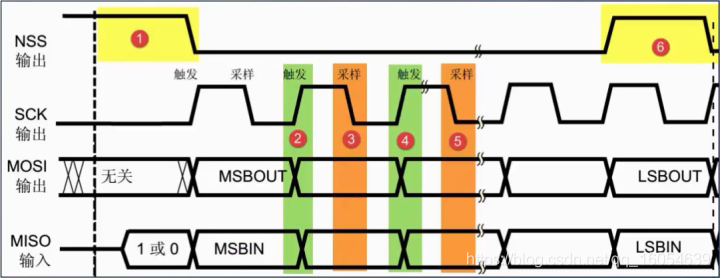

SPI通信的时候再SCLK边沿采样数据,常见的是SCLK上升沿主机发送数据,在SCLK下降沿主机接收数据,这称作SPI的相位(CPHA: Clock Phase)。另外还有总线空闲的时候SCLK处在什么电平,这称作时钟极性(CPOL:Clock Polarity)。由此就产生了四种组合。

- SCLK上升沿主机发送数据,下降沿接收数据,空闲时刻SCLK低电平:CPHA = 1,CPOL = 0

- SCLK上升沿主机发送数据,下降沿接收数据,空闲时刻SCLK高电平:CPHA = 1,CPOL = 1

- SCLK上升沿主机接收数据,下降沿发送数据,空闲时刻SCLK低电平:CPHA = 0,CPOL = 0

- SCLK上升沿主机接收数据,下降沿发送数据,空闲时刻SCLK高电平:CPHA = 0,CPOL = 1

时序图:

四种模式的时序: