I/O口作为外部中断。general purpose input and output

STM32 的每个 IO口都可以作为中断输入,要把 IO口作为外部中断输入,

有以下几个步骤:

1) 初始化 IO 口为输入。

这一步设置你要作为外部中断输入的 IO 口的状态,可以设置为上拉/下拉输入,也可以设

置为浮空输入,但浮空的时候外部一定要带上拉,或者下拉电阻。否则可能导致中断不停的触

发。在干扰较大的地方,就算使用了上拉/下拉,也建议使用外部上拉/下拉电阻,这样可以一

定程度防止外部干扰带来的影响。

2) 开启 IO 口复用时钟,设置 IO 口与中断线的映射关系。

STM32 的 IO 口与中断线的对应关系需要配置外部中断配置寄存器 EXTICR,这样我们要

先开启复用时钟,然后配置 IO 口与中断线的对应关系。才能把外部中断与中断线连接起来。

3) 开启与该 IO 口相对的线上中断/事件,设置触发条件。

这一步,我们要配置中断产生的条件, STM32 可以配置成上升沿触发,下降沿触发,或者

任意电平变化触发,但是不能配置成高电平触发和低电平触发。这里根据自己的实际情况来配

置,同时要开启中断线上的中断。这里需要注意的是:如果使用外部中断,并设置该中断的 EMR

位的话,会引起软件仿真不能跳到中断,而硬件上是可以的。而不设置 EMR,软件仿真就可以

进入中断服务函数,并且硬件上也是可以的。建议不要配置 EMR 位。

4) 配置中断分组(NVIC),并使能中断。

这一步,我们就是配置中断的分组,以及使能,对 STM32 的中断来说,只有配置了 NVIC

的设置,并开启才能被执行,否则是不会执行到中断服务函数里面去的。关于 NVIC 的详细介

绍,请参考 5.2.6 节。

5) 编写中断服务函数。

这是中断设置的最后一步,中断服务函数,是必不可少的,如果在代码里面开启了中断,

但是没编写中断服务函数,就可能引起硬件错误,从而导致程序崩溃!所以在开启了某个中断

后,一定要记得为该中断编写服务函数。在中断服务函数里面编写你要执行的中断后的操作。

与 NVIC 相关的寄存器, MDK 为其定义了如下的结构体:

typedef struct

{

__IO uint32_t ISER[8]; //中断使能寄存器组 Interrupt Set-Enable Registers

uint32_t RESERVED0[24];

__IO uint32_t ICER[8]; //中断除能寄存器组

uint32_t RSERVED1[24];

__IO uint32_t ISPR[8]; //中断挂起控制寄存器组

uint32_t RESERVED2[24];

__IO uint32_t ICPR[8]; //中断解挂控制寄存器组

uint32_t RESERVED3[24];

__IO uint32_t IABR[8]; //中断激活标志位寄存器组

uint32_t RESERVED4[56];

__IO uint8_t IP[240]; //中断优先级控制寄存器组

uint32_t RESERVED5[644];

__O uint32_t STIR; //软件触发中断寄存器组

} NVIC_Type;

ISER[8]: ISER 全称是: Interrupt Set-Enable Registers, 每1 bit 代表一个中断,总共有32×8=256个中断,你要使能某个中断,必须设置相应的 ISER 位为 1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、 IO 口映射等设置才算是一个完整的中断设置)。

ICER[8]:全称是: Interrupt Clear-Enable Registers, 该寄存器组与 ISER[8] 的作用恰好相反,是用来清除某个中断的使能的。 如果想清除一个中断,不是在对应bit写0,而应该在对应位置写1。写0是无效的。

ISPR[8]:全称是: Interrupt Set-Pending Registers ,每个位对应的中断和 ISER 是一样的。通过置 1,可以将正在进行的中断挂起,而执行同级或更高级别的中断。写 0 是无效的。

ICPR[8]:全称是: Interrupt Clear-Pending Registers ,通过设置 1,可以将挂起的中断取消挂起操作。写 0 无效。

IABR[8]:全称是: Interrupt Active Bit Registers,是一个中断激活标志位寄存器组。对应位所代表的中断和 ISER 一样,如果为 1,则表示该位所对应的中断正在被执行。这是一个只读寄存器,通过它可以知道当前在执行的中断是哪一个。在中断执行完了由硬件自动清零。

IP[240]:全称是: Interrupt Priority Registers, 是一个中断优先级控制的寄存器组。这个寄存器组相当重要! STM32 的中断分组与这个寄存器组密切相关。 IP 寄存器组由 240 个 8bit 的寄存器组成,每个可屏蔽中断占用 8bit,这样总共可以表示 240 个可屏蔽中断。 而 STM32 只用到了其中的 68 个。 IP[67]~IP[0]分别对应中断 67~0。 而每个可屏蔽中断占用的 8bit 并没有全部使用,而是 只用了高 4 位。这 4 位,又分为抢占优先级和子优先级。抢占优先级在前,子优先级在后。而这两个优先级各占几个位又要根据 SCB->AIRCR 中的中断分组设置来决定。抢占优先级的级别高于响应优先级。而数值越小所代表的优先级就越高。

STM32 的 5 个分组是通过设置 SCB->AIRCR 的 BIT[10:8]来实现的,而 SCB->AIRCR 的修改需要通过在高 16 位写入 0X05FA 这个密钥才能修改的,故在设置 AIRCR 之前,应该把密钥加入到要写入的内容的高 16 位,以保证能正常的写入 AIRCR。在修改 AIRCR 的时候,我们一般采用读->改->写的步骤,来实现不改变 AIRCR 原来的其他设置。

这里简单介绍一下 STM32 的中断分组: STM32 将中断分为 5 个组,组 0~4。该分组的设

置是由 SCB->AIRCR 寄存器的 bit10~8 来定义的。具体的分配关系如表 5.2.6.1 所示:

| 组 | AIRCR[10: 8] | bit[7: 4]分配情况 | 分配结果 |

| 0 | 111 | 0: 4 | 0 位抢占优先级, 4 位响应优先级 |

| 1 | 110 | 1: 3 | 1 位抢占优先级, 3 位响应优先级 |

| 2 | 101 | 2: 2 | 2 位抢占优先级, 2 位响应优先级 |

| 3 | 100 | 3: 1 | 3 位抢占优先级, 1 位响应优先级 |

| 4 | 011 | 4: 0 | 4 位抢占优先级, 0 位响应优先级 |

表 5.2.6.1 AIRCR 中断分组设置表

//设置 NVIC

//NVIC_PreemptionPriority: 抢占优先级

//NVIC_SubPriority : 响应优先级

//NVIC_Channel : 中断编号

//NVIC_Group : 中断分组 0~4

//注意优先级不能超过设定的组的范围!否则会有意想不到的错误

//组划分:

//组 0: 0 位抢占优先级, 4 位响应优先级

//组 1: 1 位抢占优先级, 3 位响应优先级

//组 2: 2 位抢占优先级, 2 位响应优先级

//组 3: 3 位抢占优先级, 1 位响应优先级

//组 4: 4 位抢占优先级, 0 位响应优先级

//NVIC_SubPriority 和 NVIC_PreemptionPriority 的原则是, 数值越小, 越优先

void MY_NVIC_Init(u8 NVIC_PreemptionPriority,u8 NVIC_SubPriority,u8 NVIC_Channel,u8 NVIC_Group)

{

u32 temp;

MY_NVIC_PriorityGroupConfig(NVIC_Group);//设置分组

temp=NVIC_PreemptionPriority<<(4-NVIC_Group);

temp|=NVIC_SubPriority&(0x0f>>NVIC_Group);

temp&=0xf; //取低四位

NVIC->ISER[NVIC_Channel/32]|=(1<<NVIC_Channel%32);

//使能中断位(要清除的话,相反操作就 OK)

NVIC->IP[NVIC_Channel]|=temp<<4; //设置响应优先级和抢断优先级

}

NVIC配置总结:

1) SCB->AIRCR 决定抢占优先级的位数,设置怎么解释IP(interrupt priority)分组。其实这个分组的设置在每个系统里面只要设置一次就够了,设置多次,则是以最后的那一次为准。整个系统的优先级分组格式都一样。

2) ISER 使能对应的中断管脚,

3)设置优先级。

IP[channel] 决定具体的抢占优先级和子优先级。

IP和SCB->AIRCR 一起决定中断的优先级。

IABR 自读,显示当前正在执行的中断时那个管脚的中断。

》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》

以上是对NVIC的管理和配置,下面说明一下外不中断的配置。

》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》》

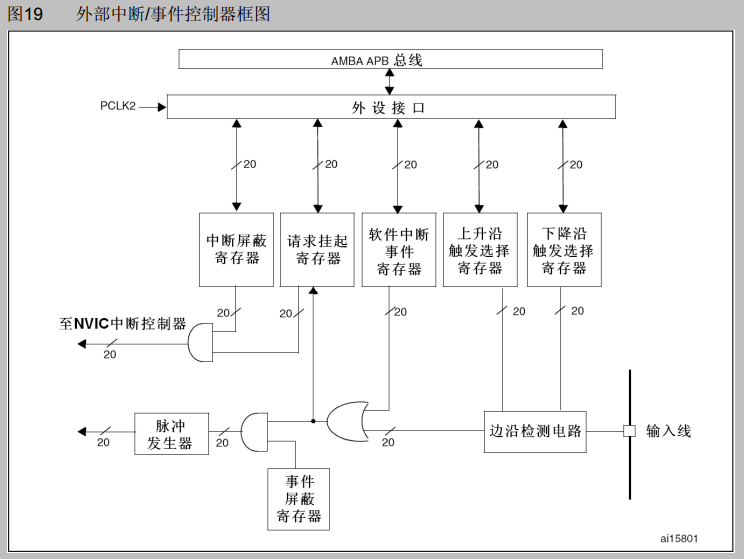

STM32F103 的 EXTI 控制器支持 19 个外部中断/事件请求。每个中断设有状态位,每个中断/事件都有独立的触发和屏蔽设置。 STM32F103 的 19 个外部中断为:

线 0~15:对应外部 IO 口的输入中断。

线 16:连接到 PVD 输出。

线 17:连接到 RTC 闹钟事件。

线 18:连接到 USB 唤醒事件。

对于外部中断 EXTI 控制 MDK 定义了如下结构体:

typedef struct

{

__IO uint32_t IMR; //interrupt mask register

__IO uint32_t EMR; //event mask register

__IO uint32_t RTSR; //rising trigger selection register

__IO uint32_t FTSR; //falling trigger selection register

__IO uint32_t SWIER; //software interrupt event register

__IO uint32_t PR; //pending register

} EXTI_TypeDef;

IMR:中断屏蔽寄存器。这是一个 32 寄存器。但是只有前 19 位有效(19个外部中断)。当位 x 设置为 1 时,则开启这个线上的中断,否则关闭该线上的中断。

EMR:事件屏蔽寄存器,同 IMR,只是该寄存器是针对事件的屏蔽和开启。

RTSR:上升沿触发选择寄存器。该寄存器同 IMR,也是一个 32 为的寄存器,只有前 19位有效。位 x 对应线 x 上的上升沿触发,如果设置为 1,则是允许上升沿触发中断/事件。否则,不允许。

FTSR:下降沿触发选择寄存器。同 RTSR,不过这个寄存器是设置下降沿的。下降沿和上升沿可以被同时设置,这样就变成了任意电平触发了。

SWIER:软件中断事件寄存器。通过向该寄存器的位 x 写入 1,在未设置 IMR 和 EMR 的时候,将设置 PR 中相应位挂起。如果设置了 IMR 和 EMR 时将产生一次中断。被设置的 SWIER位,将会在 PR 中的对应位清除后清除。

PR:挂起寄存器。当外部中断线上发生了选择的边沿事件,该寄存器的对应位会被置为 1。0:表示对应线上没有发生触发请求。通过向该寄存器的对应位写入 1 可以清除该位。在中断服务函数里面经常会要向该寄存器的对应位写 1 来清除中断请求 。

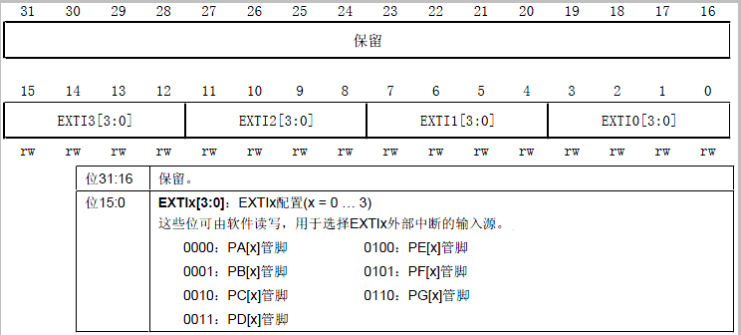

通过以上配置就可以正常设置外部中断了,但是外部 IO 口的中断,还需要一个寄存器配置,也就是 IO 复用里的外部中断配置寄存器 EXTICR。这是因为 STM32 任何一个 IO 口都可以配置成中断输入口,但是 IO 口的数目远大于中断线数(16 个)。于是 STM32 就这样设计,GPIOA~GPIOG 的[15:0]分别对应中断线 15~0。

这样每个中断线对应了最多 7 个 IO 口,以中断线 0为例:它对应了 GPIOA.0、 GPIOB.0、 GPIOC.0、 GPIOD.0、 GPIOE.0、 GPIOF.0、 GPIOG.0。而中断线每次只能连接到 1个 IO口上,这样就需要 EXTICR来决定对应的中断线配置到哪个 GPIO上了。

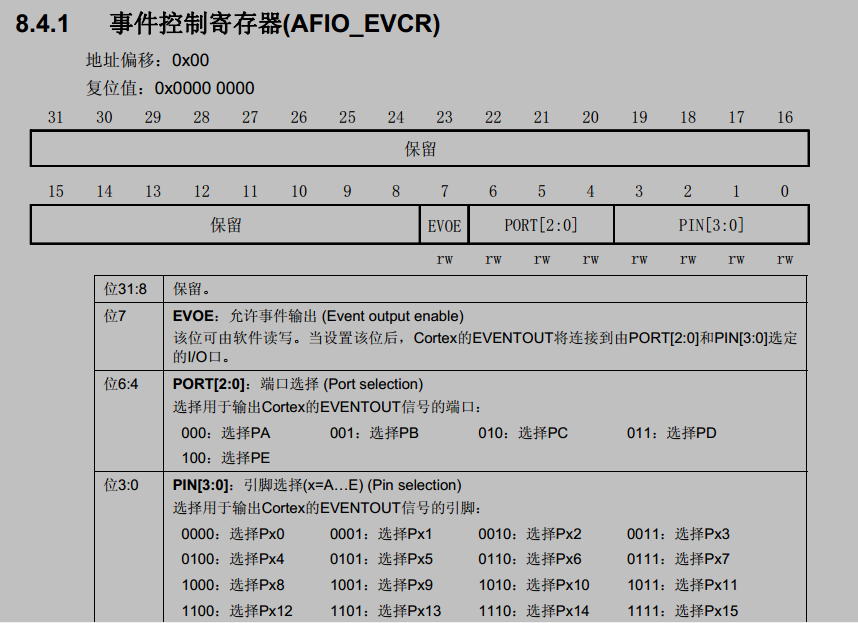

EXTICR 在 AFIO 的结构体中定义,如下:

typedef struct

{

__IO uint32_t EVCR;

__IO uint32_t MAPR;

__IO uint32_t EXTICR[4];

} AFIO_TypeDef;

-------

EXTICR1

EXTICR2 对应EXTI4,EXTI5,EXTI6,EXTI7。

EXTICR3 对应EXTI8,EXTI9,EXTI10,EXTI11。

EXTICR4 对应EXTI12,EXTI13,EXTI14,EXTI15。

映射GPIOX_K 管脚。

例如,EXTI11,配置外部中断管脚11,通过对EXTIX[3:0]的设置分别设置为GPIOA ~ GPIOG 。

//外部中断配置函数//只针对 GPIOA~G;不包括 PVD, RTC 和 USB 唤醒这三个

//参数: GPIOx: 0~6, 代表 GPIOA~G;

//BITx: 需要使能的位;

//TRIM: 触发模式, 1, 下升沿; 2, 上降沿;3,任意电平触发

//该函数一次只能配置 1 个 IO 口, 多个 IO 口, 需多次调用

//该函数会自动开启对应中断, 以及屏蔽线

void Ex_NVIC_Config(u8 GPIOx, u8 BITx, u8 TRIM)

{

u8 EXTADDR;

u8 EXTOFFSET;

EXTADDR=BITx/4; //得到中断寄存器组的编号

EXTOFFSET=(BITx%4)*4;//得到中断寄存器组内的偏移

RCC->APB2ENR|=0x01; //enable AFIO clock

AFIO->EXTICR[EXTADDR]&=~(0x000F<<EXTOFFSET);//清除原来设置!!!

AFIO->EXTICR[EXTADDR]|=GPIOx<<EXTOFFSET; //EXTI.BITx 映射到 GPIOx.BITx

//自动设置

EXTI->IMR|=1<<BITx; //开启 line BITx 上的中断,写1 开启中断

if(TRIM&0x01)EXTI->FTSR|=1<<BITx; //line BITx 上事件下降沿触发

if(TRIM&0x02)EXTI->RTSR|=1<<BITx; //line BITx 上事件上升降沿触发

}

Ex_NVIC_Config 完全是按照我们之前的分析来编写的,首先根据 GPIOx 的位得到中断寄存器组的编号,即 EXTICR 的编号,在 EXTICR 里面配置中断线应该配置到 GPIOx 的哪个位。然后使能该位的中断及事件,最后配置触发方式。这样就完成了外部中断的配置了。

NVIC配置总结:

1) SCB->AIRCR 决定抢占优先级的位数,设置怎么解释IP(interrupt priority)分组。其实这个分组的设置在每个系统里面只要设置一次就够了,设置多次,则是以最后的那一次为准。整个系统的优先级分组格式都一样。

2) ISER 使能对应的中断bit,

3)设置优先级。

IP[channel] 决定具体的抢占优先级和子优先级。

IP和SCB->AIRCR 一起决定中断的优先级。

IABR 自读,显示当前正在执行的中断时那个管脚的中断。

外部中断配置总结:

1) EXTI.BITx 映射到 GPIOx.BITx,通过AFIO_EXTICRn。

2)开启外部中断线。

3)设置触发方式。