共100道经典笔试、面试题目(文末可全领)

基尔霍夫定理的内容

基尔霍夫定律包括电流定律和电压定律:电流定律:在集总电路中,在任一瞬时,流向某一结点的电流之和恒等于由该结点流出的电流之和。电压定律:在集总电路中,在任一瞬间,沿电路中的任一回路绕行一周,在该回路上电动势之和恒等于各电阻上的电压降之和。

描述反馈电路的概念,列举他们的应用。

反馈,就是在电路系统中,把输出回路中的电量(电压或电流)输入到输入回路中去。

反馈的类型有:电压串联负反馈、电流串联负反馈、电压并联负反馈、电流并联负反馈。

负反馈的优点:降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用。电压负反馈的特点:电路的输出电压趋向于维持恒定。

电流负反馈的特点:电路的输出电流趋向于维持恒定。58. 有源滤波器和无源滤波器的区别无源滤波器:这种电路主要有无源元件 R、L 和 C 组成有源滤波器:集成运放和 R、C 组成,具有不用电感、体积小、重量轻等优点。集成运放的开环电压增益和输入阻抗均很高,输出电阻小,构成有源滤波电路后还具有一定的电压放大和缓冲作用。

但集成运放带宽有限,所以目前的有源滤波电路的工作频率难以做得很高。

给了 reg 的 setup,hold 时间,求中间组合逻辑的 delay 范围。

TdTdelay < Tperiod - TsTsetup – TholdTperiod > TsTsetup + Thold +TdTdelay (用来计算最高时钟频率)TcTco= TsTsetup + Thold 即触发器的传输延时

时钟周期为 T,触发器 D1 的寄存器到输出时间(触发器延时 Tco)最大为T1max,最小为 T1min。组合逻辑电路最大延迟为 T2max,最小为 T2min。问,触发器 D2 的建立时间 T3 和保持时间应满足什么条件。

T3setup>T+T2max 时钟沿到来之前数据稳定的时间(越大越好),一个时钟周期T 加上最大的逻辑延时。

T3hold>T1min+T2min 时钟沿到来之后数据保持的最短时间,一定要大于最小的延时也就是 T1min+T2min。

锁存器(latch)和触发器(flip-flop)区别?

电平敏感的存储器件称为锁存器。可分为高电平锁存器和低电平锁存器,用于不同时钟之间的信号同步。有交叉耦合的门构成的双稳态的存储原件称为触发器。分为上升沿触发和下降沿触发。可以认为是两个不同电平敏感的锁存器串连而成。前一个锁存器决定了触发器的建立时间,后一个锁存器则决定了保持时间。

实现三分频电路,3/2 分频电路等(偶数倍分频奇数倍分频)

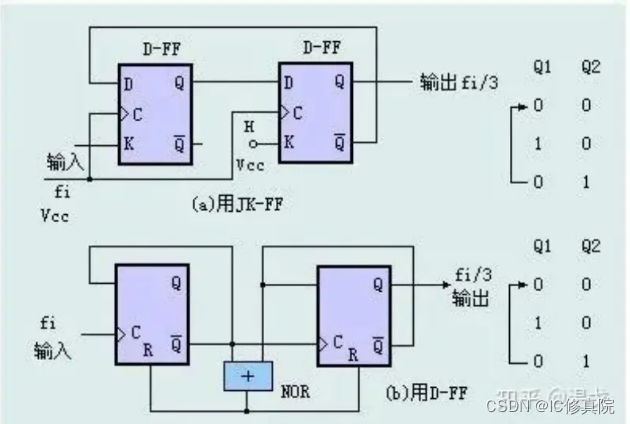

图 a 是 3 分频电路,用 JK-FF 实现 3 分频很方便,不需要附加任何逻辑电路就能实现同步计数分频。

但用 D-FF 实现 3 分频时,必须附加译码反馈电路,如图 2所示的译码复位电路,强制计数状态返回到初始全零状态,就是用 NOR 门电路把 Q2,Q1=“11B”的状态译码产生“H”电平复位脉冲,强迫 FF1 和 FF2 同时瞬间(在下一时钟输入 Fi 的脉冲到来之前)复零,于是 Q2,Q1=“11B”状态仅瞬间作为“毛刺”存在而不影响分频的周期,这种“毛刺”仅在 Q1 中存在,实用中可能会造成错误,应当附加时钟同步电路或阻容低通滤波电路来滤除,或者仅使用 Q2 作为输出。D-FF 的 3 分频,还可以用 AND 门对 Q2,Q1 译码来实现返回复零。

名词解释

CMOS(Complementary Metal Oxide Semiconductor),互补金属氧化物半导体,电压控制的一种放大器件。是组成 CMOS 数字集成电路的基本单元。

MCU(Micro Controller Unit)中文名称为微控制单元,又称单片微型计算机(SingleChip Microcomputer)或者单片机,是指随着大规模集成电路的出现及其发展,将计算机的 CPU、RAM、ROM、定时数计器和多种 I/O 接口集成在一片芯片上,形成芯片级的计算机,为不同的应用场合做不同组合控制。

RISC(reduced instruction set computer,精简指令集计算机)是一种执行较少类型计算机指令的微处理器,起源于 80 年代的 MIPS 主机(即 RISC 机),RISC 机中采用的微处理器统称 RISC 处理器。这样一来,它能够以更快的速度执行操作(每秒执行更多百万条指令,即 MIPS)。因为计算机执行每个指令类型都需要额外的晶体管和电路元件,计算机指令集越大就会使微处理器更复杂,执行操作也会更慢。

CISC 是复杂指令系统计算机(Complex Instruction Set Computer)的简称,微处理器是台式计算机系统的基本处理部件,每个微处理器的核心是运行指令的电路。指令由完成任务的多个步骤所组成,把数值传送进寄存器或进行相加运算。

DSP(digital signal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。其工作原理是接收模拟信号,转换为 0 或 1 的数字信号。再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千 万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

FPGA(Field-Programmable GateArray),即现场可编程门阵列,它是在 PAPAL、GAL、CPLD 等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。与门阵列等其它 ASIC(ApplicationSpecific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。

PCI(Peripheral Component Interconnect)外围组件互连,一种由英特尔(Intel)公司 1991 年推出的用于定义局部总线的标准。

ECC 是“Error Correcting Code”的简写,中文名称是“错误检查和纠正”。ECC是一种能够实现“错误检查和纠正”的技术,ECC 内存就是应用了这种技术的内存,一般多应用在服务器及图形工作站上,这将使整个电脑系统在工作时更趋于安全稳定。

DDR=Double Data Rate 双倍速率同步动态随机存储器。严格的说 DDR 应该叫 DDRSDRAM,人们习惯称为 DDR,其中,SDRAM 是 Synchronous Dynamic RandomAccess Memory 的缩写,即同步动态随机存取存储器。

IRQ 全称为 Interrupt Request,即是“中断请求”的意思(以下使用 IRQ 称呼)。IRQ 的作用就是在我们所用的电脑中,执行硬件中断请求的动作,用来停止其相关硬件的工作状态USB 是英文 Universal Serial BUS(通用串行总线)的缩写,而其中文简称为“通串线,是一个外部总线标准,用于规范电脑与外部设备的连接和通讯。

BIOS 是英文"Basic Input Output System"的缩略语,直译过来后中文名称就是"基本输入输出系统"。其实,它是一组固化到计算机内主板上一个 ROM 芯片上的程序,它保存着计算机最重要的基本输入输出的程序、系统设置信息、开机后自检程序和系统自启动程序。其主要功能是为计算机提供最底层的、最直接的硬件设置和控制。

需要上述面试题目的同学可按需领,点击下方链接可以直接分享给大家~

这里放个口:IC笔面试题目