共100道经典笔试、面试题目(文末可全领)

1. IC 设计中同步复位与异步复位的区别?

同步复位在时钟沿变化时,完成复位动作。异步复位不管时钟,只要复位信号满足条件,就完成复位动作。异步复位对复位信号要求比较高,不能有毛刺,如果其与时钟关系不确定,也可能出现亚稳态。

2.MOORE 与 MEELEY 状态机的特征?

Moore 状态机的输出仅与当前状态值有关, 且只在时钟边沿到来时才会有状态变化。Mealy 状态机的输出不仅与当前状态值有关, 而且与当前输入值有关。

3. 多时域设计中,如何处理信号跨时域?

不同的时钟域之间信号通信时需要进行同步处理,这样可以防止新时钟域中第一级触发器的亚稳态信号对下级逻辑造成影响。

信号跨时钟域同步:当单个信号跨时钟域时,可以采用两级触发器来同步;数据或地址总线跨时钟域时可以采用异步 FIFO 来实现时钟同步;第三种方法就是采用握手信号。

4. 说说静态、动态时序模拟的优缺点?

静态时序分析是采用穷尽分析方法来提取出整个电路存在的所有时序路径, 计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误。

它不需要输入向量就能穷尽所有的路径,且运行速度很快、占用内存较少,不仅可以对芯片设计进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计,因此 静态时序分析已经越来越多地被用到数字集成电路设计的验证中。

动态时序模拟就是通常的仿真,因为不可能产生完备的测试向量,覆盖门级网表中的每一条路径。因此在动态时序分析中,无法暴露一些路径上可能存在的时序问题。

5.一个四级的 Mux,其中第二级信号为关键信号如何改善 timing.?

关键:将第二级信号放到最后输出一级输出,同时注意修改片选信号,保证其优先级未被修改。(为什么?)

6. 给出一个门级的图,又给了各个门的传输延时,问关键路径是什么,还问给出输入, 使得输出依赖于关键路径?

关键路径就是输入到输出延时最大的路径,找到了关键路径便能求得最大时钟频率。

7. 为什么一个标准的倒相器中 P 管的宽长比要比 N 管的宽长比大?

和载流子有关,P 管是空穴导电,N 管是电子导电,电子的迁移率大于空穴,同样的电场下,N 管的电流大于 P 管,因此要增大 P 管的宽长比,使之对称,这样才能使得两者上升时间下降时间相等、高低电平的噪声容限一样、充电放电的时间相等。

8. 用 mos 管搭出一个二输入与非门?

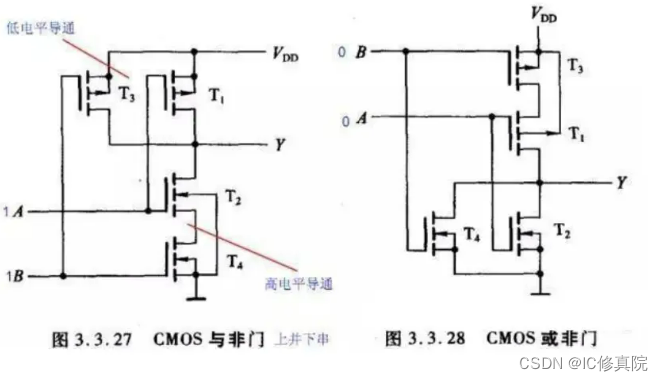

《数字电子技术基础(第五版)》 92 页

与非门:上并下串

或非门:上串下并

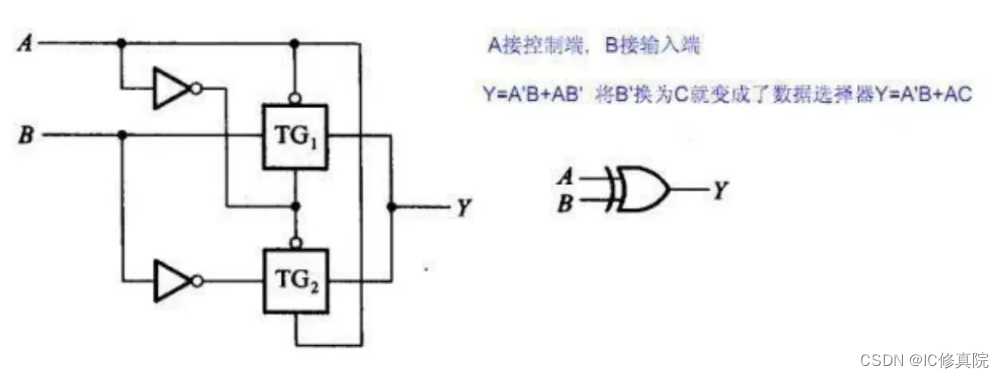

9. 画出 CMOS 的图,画出 tow-to-one muxgate.?

Y=SA+S’B 利用与非门和反相器,进行变换后 Y=((SA)’*(S’A)’)’,三个与非门,一个反相器。也可以用传输门来实现数据选择器或者是异或门。

10.用一个二选一 mux 和一个 inv 实现异或?

其中:B 连接的是地址输入端,A 和 A 非连接的是数据选择端,F 对应的的是输出端, 使能端固定接地置零(没有画出来).

Y=BA’+B’A

利用 4 选 1 实现 F(x,y,y,z)=xz+yz’ F(x,y,y,z)=xyz+xy’z+xyz’+x’yz’=x’y’0+x’yz’+xy’z+xy1

Y=A’B’D0+A’BD1+AB’D2+ABD3

所以 D0=0,D1=z’,D2=z,D3=1

需要上述面试题目的同学可按需领,点击下方链接可以直接分享给大家~

这里放个口:IC笔面试题目