文章目录

一、基础知识篇

1.1 基础总结

1.2 Verilog 硬件描述语言

1.3 SystemVerilog

1.4 Linux

1.5 Markdown

二、Verilog设计实例篇

1.1 小模块设计

1、verilog实例—并行数据流转化为一种特殊串行数据流模块的设计

2、verilog实例—sync_fifo

3、verilog实例—async_fifo

4、verilog实例-Uart设计

5、verilog实例-SPI设计

6、verilog实例-I2C设计

7、Verilog实例-AMBA(AXI)

8、verilog实例-AMBA(APB)协议

9、Verilog实例-AMBA(AHB)协议

10、verilog实例-SRAM控制器

11、verilog实例-fullshakehand握手同步

12、verilog实例-流水线(Pipeline)

13、verilog实例-近期最少使用算法(LRU)

三、脚本语言

3.1 Makefile

3.2 TCL

1.1 TCL教程

2.1 TCL 基础语法

2.2 TCL 命令与置换

2.3 TCL 数值与变量

2.4 TCL 数据类型

2.5 TCL 表达式

3.1 TCL if 语句

3.2 TCL switch 语句

3.3 TCL 循环语句

3.4 TCL break 与 continue

3.3 Perl

3.4 Python

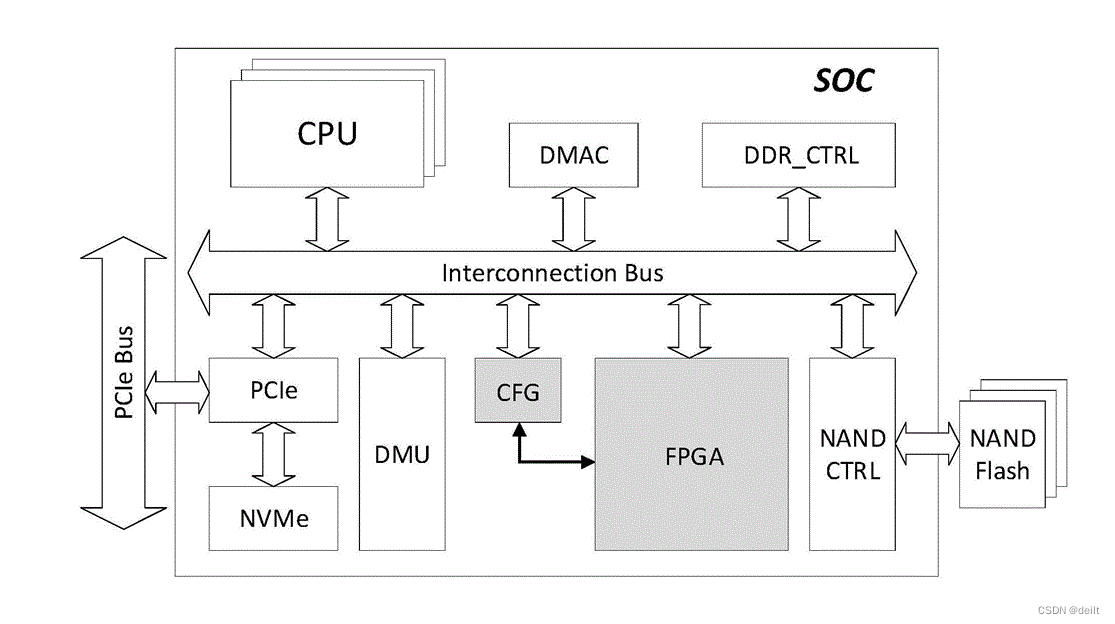

一、芯片架构篇

1.1 RISC-V

一、工具篇

1.1 VCS+Verdi

- VCS + Verdi 流程

- Verdi 启动方式

- Verdi 原理图窗口 nSchema

- Verdi 代码追踪窗口 nTrace

- Verdi 波形窗口 nWave

- VCS 编译选项

- VCS 仿真接口 UCLI

- VCS 混合分步编译