学习摘自数字芯片实验室

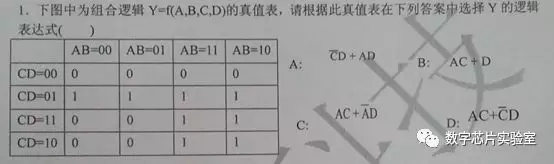

排除法即可

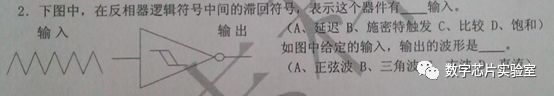

B、施密特触发

C、方波

增强抗干扰能力,避免误触发。

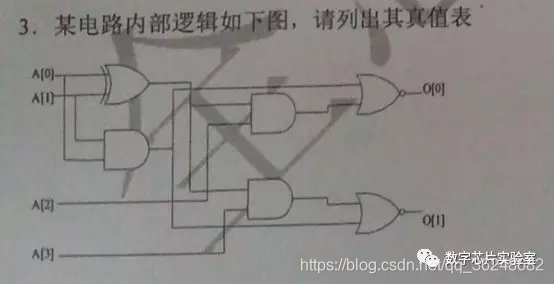

列出所有情况A[3:0] = 4’b0000 ~ 4’b1111即可

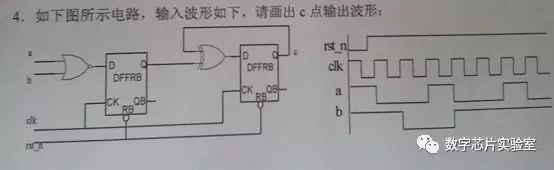

rst_n为异步复位,然后在每个clk上升沿进行触发器状态更新

建立时间:

Clk_delay_ff2 + T > Clk_delay_ff1 + Tco + Tcomb + Tsetup

0.8ns + 4ns > 1ns + 1.2ns + 2.2ns +0.6ns

4.8ns > 5ns,所以建立时间不满足

保持时间:

Clk_delay_ff1 + Tco+ Tcomb > Clk_delay_ff2+ Thold

1ns + 1.2ns + 2.2ns > 0.8ns + 0.3ns

4.4ns > 1.1ns,所以保持时间满足

所谓分频器就是计数器的输出状态,奇数分频器需要同时用到上升沿和下降沿。

根据输入寄存器控制分频计数值

divider.v

module divider(

input clk ,

input rst_n ,

input [2:0] divider_num ,

output reg out_clk

);

reg [2:0] divider_num_reg ;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

divider_num_reg <= 0 ;

end

else begin

divider_num_reg <= divider_num ;

end

end

reg [2:0] count ;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

count <= 0 ;

out_clk <= 0 ;

end

else begin

count <= count +1 ;

if(count == (divider_num_reg-1))begin

out_clk <= ~out_clk ;

count <= 0 ;

end

end

end

always@(negedge clk or negedge rst_n) begin

if(!rst_n) begin

count <= 0 ;

out_clk <= 0 ;

end

else begin

count <= count +1 ;

if(count == (divider_num_reg-1))begin

out_clk <= ~out_clk ;

count <= 0 ;

end

end

end

endmodule

divider_tb.v

module divider_tb;

reg clk ;

reg rst_n ;

reg [2:0] divider_num ;

wireout_clk;

initialbegin

rst_n= 1 ;

#10 rst_n= 0 ;

#10 rst_n= 1 ;

end

initialbegin

clk= 0 ;

forever#5 clk = ~clk ;

end

initialbegin

divider_num =1 ;

#300 divider_num=2 ;

#300 divider_num=3;

#300 divider_num=4 ;

#300 divider_num=5 ;

#300 divider_num=6 ;

#300 divider_num=7 ;

#300 divider_num=8 ;

end

divider divider(

.clk(clk) ,

.rst_n(rst_n) ,

.divider_num(divider_num) ,

.out_clk(out_clk)

);

endmodule

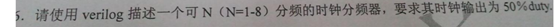

shift[2:0] = 3’b000 :output[7:0] = inp(0)_0_0_0_0_0_0_0

shift[2:0] = 3’b001 :output[7:0] = inp(1)_ inp(0)_0_0_0_0_0_0

shift[2:0] = 3’b010 :output[7:0] = inp(2)_ inp(1)_ inp(0)_0_0_0_0_0

shift[2:0] = 3’b011 :output[7:0] = inp(3)_ inp(2)_ inp(1)_ inp(0)_0_0_0_0

shift[2:0] = 3’b100 :output[7:0] = inp(4)_inp(3)_ inp(2)_ inp(1)_inp(0)_0_0_0

shift[2:0] = 3’b101 :output[7:0] = inp(5)_inp(4)_inp(3)_ inp(2)_inp(1)_ inp(0)_0_0

shift[2:0] = 3’b110 :output[7:0] = inp(6)_inp(5)_inp(4)_inp(3)_inp(2)_ inp(1)_ inp(0)_0

shift[2:0] = 3’b111 :output[7:0] = inp(7)_inp(6)_inp(5)_inp(4)_inp(3)_inp(2)_ inp(1)_ inp(0)

上述电路为纯组合逻辑,电路功能直接由真值表可以看出。

关于Verilog实现有很多种描述方式:

1、 根据得出的电路功能行为用行为级Verilog描述:

shift_mux.v

module shift_mux(

input [7:0] inp ,

input [2:0] shift,

output reg [7:0] outp

);

always@(*) begin

case(shift)

3'b000: assign outp ={inp[0],7'b000_0000} ;

3'b001: assign outp ={inp[1],inp[0],6'b00_0000} ;

3'b010: assign outp ={inp[2],inp[1],inp[0],5'b0_0000} ;

3'b011: assign outp ={inp[3],inp[2],inp[1],inp[0],4'b0000} ;

3'b100: assign outp ={inp[4],inp[3],inp[2],inp[1],inp[0],3'b000} ;

3'b101: assign outp ={inp[5],inp[4],inp[3],inp[2],inp[1],inp[0],2'b00} ;

3'b110: assign outp ={inp[6],inp[5],inp[4],inp[3],inp[2],inp[1],inp[0],1'b0} ;

3'b111: assign outp ={inp[7],inp[6],inp[5],inp[4],inp[3],inp[2],inp[1],inp[0]} ;

endcase

end

endmodule

shift_mux_tb.v

module shift_mux_tb;

reg [7:0] inp;

reg [2:0] shift;

wire [7:0] outp;

initialbegin

inp = 0 ;

shift = 0 ;

end

always#10 inp = $random%256 ;

always#10 shift = $random%8 ;

shift_muxshift_mux(

.inp(inp) ,

.shift(shift),

.outp(outp)

);

endmodule

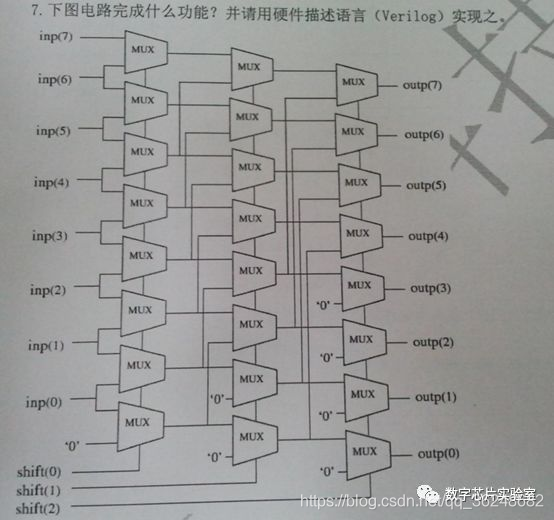

interface_change.v

module interface_change(

input clka ,

input wra_n,

input da ,

inputclkb ,

output [7:0] db ,

outputwrb

);

reg [7:0] data = 0 ;

always@(posedge clka) begin

if(!wra_n)begin

data<= {data[6:0],da} ;

end

end

reg wra_n_reg1 ,wra_n_reg2 ;

always@(posedge clkb ) begin

wra_n_reg1<= wra_n ;

wra_n_reg2<= wra_n_reg1 ;

end

wire wra_n_check ;

assign wra_n_check = wra_n_reg1&&(!wra_n_reg2) ;

assign wrb = wra_n_check ;

assign db = (wra_n_check == 1'b1) ? data :0 ;

endmodule

interface_change_tb .v

module interface_change_tb ;

reg clka ;

reg wra_n;

reg da ;

regclkb ;

wire[7:0] db ;

wirewrb ;

initial begin

clka = 0 ;

#3;

clkb = 0 ;

end

initial begin

wra_n= 1 ;

@(posedgeclka) wra_n = 0 ;

da= $random%2 ;

@(posedgeclka) wra_n = 0 ;

da= $random%2 ;

@(posedgeclka) wra_n = 0 ;

da= $random%2 ;

@(posedgeclka) wra_n = 0 ;

da= $random%2 ;

@(posedgeclka) wra_n = 0 ;

da= $random%2 ;

@(posedgeclka) wra_n = 0 ;

da= $random%2 ;

@(posedgeclka) wra_n = 0 ;

da= $random%2 ;

@(posedgeclka) wra_n = 0 ;

da= $random%2 ;

@(posedgeclka) wra_n = 1;

end

always #5 clka = ~clka ;

always #10 clkb = ~clkb ;

interface_change interface_change (

.clka(clka) ,

.wra_n(wra_n),

.da(da) ,

.clkb(clkb),

.db(db),

.wrb(wrb)

);

endmodule