几块钱几分钟打造100MHz采样率逻辑分析仪

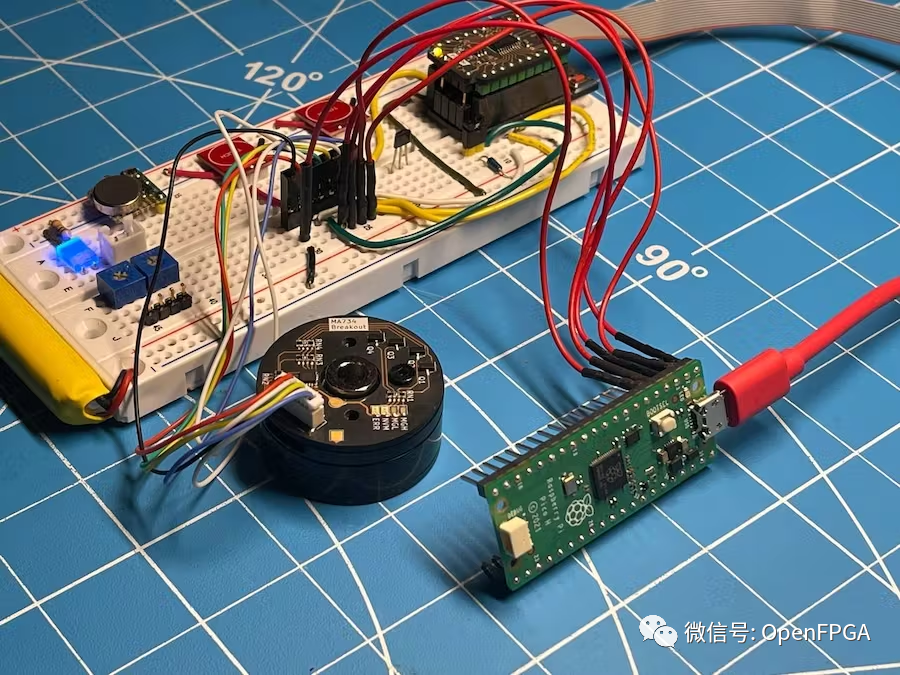

5 分钟内将 Raspberry Pi Pico(或任何 RP2040 板)变成简单的逻辑分析仪。

介绍

逻辑分析仪是一种电子仪器,可捕获并显示来自数字系统或数字电路的多个信号。逻辑分析仪可以将捕获的数据转换为时序图、协议解码、状态机跟踪、操作码,或者可以将操作码与源级软件相关联。逻辑分析仪具有先进的触发功能,当用户需要查看数字系统中许多信号之间的时序关系时,逻辑分析仪非常有用。

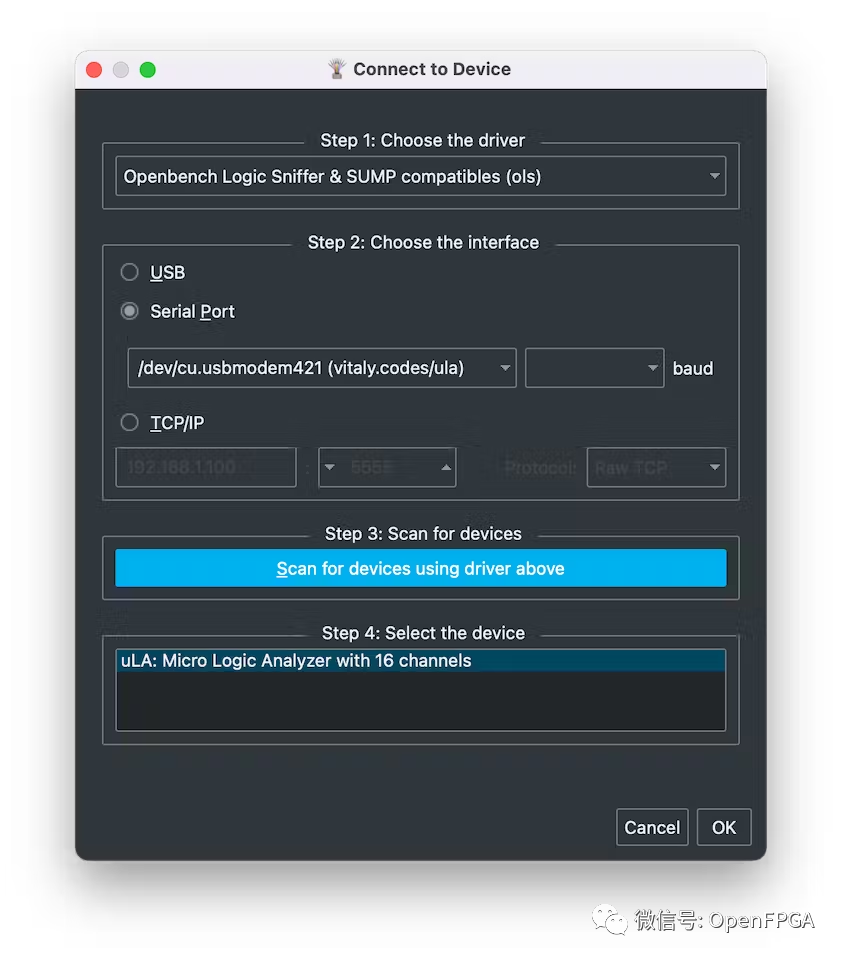

μLA 是 SUMP/OLS 兼容逻辑分析仪固件,适用于基于 RP2040 的板卡。

特征

16个通道

100 MHz 采样率(优化得当(超频)后为 250 MHz),每个系统时钟周期采集 1 个样本

200 KB 内存

使用 PIO 快速触发

支持的硬件

树莓派 Pico

RP2040-zero

所有基于 RP2040 的板卡(需具有 USB 连接)

安装

从下方链接下载最新的 µLA 固件

扫描二维码关注公众号,回复: 17249795 查看本文章

https://github.com/dotcypress/ula/releases

将开发板连接到计算机时按住 BOOTSEL 按钮

将之前下载的固件文件复制到 RP2040

使用 PulseView 或 sigrok-cli 进行上位机采集分析

https://sigrok.org/wiki/PulseView

https://sigrok.org/wiki/Sigrok-cli

享受

代码

https://github.com/dotcypress/ula

https://sigrok.org/wiki/PulseView

https://sigrok.org/wiki/Sigrok-cli