半加器功能:完成两个一位二进制数的加法,不考虑进位输入。

真值表 逻辑图

半加器的Verilog描述

module h_adder (A,B,SO,CO);

input A,B;

output SO,CO;

assign SO=A ^ B;

assign CO=A & B;

endmodule

测试程序

module test_bjq;

reg A,B;

wire SO,CO;

h_adder h_adder1(A,B,SO,CO);

initial//只在仿真开始时执行一次,只能用于测试程序

begin

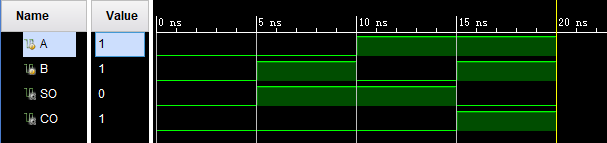

#0 A = 1'b0; B = 1'b0;

#5 A = 1'b0; B = 1'b1;

#5 A = 1'b1; B = 1'b0;

#5 A = 1'b1; B = 1'b1;

#5 $finish;

end

initial

$monitor("At time %t, A(%b) + B(%b) = SO(%b),CO(%b)",$time, A, B, SO, CO);

initial

begin

$dumpfile("test.vcd");

$dumpvars(0,test_bjq);

end

endmodule仿真结果