计算机结构 (★)

运算器:

- 算术逻辑单元ALU:数据的算术运算和逻辑运算

- 累加寄存器AC:通用寄存器,为ALU提供一个工作区,用于暂存数据

- 数据缓冲寄存器DR:写内存时,暂存指令或数据

- 状态条件寄存器PSW:存状态标志与控制标志(争议:也有将其归为控制器的)

控制器:

- 程序计数器PC:存储下一条要执行指令的地址

- 指令寄存器IR:存储即将执行的指令

- 指令译码器ID:对指令中的操作码字段进行分析解释

- 时序部件:提供时序控制信号

冯•诺依曼结构

冯•诺依曼结构也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一

起的存储器结构。

特点:

(1) 一般用于PC处理器,如13, 15, 17处理器

(2) 指令与数据存储器合并在一起

(3) 指令与数据都通过相同的数据总线传输

哈佛结构

哈佛结构是一种将程序指令存储和数据存储分开的存储器结构。哈佛结构是一种并

行体系结构,它的主要特点是将程序和数据存储在不同的存储空间中,即程序存储

器和数据存储器是两个独立的存储器,每个存储器独立编址、独立访问。

特点:

(1) —般用于嵌入式系统处理器 (DSP) 数字信号处理 (DSP, Digital Signal Processing)

(2) 指令与数据分开存储,可以并行读取,有较高数据的吞吐率

(3) 有4条总线:指令和数据的数据总线与地址总线

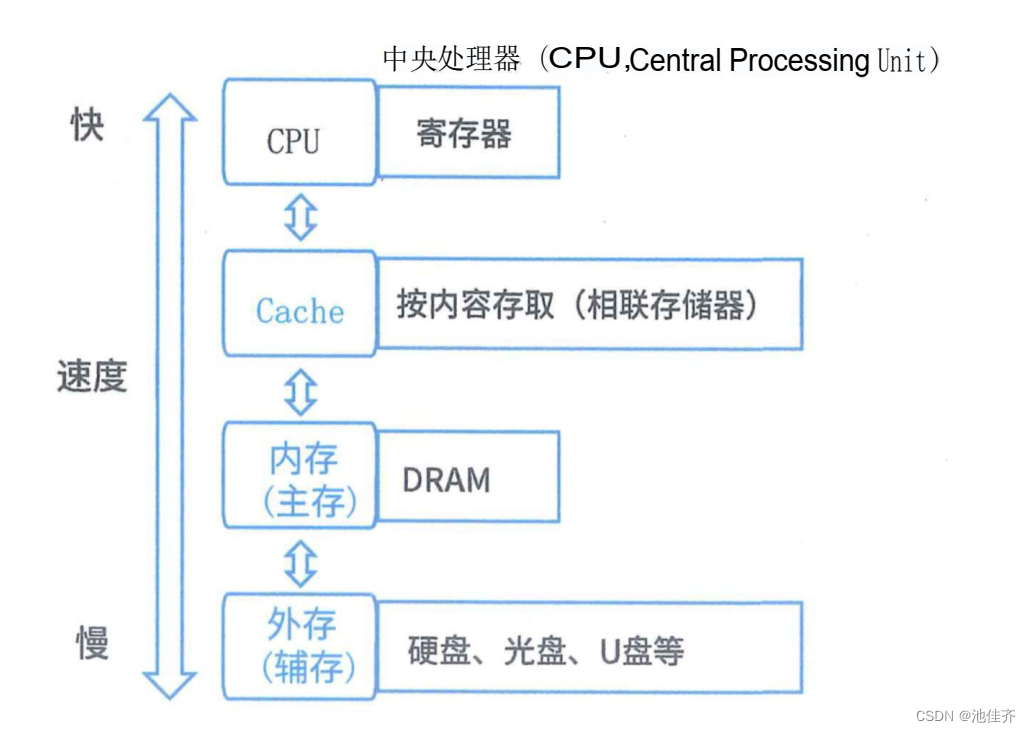

存储系统(★★★★)

Cache:

Cache的功能:提高CPU数据输入输出的速率,突破冯•诺依曼瓶颈,即CPU与存储系统间数据传送带宽限制。

- 在计算机的存储系统体系中,Cache是访问速度最快的层次。

- Cache对程序员来说是透明的。

- 使用Cache改善系统性能的依据是程序的局部性原理。

时间局部性:指程序中的某条指令一旦执行,不久以后该指令可能再次执行,典型原因是由于程序中存在着大量的循环操作。

空间局部性:指一旦程序访问了某个存储单元,不久以后,其附近的存储单元也将被访问,即程序在一段时间内所访问的地址可能集中在一定的范围内,其典型情况是程序顺序执行。

如果以h代表对Cache的访问命中率,t1表示Cache的周期时间,t2表示主存储器周期时间,以读操作为例,使用 “Cache+主存储器” 的系统的平均周期为t3, 则:

t3 = h * t1 + (1 - h) * t2

其中, (1 - h) 又称为失效率 (未命中率) 。

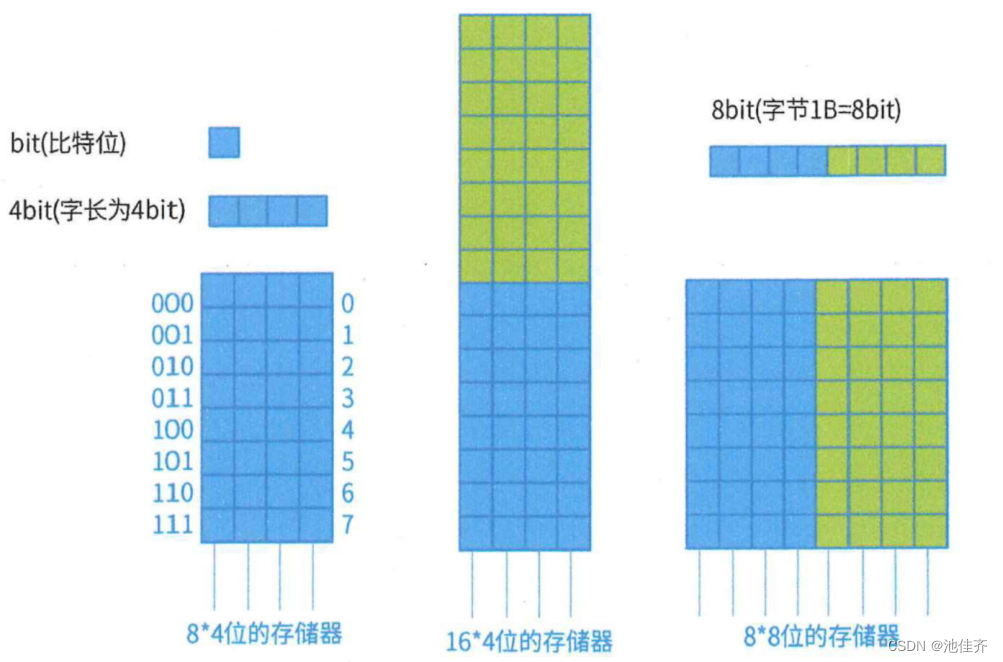

主存编址

存储单元个数 = 最大地址 - 最小地址 + 1

编址内容

按字编址:存储体的存储单元是字存储单元,即最小寻址单位是一个字

按字节编址:存储体的存储单元是字节存储单元,即最小寻址单位是一个字节。

总容量 = 存储单元个数*编址内容

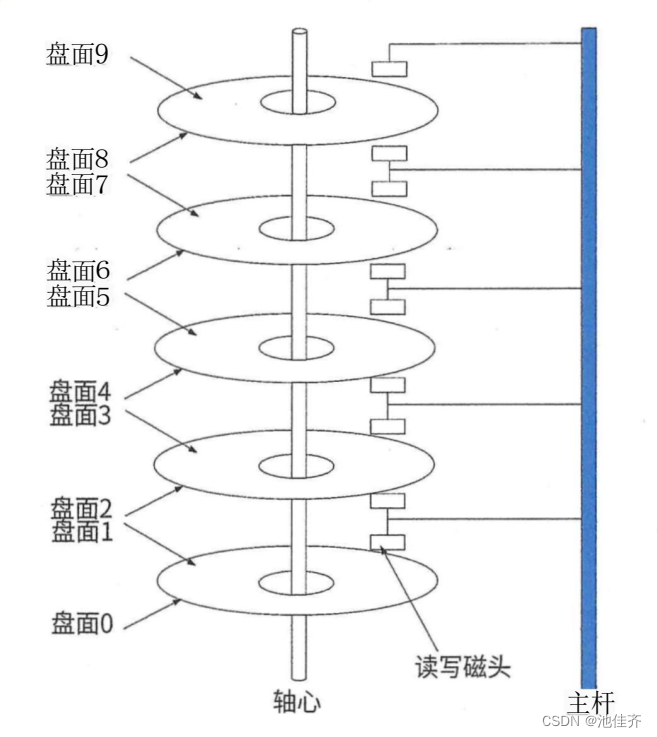

磁盘管理

存取时间 = 寻道时间+等待时间,寻道时间是指磁头移动到磁道所需的时间;等待时间为等待读写的扇区转到磁头下方所用的时间。

读取磁盘数据的时间应包括以下三个部分:

- (1) 找磁道的时间。

- (2) 找块 (扇区) 的时间,即旋转延迟时间。

- (3) 传输时间。

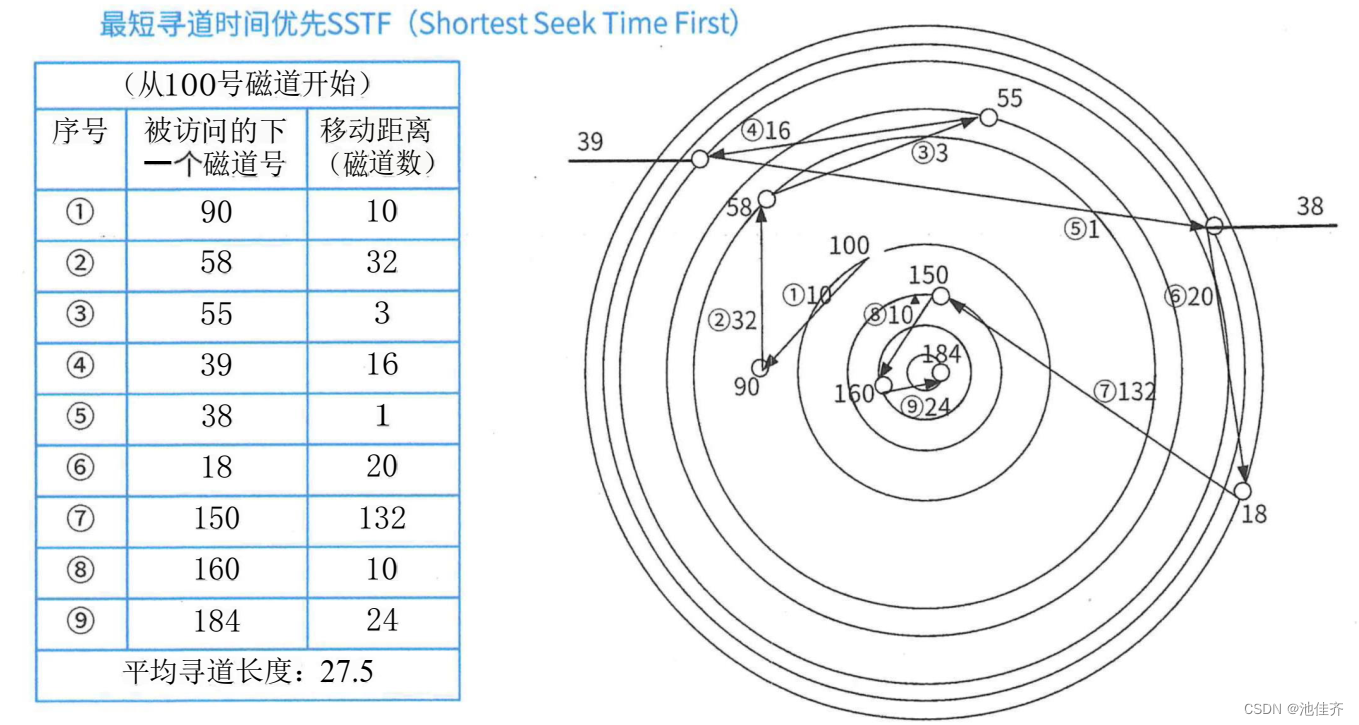

磁盘调度算法:

- 先来先服务FCFS(First-Come,First Served)

- 最短寻道时间优先 (SSTF)

- 扫描算法 (SCAN)

- 循环扫描 (CSCAN) 算法

数据传输控制方式 (★)

程序控制(查询)方式:分为无条件传送和程序查询方式两种。方法简单,硬件开销小,但I/O能力不高,严重影响CPU的利用率。

程序中断方式:与程序控制方式相比,中断方式因为CPU无需等待而提高了传输请求的响应速度。

DMA方式:DMA方式是为了在主存与外设之间实现高速、批量数据交换而设置的。DMA方式比程序控制方式与中断方式都高效。

DMAC向总线裁决逻辑提出总线请求;CPU执行完当前总线周期即可释放总线控制权。此时DMA响应,通过DMAC通知I/O接口开始DMA传输。

总线(★★)

一条总线同一时刻仅允许一个设备发送,但允许多个设备接收。所以总线是半双工模式

半双工与全双工

串行总线与并行总线

总线功能来划分

数据总线 (Data Bus, DB) :在CPU与RAM之间来回传送需要处理或是需要储存的数据。

地址总线 (AddressBus, AB) : 用来指定在RAM (Random AccessMemory) 之中储存的数据的地址。

控制总线 (Control Bus, CB) :将微处理器控制单元 (Control Unit) 的信号,传送到周边设备。

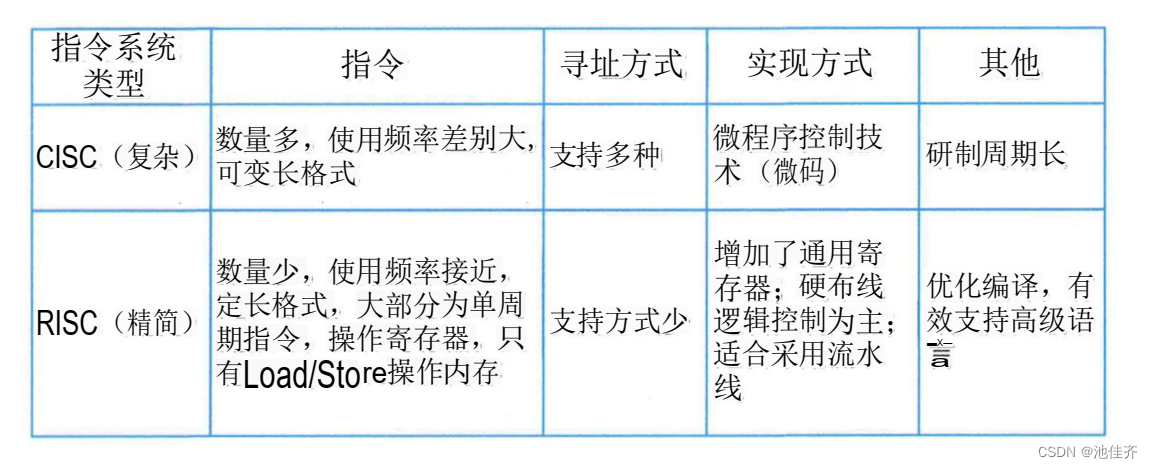

CISC与RISC (★)

复杂指令集计算机 (CISC, Complex Instruction Set Computers)

精简指令集计算机 (RISC, Reduced Instruction Set Computers)

流水线(★★)

相关参数计算:流水线执行时间计算、流水线吞吐率、流水线加速比等。

Rs 流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理是针对不同指令而言的,它们可同时为多条指令的不同部分进行工作,以提高各部件的利用率和指令的平均执行速度。

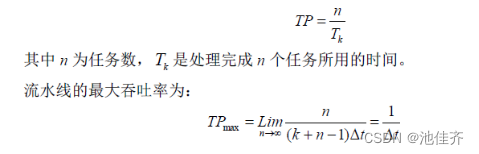

流水线的吞吐率 (ThoughPut rate, TP) 是指在单位时间内流水线所完成的任务数量或输出的结果数量。计算流水线吞吐率的最基本的公式如下:

TP = 指令条数TD / 流水线执行时间

流水线最大吞吐率:

加速比(speedup ratio): 不使用流水线所用的时间与使用流水线所用的时间之比称为流水线的加速比(speedup ratio)。

顺序执行所用的时间为 T0 ,使用流水线的执行时间为 Tk

校验码 (★)

奇偶校验码

由若干位有效信息 (如一个字节),再加上一个二进制位 (校验位) 组成校验码。

奇校验:整个校验码 (有效信息位和校验位) 中 “1”的个数为奇数。

偶校验:整个校验码 (有效信息位和校验位) 中 “1”的个数为偶数。

奇偶校验,可检查1位的错误,不可纠错。

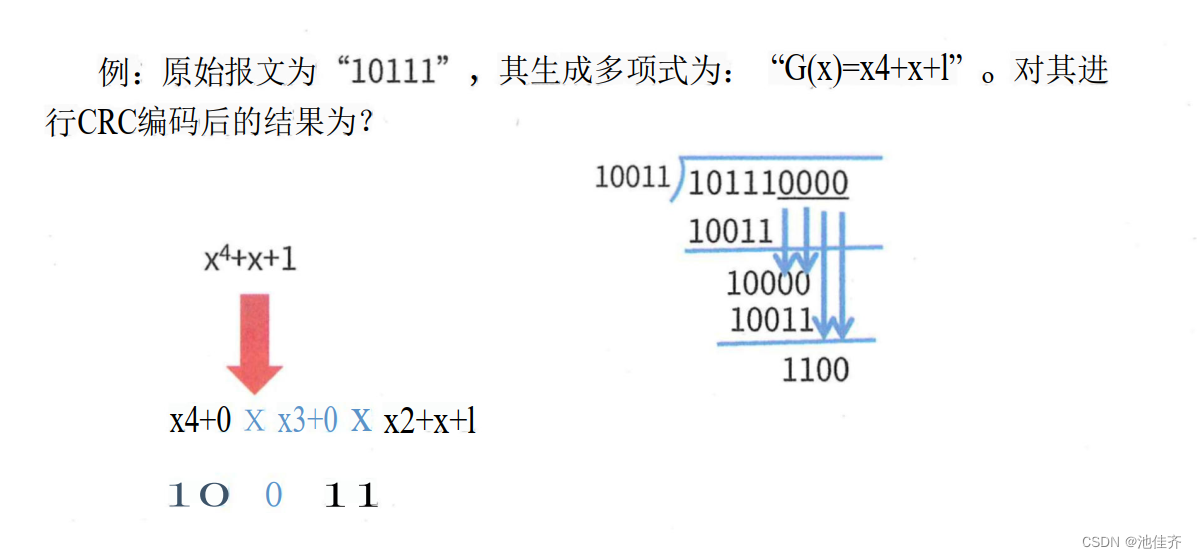

循环冗余校验 (CRC, Cyclic Redundancy Check)

CRC的编码方法是:在k位信息码之后拼接r位校验码。应用CRC码的关键是如何从k位信息位简便地得到r位校验位 (编码),以及如何从k+r位信息码判断是否出错。

循环冗余校验码编码规律如下:

除数:10011

被除数:100111+ 0000 (4个0即多项式最高次)

把接收到的CRC码用约定的生成多项式G(X)去除,如果正确,则余数为0;如果某一位出错,

则余数不为0。不同的位数出错其余数不同,余数和出错位序号之间有唯一的对应关系。

嵌入式 (★)

1、DSP

DSP芯片,也称数字信号处理器,是一种特别适合于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理算法。

2、SoC

System on Chip, 简称SoC, 也即片上系统。从狭义角度讲,它是信息系统核心的芯片集成,是将系统关键部件集成在一块芯片上;从广义角度讲, SoC是一个微小型系统,如果说中央处理器 (CPU) 是大脑,那么SoC就是包括大脑、心脏、眼睛和手的系统。

3、MPU

微机中的中央处理器 (CPU) 称为微处理器 (MPU) ,是构成微机的核心部件,也可以说是微机的心脏。它起到控制整个微型计算机工作的作用,产生控制信号对相应的部件进行控制,并执行相应的操作。

4、MCU

微控制单元 (Microcontroller Unit;MCU) , 又称单片微型计算机 (Single Chip Microcomputer) 或者单片机,是旭中央处理器 (CentralProcess Unit;CPU) 的频率与规格做适当缩减,并将内存 (memory) 、计数器 (Timer) 、USB、A/D转换、UART、PLC、DMA等周边接口,甚至LCD驱动电路都整合在单一芯片上,形成芯片级的计算机,为不同的应用场合做不同组合控制。