和高速ADC对应,高速DAC被广泛使用在波形产生,测试设备及无线基础设施中,当代高速DAC的制造是基于亚微米CMOS或BiCMOS的工艺,已经达到了一个全新的性能水准,实现了1GSPS的刷新率以及14位,甚至16位的分辨率。为了达到如此高的刷新率和分辨率,DAC采用了一种带分段(segmented)电流源的电流导引型(current steering)架构。

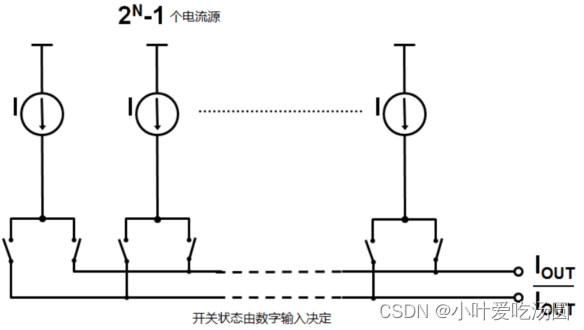

此类单片电路DAC的核心单元是电流源阵列(array),其设计用于输送出满刻度输出电流,典型值为20mA。内置的解码器在每次DAC刷新的时刻驱动(addresses)差分电流开关。如上图所示,该电流源阵列有两个电流输出,两路输出互补,使得输出的电流总量为一个恒定值。数字输入导引源自各个电流源的电流,输出到相应信号输出电流的差分输出端。相较于电压输出,这种方法可以保证更高的速度。

在此采用差分信号是为了改善动态性能,同时降低负载电阻上承载的输出电压的摆动。理想情况下,此类信号电压摆幅是越小越好,以确保DAC有最适宜的线性度。此信号电压的上限,以及相关的负载电阻,通过输出电压所遵循的规格实现定义。分段电流引导架构的意义在于降低了电路复杂性,并因此降低了杂散脉冲的能量。这些,都从整体上改善了DAC的线性度及交流性能。作为一种全新的系统架构,其高刷新率和卓越的动态性能,使得其输出频率的合成能力达到百兆赫兹的范围,而这种方式通常被称为“直接中频”。