用TLC5620芯片,TLC5620内部有4个DAC,全部都是8位电压输出型。每个DAC有一个高输入阻抗的参考电压输入端口,每个DAC可以输出一倍或者两倍的参考电压与GND之间的电压值。

TLC5620接受11位数据,2位的DAC选择位,8位的数据位,1位的电压倍增控制位。

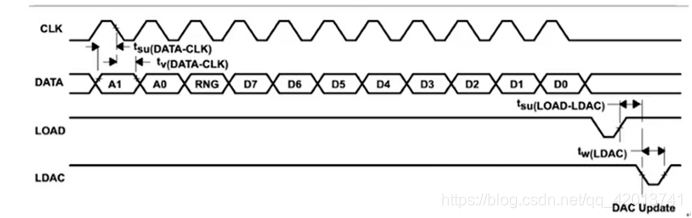

先有load控制将信号存储到latch中,再由ldac控制,将存储的信号交由DAC输出。clk是位串行接口时钟,每个时钟的下降沿,输入数字总线上的数据被移入内部的接口寄存器中。只有当ldac由高电平变为低电平时,数据才会跟新到DAC上。当ldac为低电平时,load的下降沿将带输出数据所存到输出锁存器并立即产生输出电压。每个DAC通道的输出可由下列公式计算得出:

Vo(DAC|A|B|C|D)=REFCODE/256(1+RNG bit value)

两种输出方式如下:

A0A1两位指定了被选中的DAC,00为DACA,01为DACB,10为DACC,11为DACD。

芯片手册如上,我使用的学习板中提供的参考电压为3.42V。我们只需要在逻辑中使用计数器来计数,然后每个计数值相当于一个时间点,各个信号需要进行什么样的操作直接赋值即可。因为系统时钟为50M所以时钟周期为20ns,但是时序参数中最小值为50ns,所以使用60ns来代替。

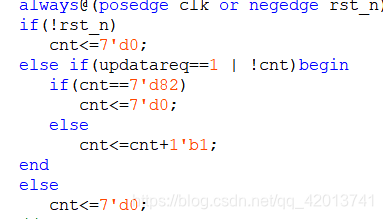

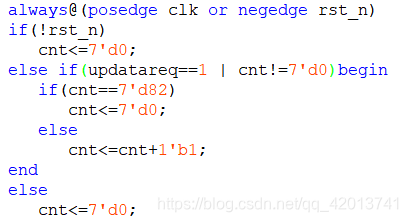

按照时间线,需要一个计数器计数到82即可,这里编写一个计数器。

按照时间线,需要一个计数器计数到82即可,这里编写一个计数器。

按照时间线编写DAC代码即可

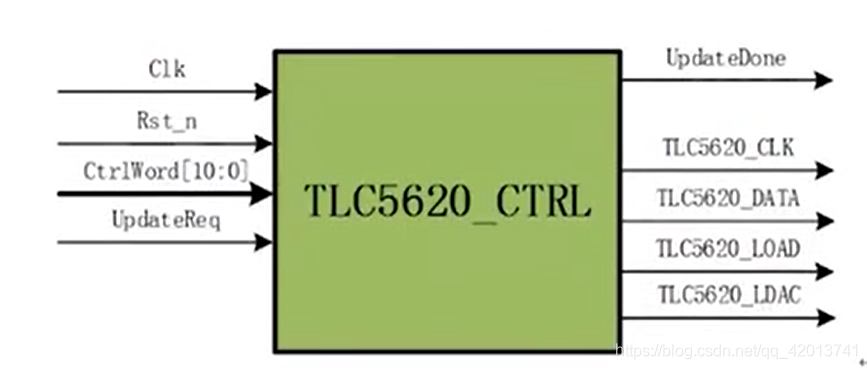

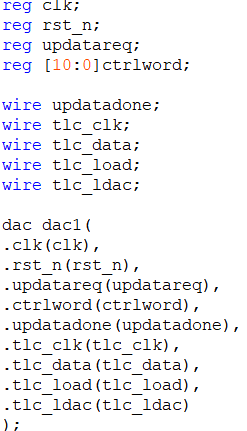

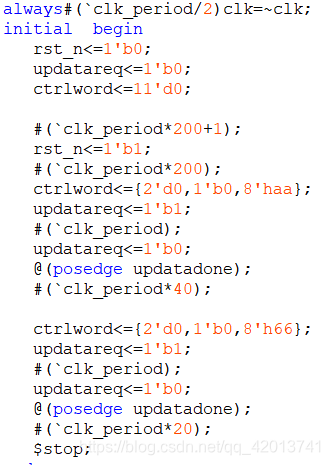

之后编写testbench进行测试,先对寄存器进行连接。

之后编写testbench进行测试,先对寄存器进行连接。

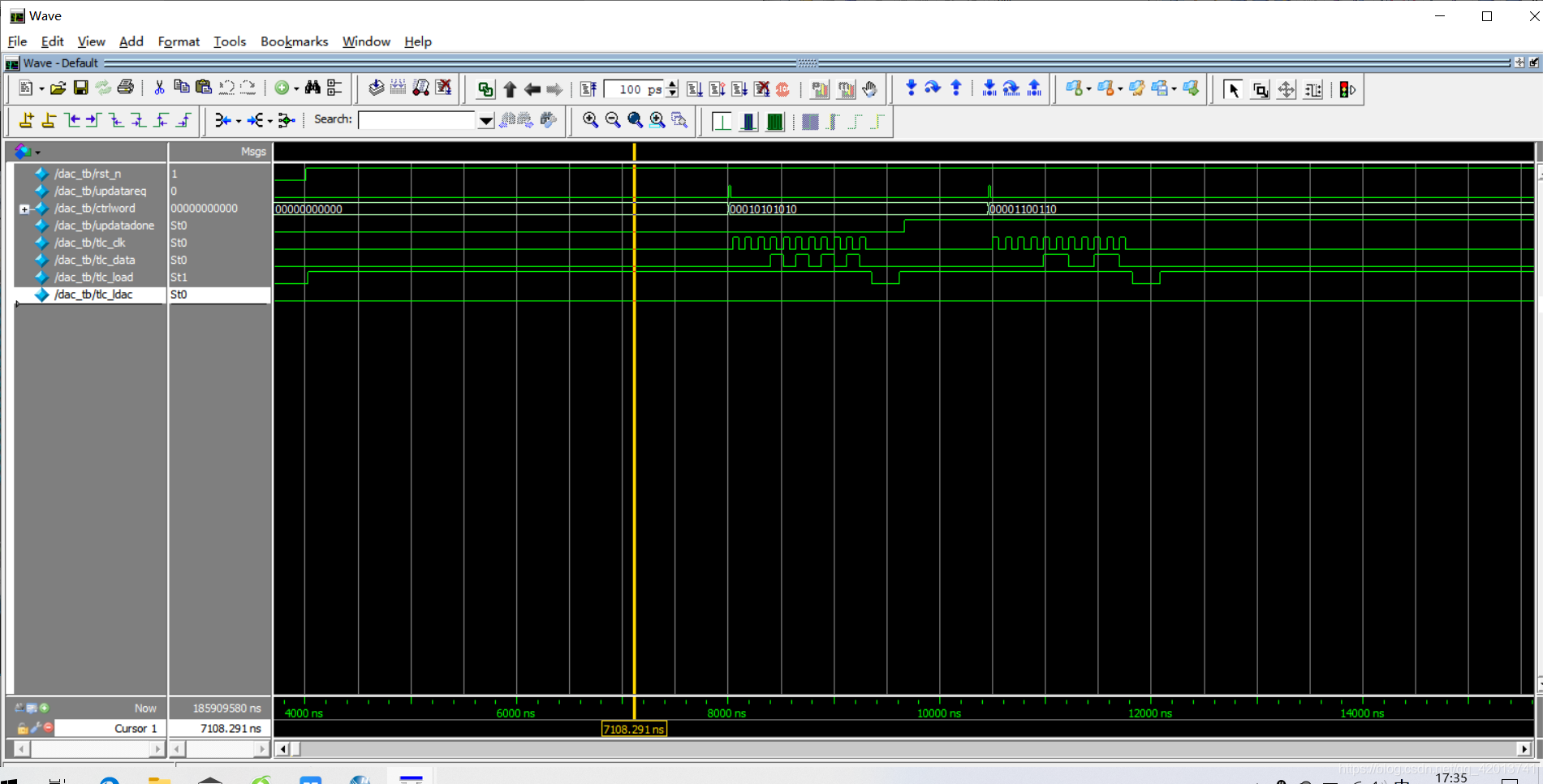

简单的编写驱动进行测试,看仿真波形。

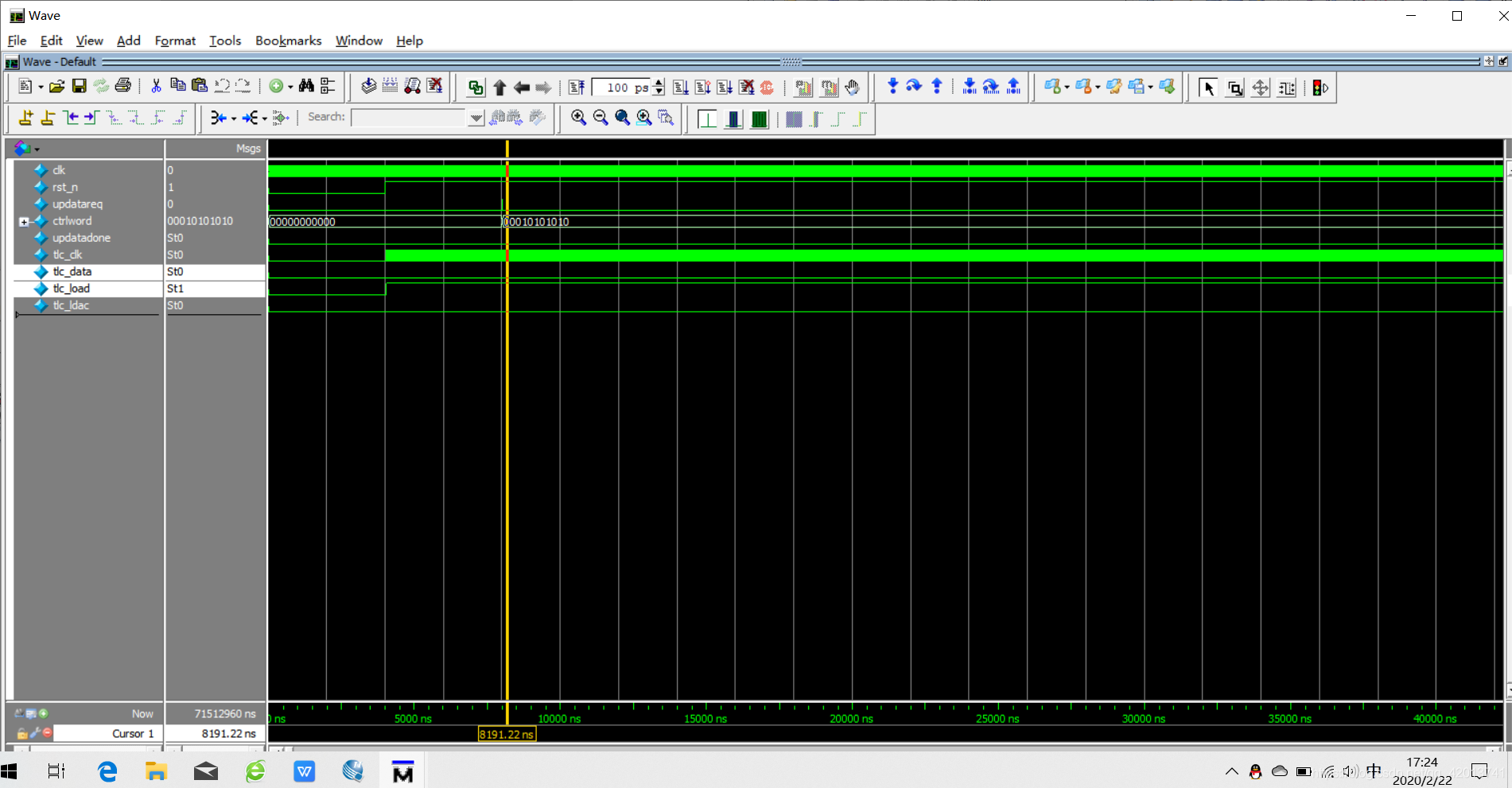

发现没有出现预期效果。

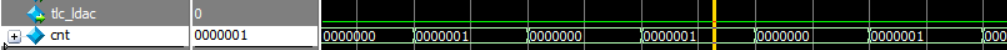

这里看到,最然产生了tlc_clk,但是没有与updatareq同步,回去查代码。发现cnt一直在0,1之间变化。

改后代码为

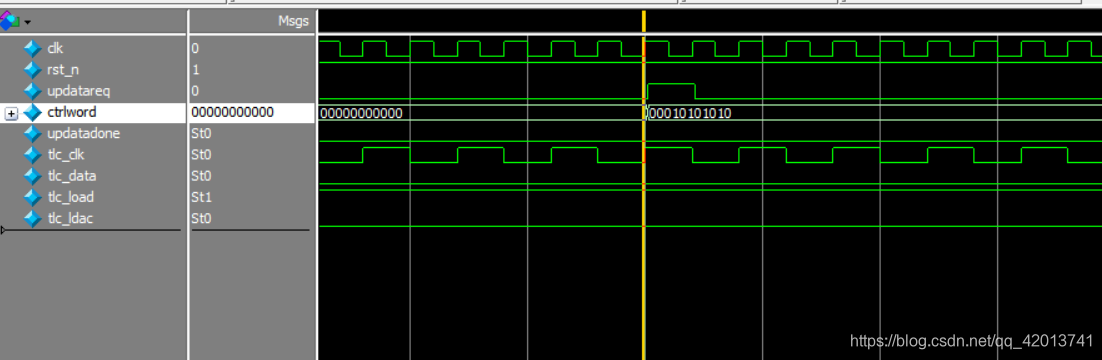

再次进行仿真

与预计波形相同,在管教约束时,把data约束到硬件口即可。

基于FPGA的dac控制

猜你喜欢

转载自blog.csdn.net/qq_42013741/article/details/104443956

今日推荐

周排行